FPGA入门

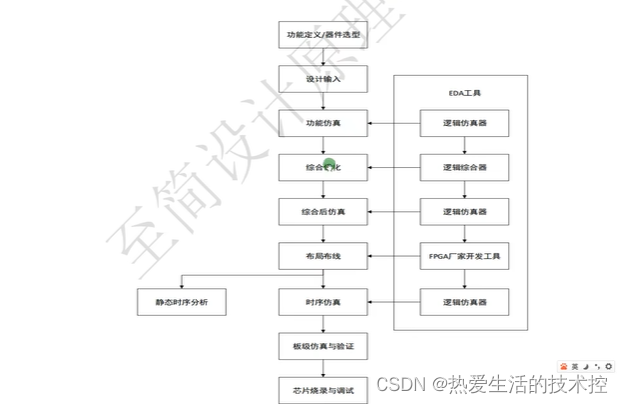

EDA软件

可以编程A,B,C的关系

第三章 硬件描述语言 verilog

HDL硬件描述语言

语言——》原理图——》实现

语言-》综合器-》电路

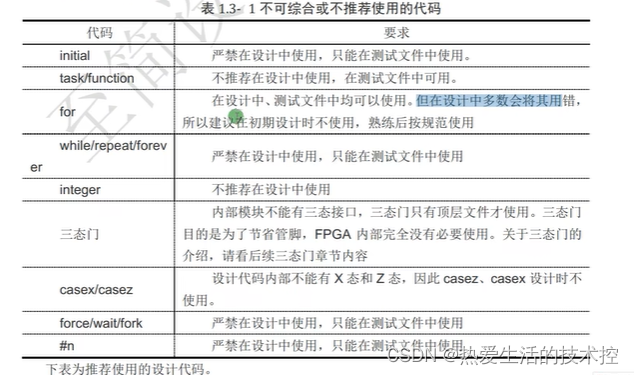

测试文件;使用激励

不可综合语法:不能在电路实现

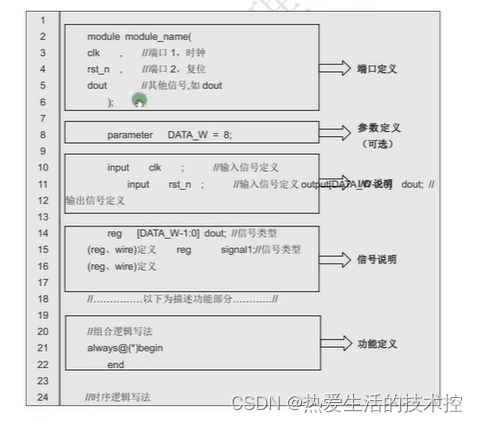

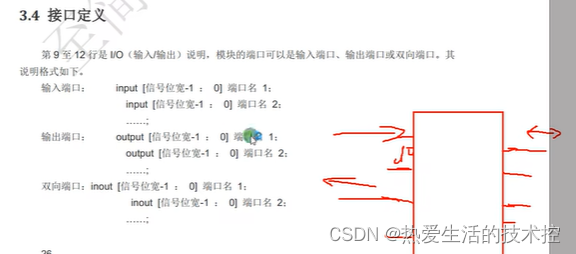

3节 模块结构

模块类似函数(自顶向下)

模块;

模块类:{

接口名

参数定义:

输入管脚

输出管脚

信号类型定义

功能描述:

}

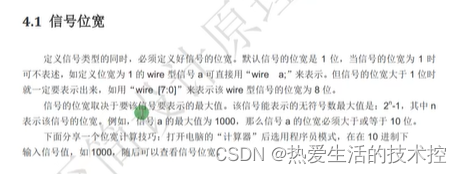

4节 信号类型

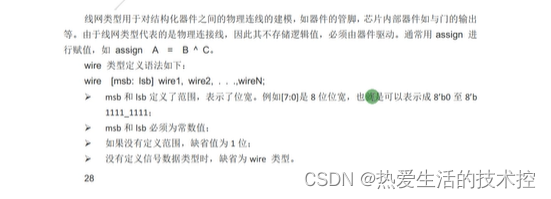

线网类型:net type wire

寄存器类型; reg type reg

4.2

用于结构化器件之间的物理连线的建模

assign a= A ^B

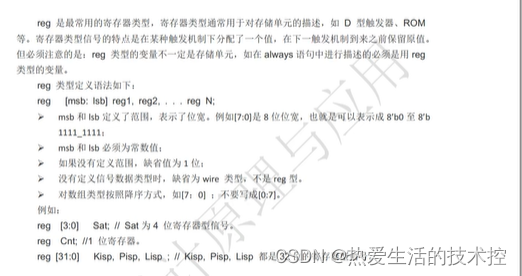

4.3 寄存器类型 reg

4.4 寄存器类型与线性类型区别

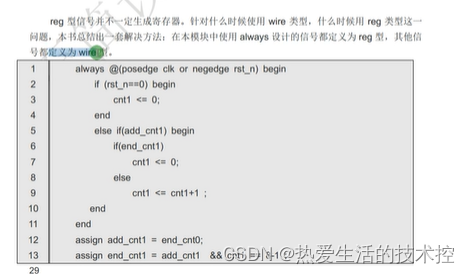

reg型信号并不一定生成寄存器。针对什么时候使用wire类型,什么时候用reg类型这一

问题,本转总结出一能解决方法:在本模块中使用always设计的信号都定义为reg型,其他信

号都定义为wire型。

5节 程序语句

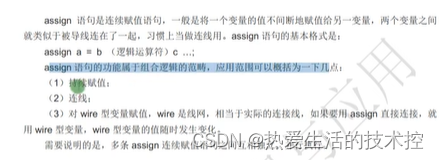

5.1.1 寄存器类型与线性类型区别

assign :类似·1连线

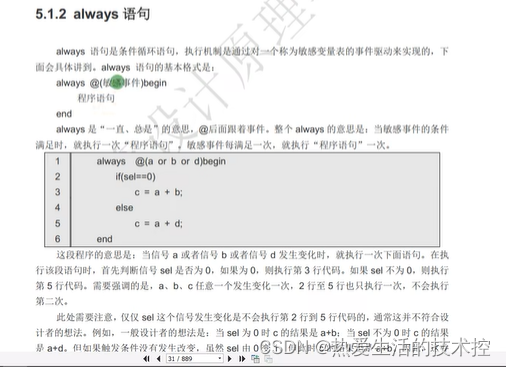

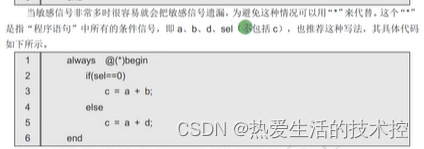

5.1.2 always条件循环

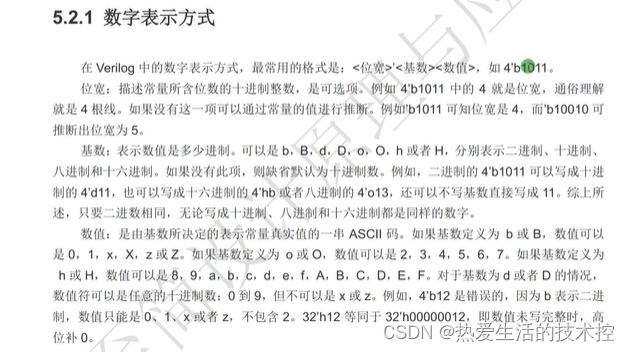

5.2节 数字进制

5.1.2 数字表示方式

<位宽><基数><数值>

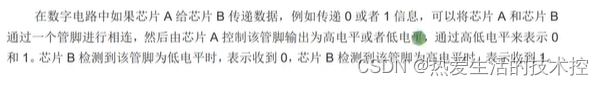

5.2.2 二进制是基础

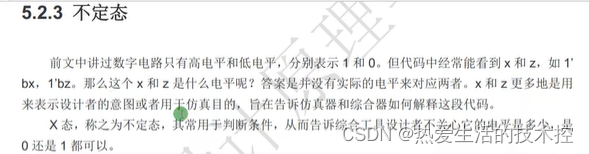

5.2.3 不定态

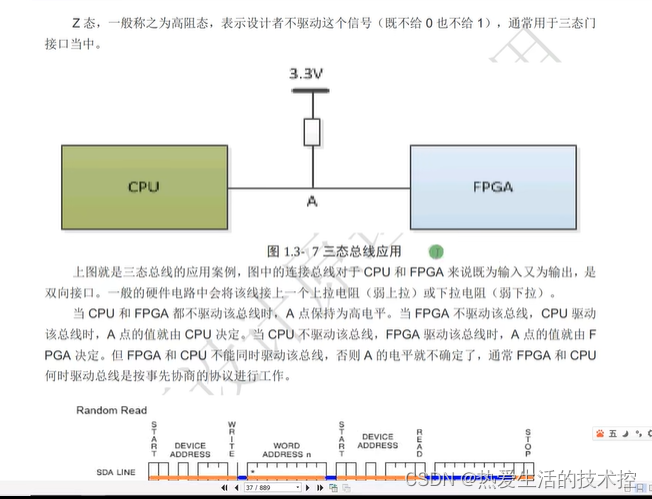

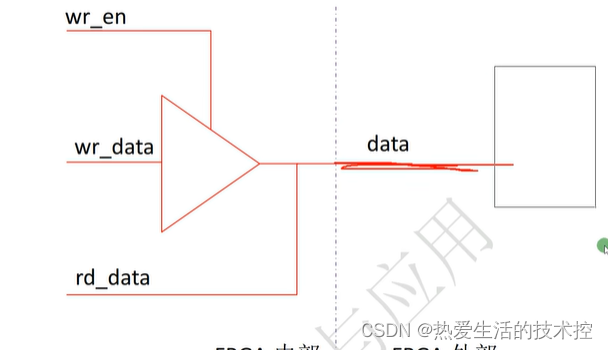

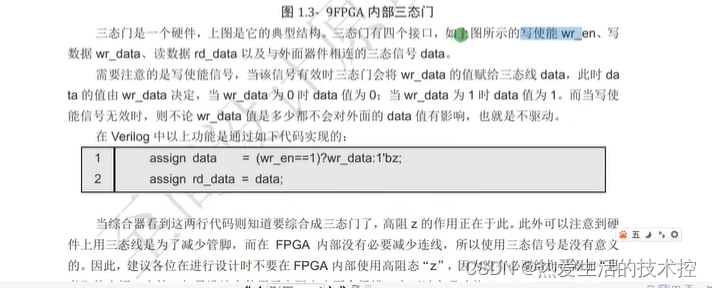

5.2.4 高阻态

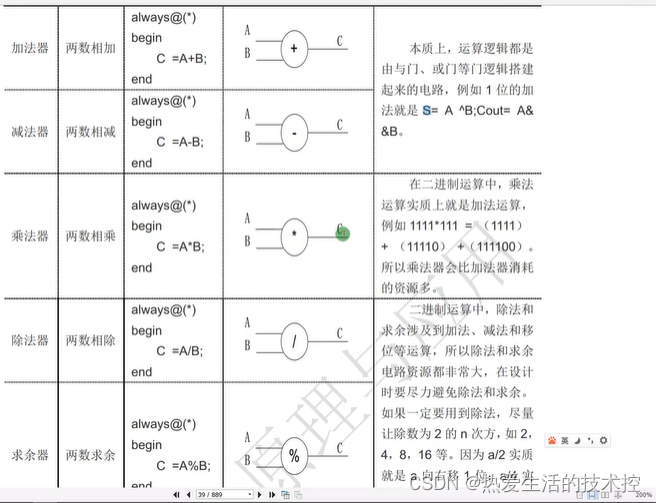

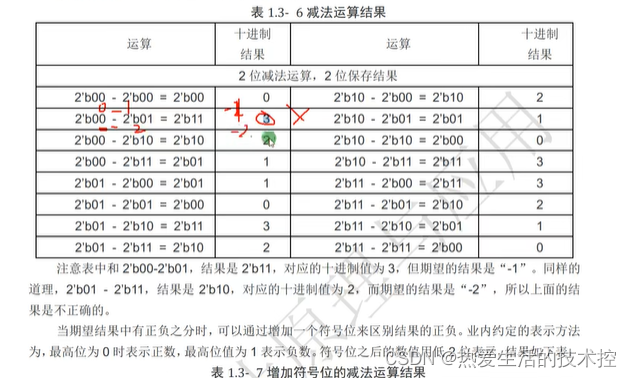

5.3节 数学运算符

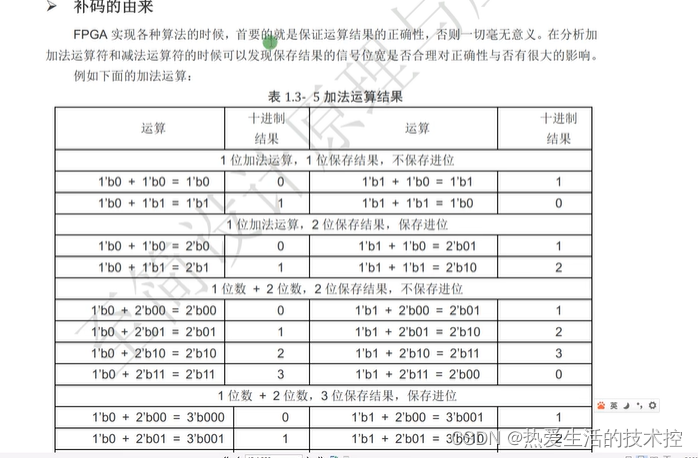

5.3.1节 加法运算符

5.3.5节 经验总结

“1”默认32位

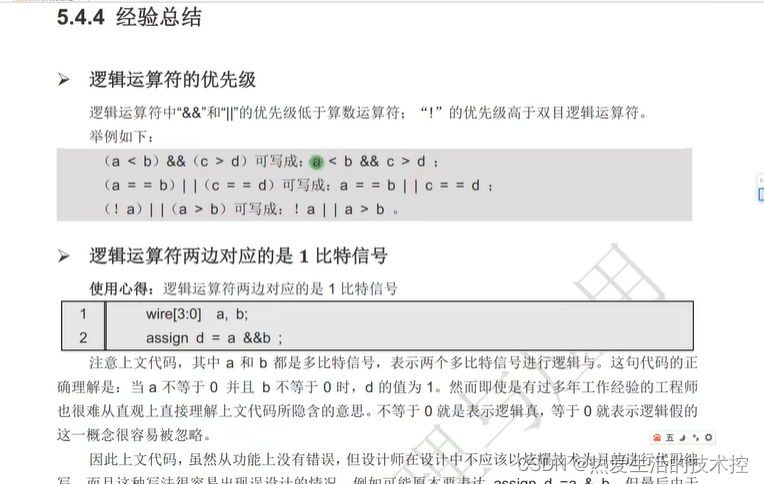

5.4.4节 经验总结

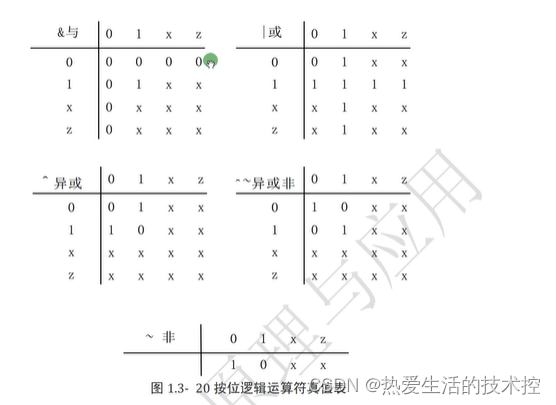

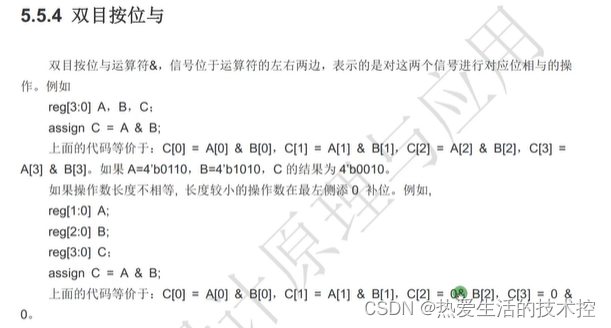

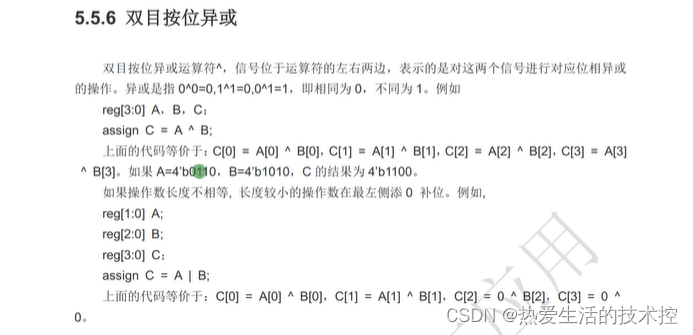

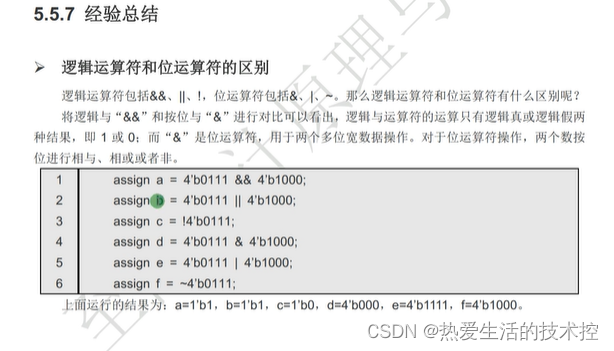

5.5 按位运算符

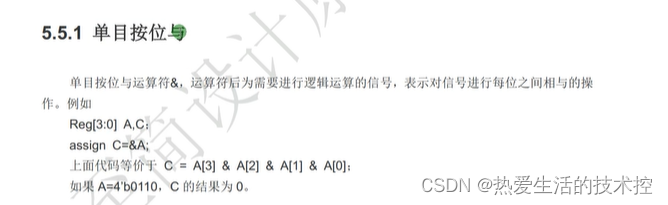

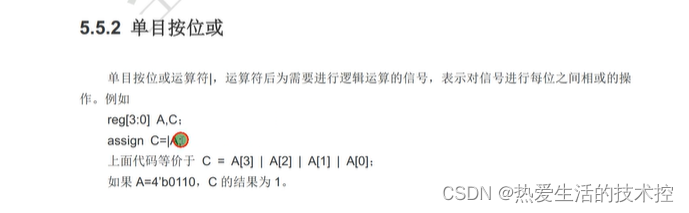

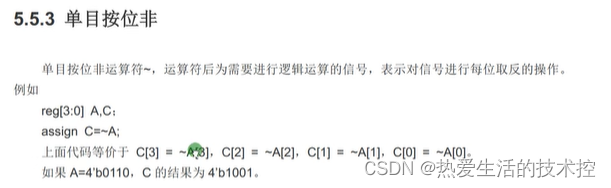

5.5.1 单位按位与

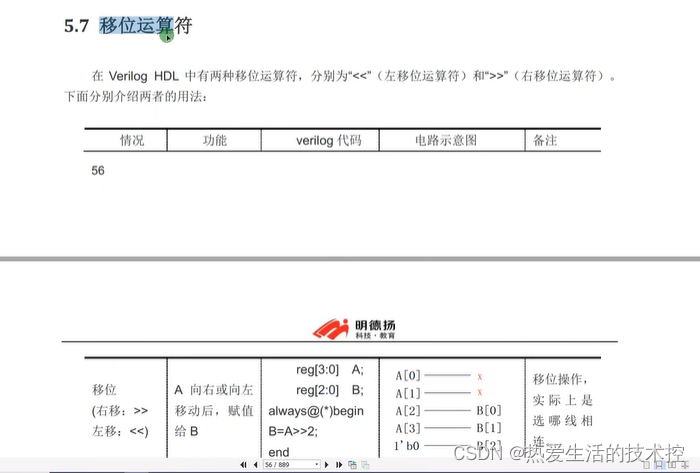

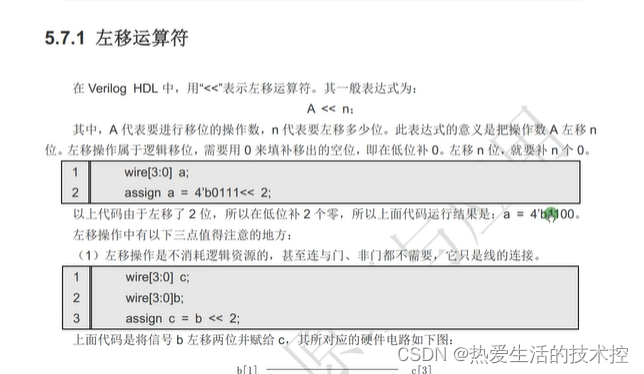

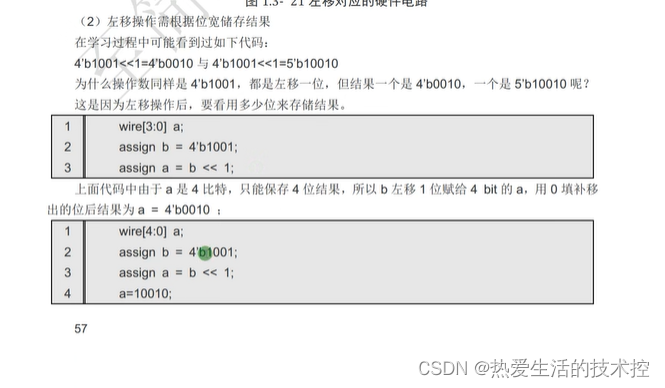

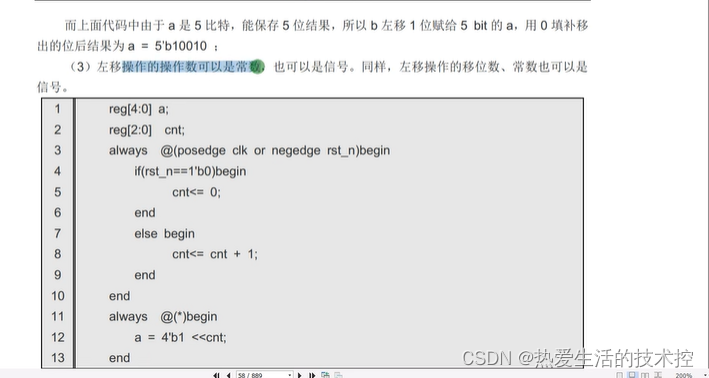

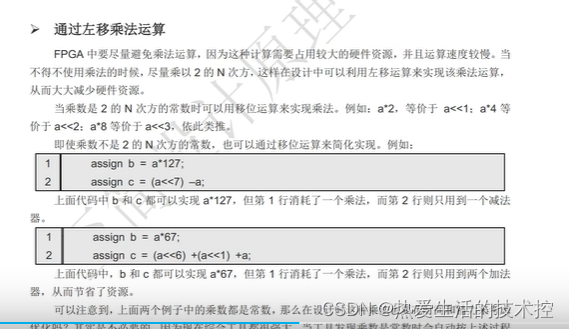

5.7 移位符

5.7.1 移位符

5.7.3 经验总结

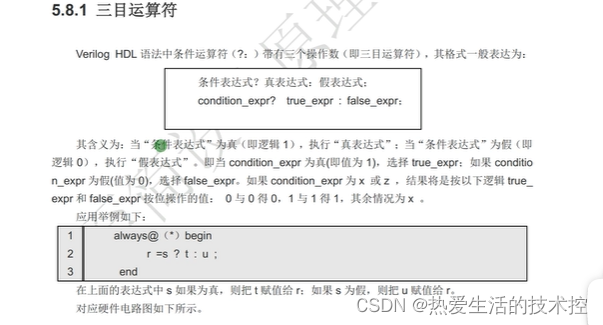

5.8 条件运算符

5.8.1 三目运算符

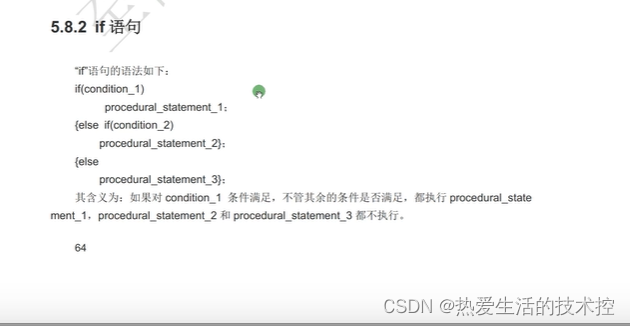

5.8.2 if语句

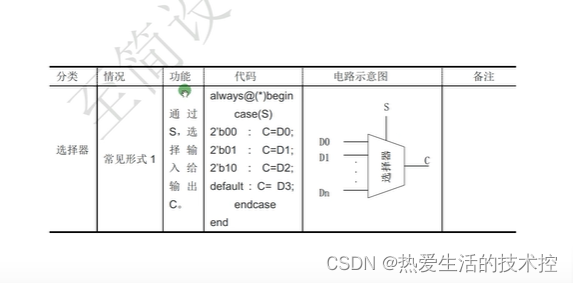

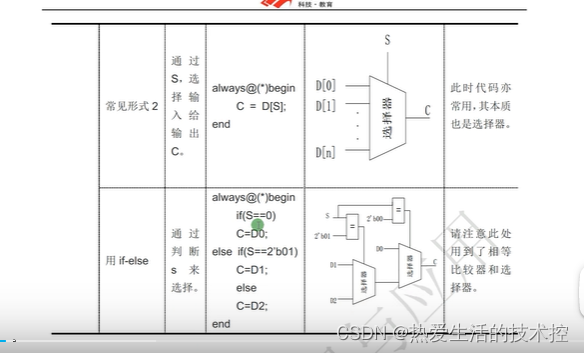

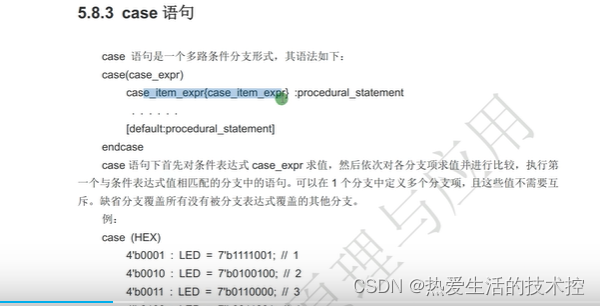

5.8.3 case语句

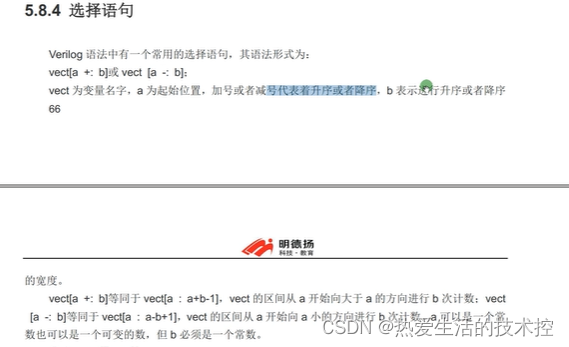

5.8.4 选择语句

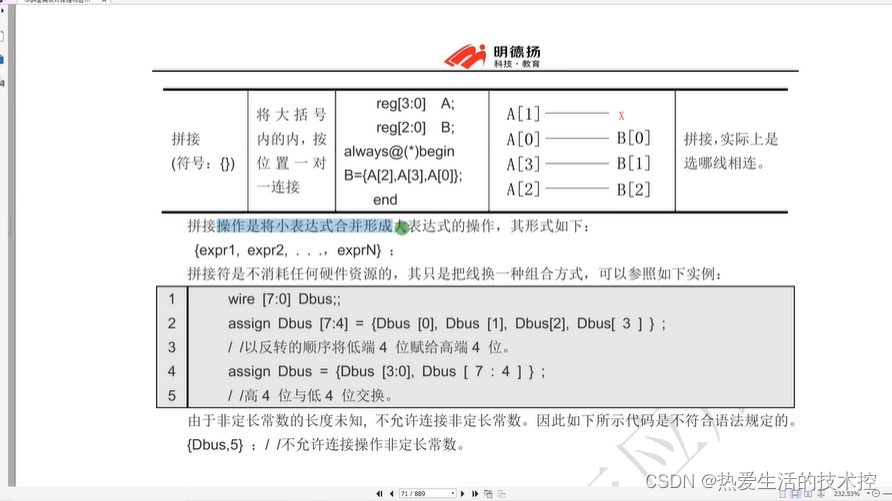

5.8.5 拼接运算符

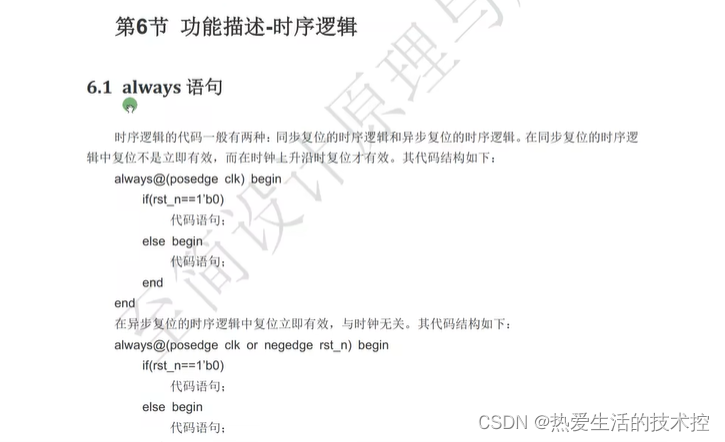

6节 功能描述-时序逻辑

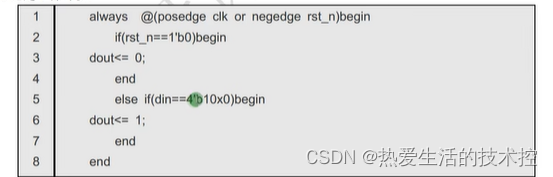

6.1 always语句

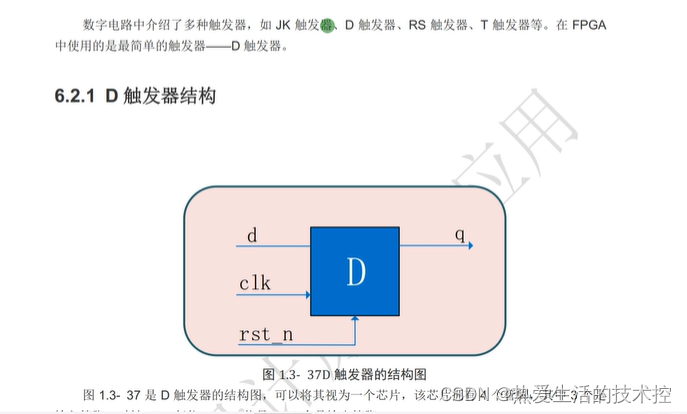

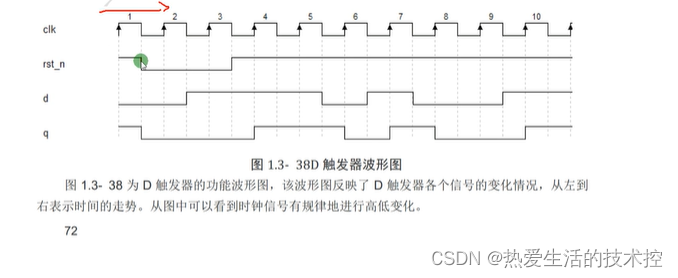

6.2 D触发器

图1.3- 37是D触发器的结构图,可以将其视为一一个芯片,该芯片拥有4个管脚,其中3个是输入管脚:时钟clk、复位rst n.信号d:1个是输出管脚: q。

该芯片的功能如下:当给管脚rst n给低电平(复位有效),即赋值为0时,输出管脚q处于低电平状态。如果管脚rst _n 为高电平,则观察管脚clk 的状态,当clk信号由0变1即处于上升沿的时候,将此时d的值赋给q。若d是低电平,则q也是低电平:若d是高电平,则q也是高电平。

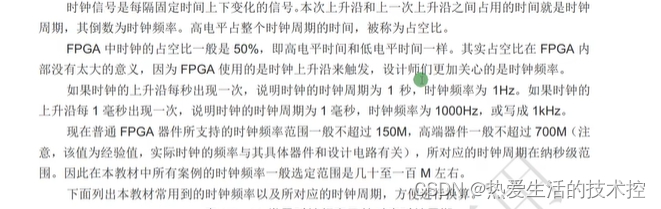

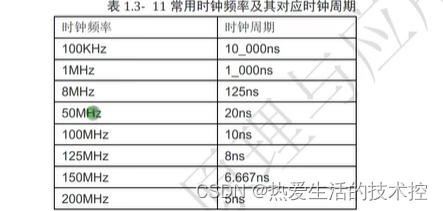

6.3 时钟

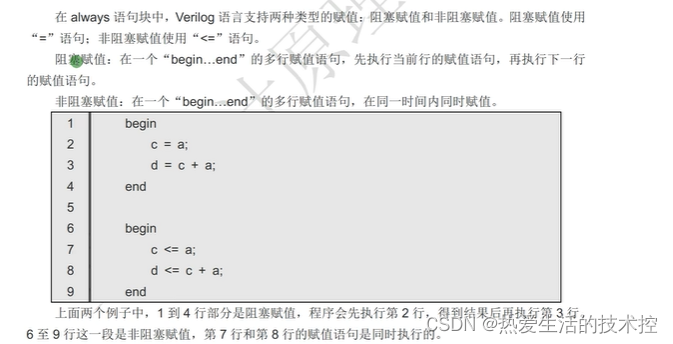

6.3 阻塞赋值和非阻塞赋值

6596

6596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?