随着摩尔定律的不断推进,芯片的集成度越来越高,性能要求也日益严苛。在这样的背景下,静态时序分析(STA)成为了确保芯片设计满足时序要求的关键技术。STA通过分析电路设计,预测电路性能,确保数据信号能够在规定的时间内准确无误地传输。这一过程对于提高芯片的可靠性和性能至关重要。

然而,对于许多刚步入芯片设计领域的工程师来说,STA的概念、原理和实际应用可能会显得有些抽象和复杂。此外,随着设计规模的扩大和时钟频率的提高,STA的复杂性也在不断增加。在这篇文章中,将移知移知公开课《静态时序分析的核心》,为大家揭开STA的神秘面纱。

想观看公开课视频完整版,可联系小编领取

公开课内容将从STA的基本概念入手,逐步深入到setup/hold时间的检查原理与计算方法,以及noise的产生与修复策略。这些内容不仅涵盖了STA的核心理论,还包含了实际设计中的痛点和解决方案。通过这篇文章,我希望能够为那些渴望深入了解STA的工程师们提供一个清晰的学习路径。

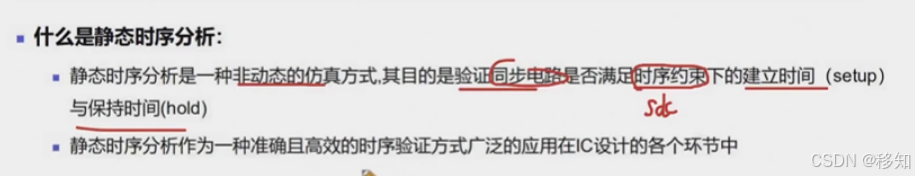

1. 静态时序分析简介

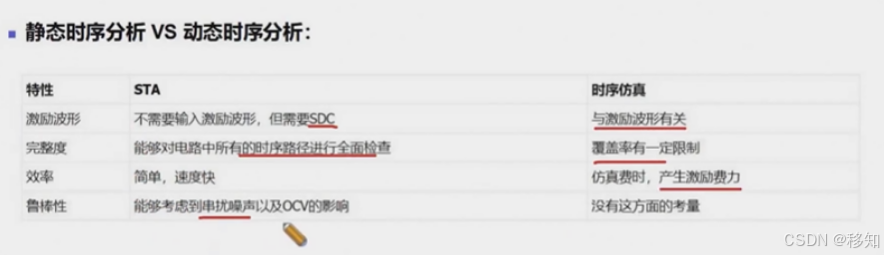

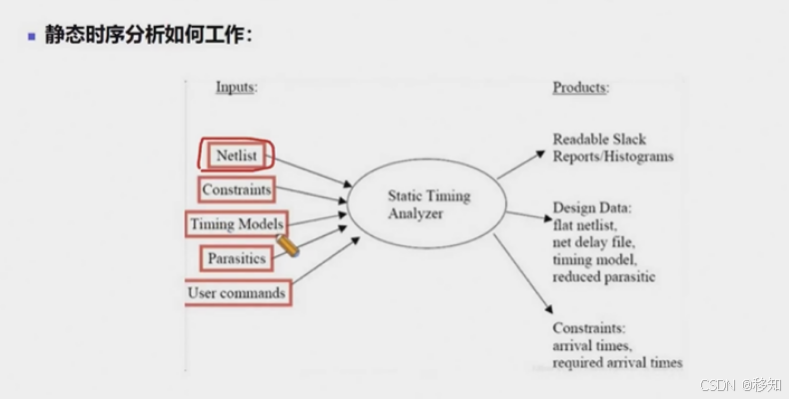

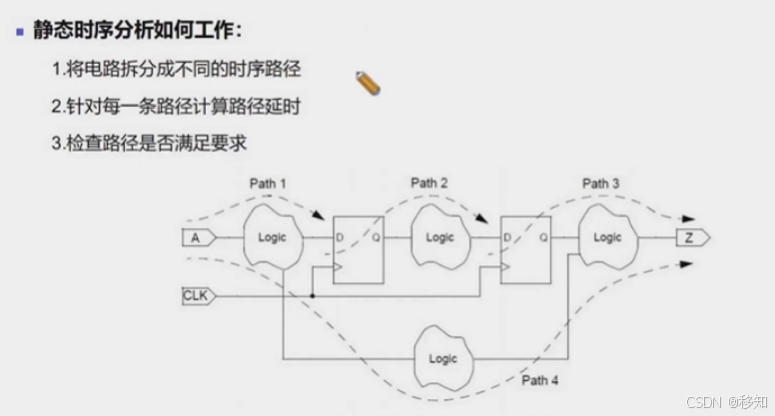

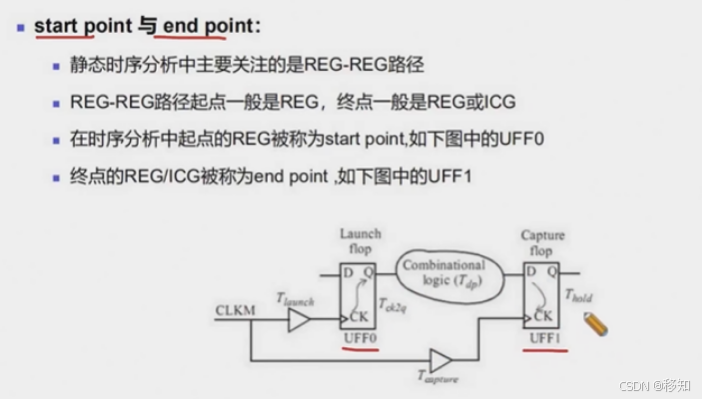

静态时序分析,简称STA,是一种在不模拟电路运行的情况下,通过分析电路设计来预测电路性能的方法。它主要关注电路中的时序问题,比如数据信号是否能够在规定的时间内到达目的地,以及是否能满足电路的时序要求。

STA的目的是验证设计是否满足所有的时序约束,包括建立时间(Setup Time)和保持时间(Hold Time)。这些约束通常在设计初期就被定义,并在设计过程中不断被验证和优化。

2. Setup/Hold检查原理与计算方法

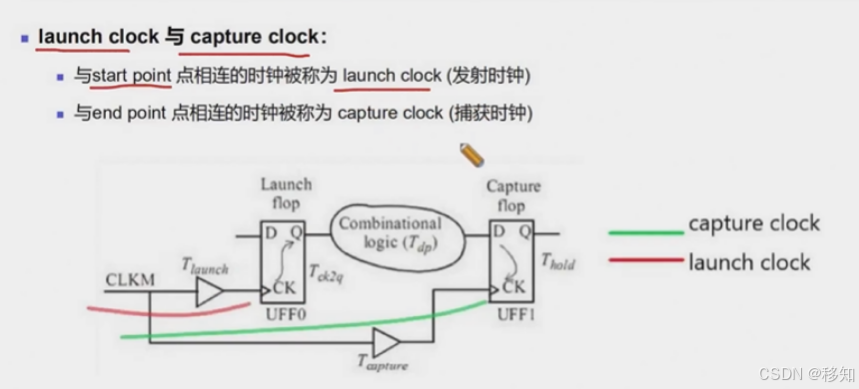

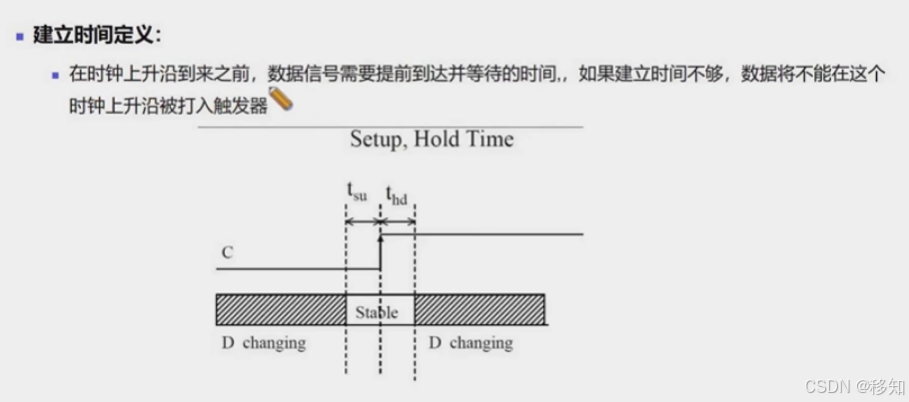

在STA中,Setup和Hold时间是两个核心概念,它们分别描述了数据信号在时钟信号前后的稳定时间要求。

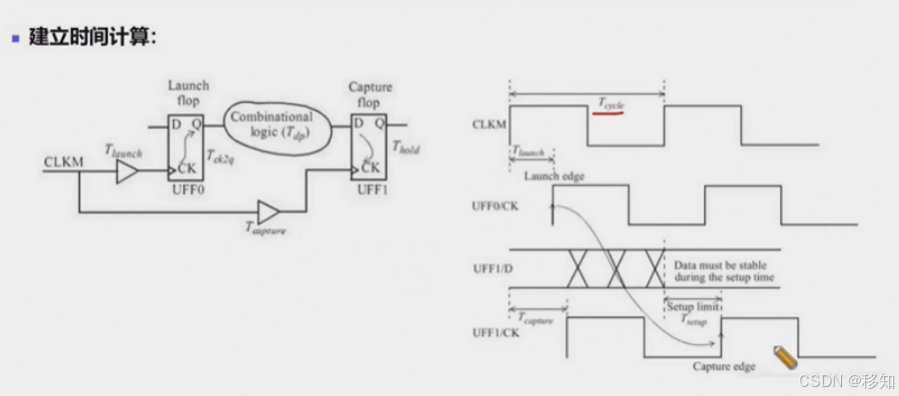

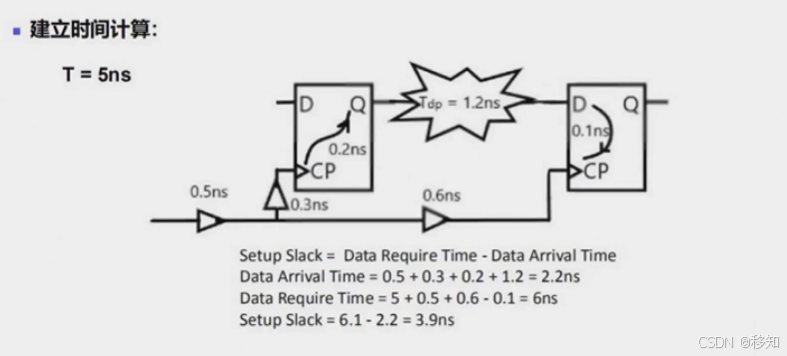

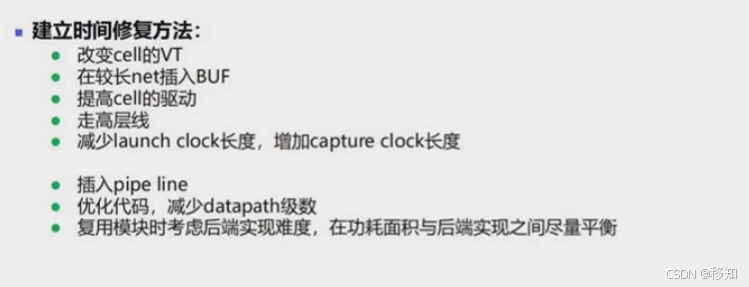

**Setup Time:**指的是在时钟边沿到来之前,数据信号需要在触发器的输入端稳定的时间。如果数据信号在时钟边沿到来之前没有足够的时间稳定,就会导致Setup时间违规。

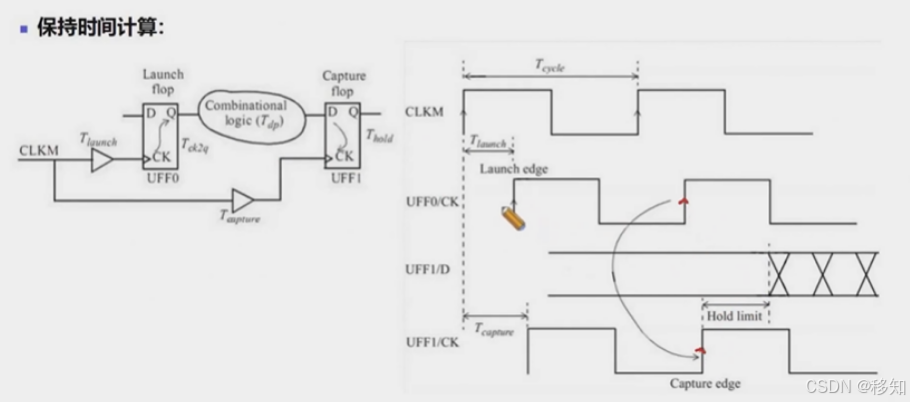

**Hold Time:**指的是在时钟边沿到来之后,数据信号需要在触发器的输入端保持稳定的时间。如果数据信号在时钟边沿到来之后过早变化,就会导致Hold时间违规。

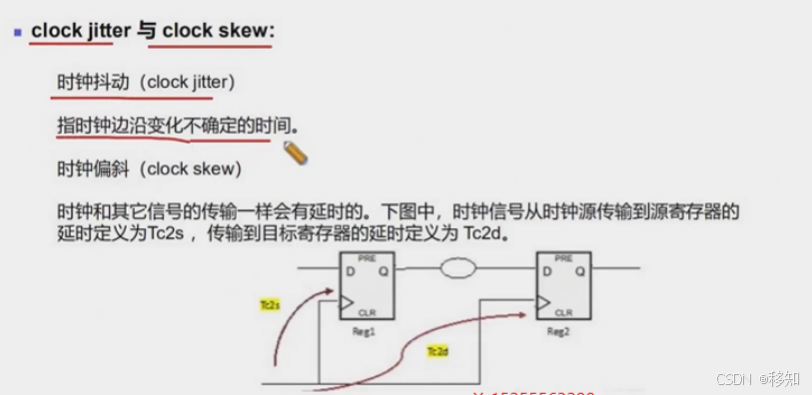

计算Setup和Hold时间需要考虑多个因素,包括时钟周期、时钟偏斜、时钟抖动等。这些计算通常由专业的STA工具完成,但了解背后的原理对于设计工程师来说至关重要。

3. Noise的产生与修复

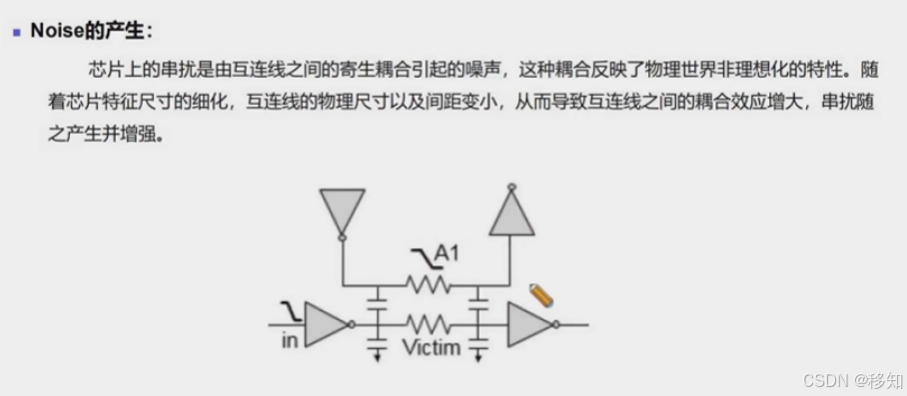

在高速电路设计中,Noise(噪声)是一个不可忽视的问题。噪声的产生通常与电路中的串扰(Crosstalk)有关,当两条信号线距离过近时,它们之间的互电容会导致信号互相干扰。

噪声对电路的影响主要体现在以下几个方面:

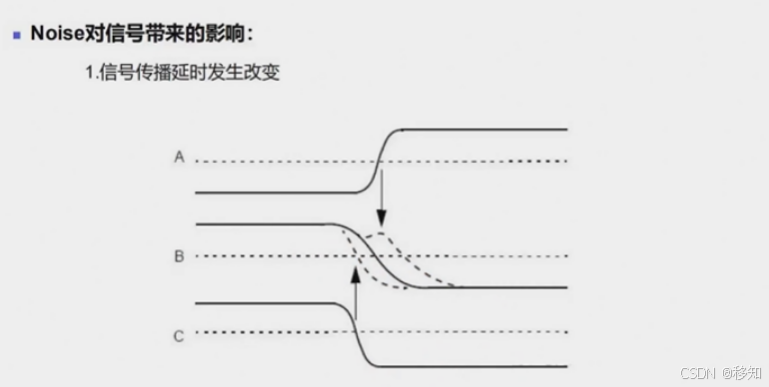

信号传播延迟变化:噪声可能导致信号传播延迟的变化,影响电路的时序性能。

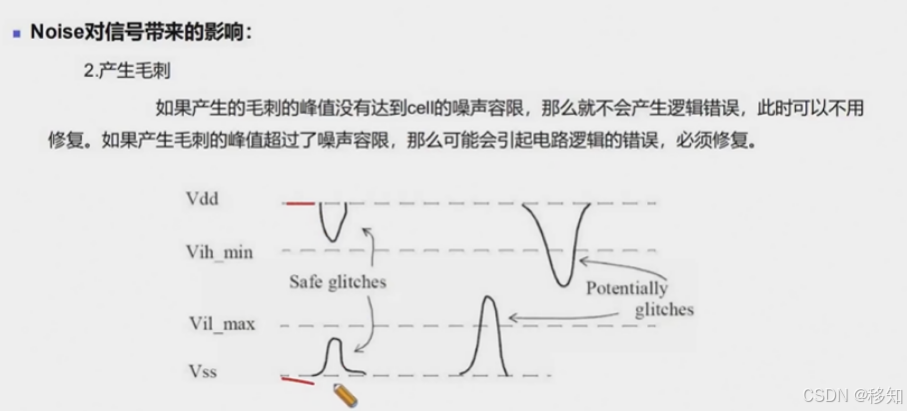

产生毛刺:噪声可能导致信号线上产生毛刺,这些毛刺如果超过一定的阈值,就可能被电路错误地解释为有效的信号变化。

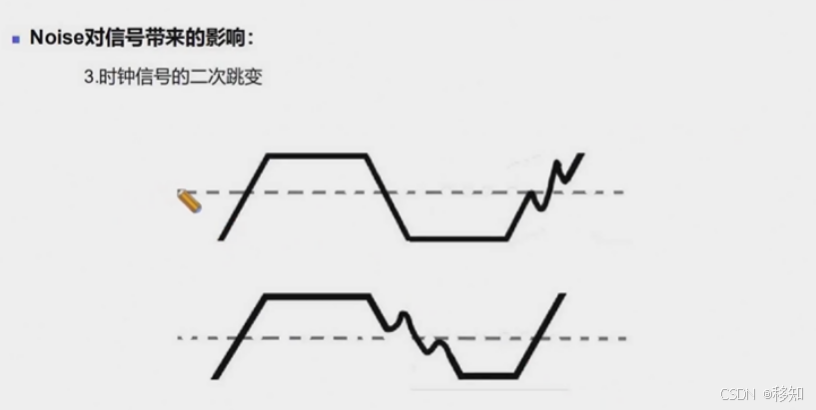

时钟信号的二次跳变:在时钟网络上,噪声可能导致时钟信号产生不必要的二次跳变,影响电路的同步性。

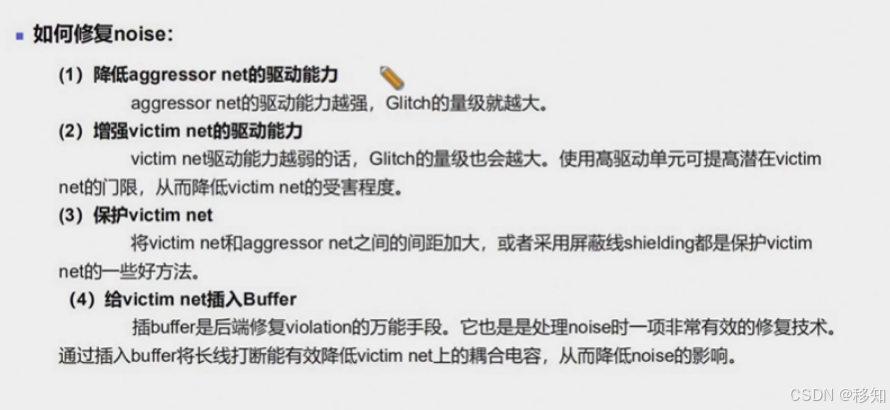

修复噪声问题通常需要从物理层面进行,比如调整信号线的布局、增加屏蔽线或者优化信号线的驱动能力等。

静态时序分析是芯片设计中的一项基础且关键的技术。它不仅涉及到电路设计的时序验证,还涉及到噪声的产生与修复。了解STA的基本概念、Setup/Hold时间的计算方法以及噪声的处理策略,对于芯片设计工程师来说是非常必要的。希望这篇文章能够帮助大家对STA有一个更深入的理解。

2461

2461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?