create_generated_clock

-edges

-divide_by

-multiply_by

(与create_clock -period -waveform不同,通过上述三个指定波形)

-divide_by :

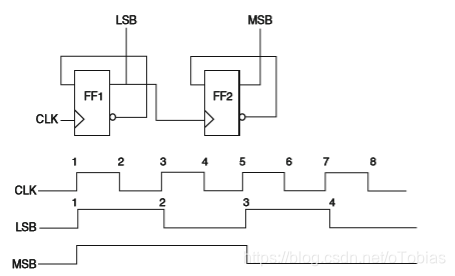

create_clock -period 10 -name CLK [get_ports CLK]

create_generated_clock -name LSB -source [get_port CLK] -divide_by 2 [get_pins FF1/Q]

create_generated_clock -name MSB -source [get_pins FF1/Q] -divide_by 2 [get_pins FF2/Q]

create_generated_clock -name MSB -source [get_port CLK] -divide_by 4 [get_pins FF2/Q]

-edges:

create_generated_clock -name LSB -source [get_ports CLK] -edges {1 3 5}[get_pins FF1/Q]

create_generated_clock -name MSB -source [get_pins FF1/Q] -edges {1 3 5}[get_pins FF2/Q]

create_generated_clock -name MSB -source [get_ports CLK] -edges {1 5 9} [get_pins FF2/Q]

(-edges中间3个数字代表上升沿和下降沿和上升沿)

create_generated_clock

最新推荐文章于 2025-03-25 22:10:53 发布

本文详细介绍了使用create_generated_clock命令创建复杂时钟信号的方法。包括通过divide_by参数实现频率分频,利用edges参数精确控制时钟信号的上升沿和下降沿,以及multiply_by参数调整时钟周期。这些技巧对于时序电路设计尤为关键。

本文详细介绍了使用create_generated_clock命令创建复杂时钟信号的方法。包括通过divide_by参数实现频率分频,利用edges参数精确控制时钟信号的上升沿和下降沿,以及multiply_by参数调整时钟周期。这些技巧对于时序电路设计尤为关键。

559

559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?