目录

前言

任何sdc首先定义的都是时钟。Clock主要包含Waveform、Uncertainty和Clock group的定义。我们把它们称为时钟的三要素,当然创建任何时钟都要检查一下这三者有没有定义正确。

一、clock的属性

clock period

时钟周期为时钟频率的倒数,又称为振荡周期。

clock duty cycle

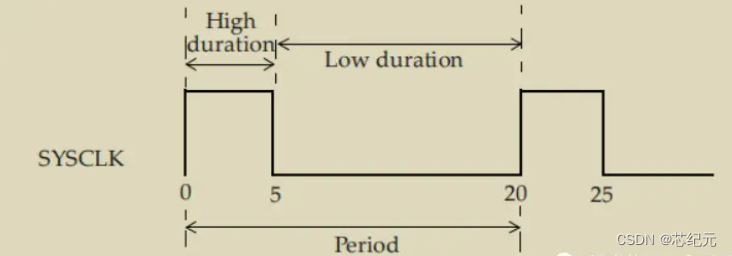

clock duty cycle指时钟高电平信号在一个周期内所占的时间比率,大部分时钟占空比为50%,即高/低电平各占0.5个周期。

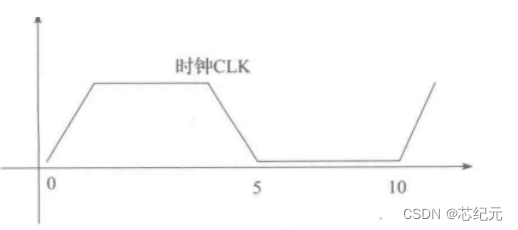

在create_clock的-waveform中,第一个变量是上升沿出现的时刻,第二个变量是下降沿出现的时刻,如果上升沿出现在0ns,下降沿出现在5ns,周期为20的clock对应的波形图如下。

clock latency

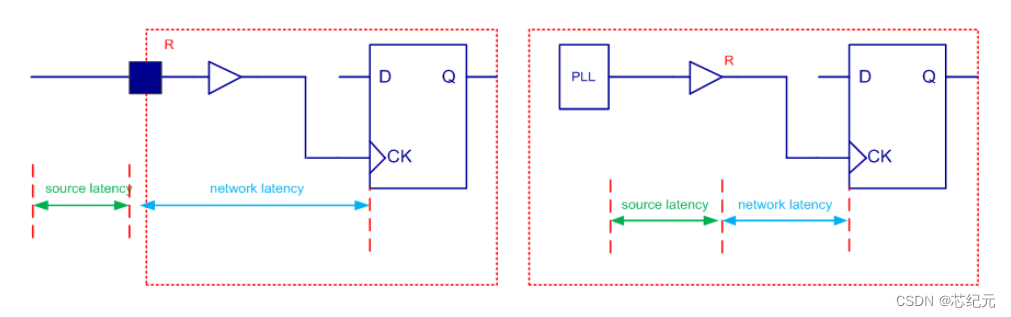

Clock latency通俗意义上是指clock定义点到clock sink点(时序器件的clock pin)之间的这段delay。其分为两类,source latency和network latency。

source latency也称作insertion delay,通常是指clock source端到clock定义点之间的这段时间延迟。通常有两种情况,其一:clock 直接来自于芯片外部,如crystal clock,此时,source latency指的是芯片外部crystal出口到芯片PAD(假如clock定义在此处)之间的时间延迟;其二:clock 来自于芯片内部的PLL,此时,source latency指的是芯片内部PLL输出点到芯片内部某个第一个clock定义点之间的这段时间。

network latency 指的是clock定义点到clock sink点之间的这段delay。

这两种latency是每一个clock的固有属性,当CTS完成之后,每一个clock如果是在propagation状态下,其source latency和network latency都是确定的。当然,在前期(PR之前或者CTS之前),通常情况下clock都处于ideal状态,为了能够模拟真实的情况,我们可以通过指令set_clock_latency去指定每个clock的source latency或者network latency。

clock slew

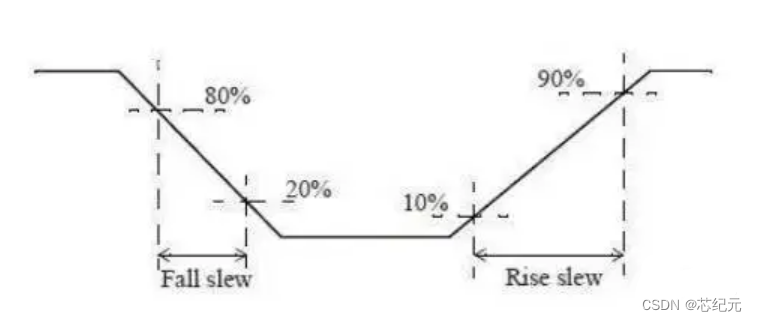

时钟转换时间clock transition time ,也称为clock slew。通常是指电压从10%VDD上升到90%VDD所需要的时间,或者是从90%VDD下降到10%VDD所需要的时间,上升和下降时间过长意味着电路的速度很慢。如下图所示。

在sdc中,可以用set_max_transition 0.1 -clock_path[all_clocks]命令来限制clock slew大小。

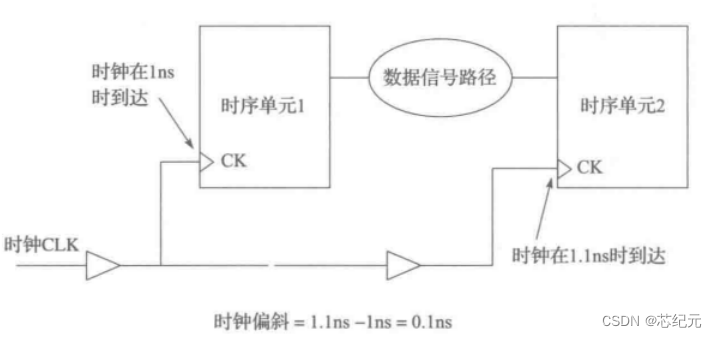

clock skew

在CTS中,由于时钟到每个寄存器的路径延迟不一样,造成信号到达 clock pin 的时间也不一样,寄存器也不会同时翻转。时钟偏差(skew) 的定义就是最长路径延迟减去最短路径延迟的值。一直以来,Skew都是衡量时钟树性能的重要参数,CTS的目的就是为了减小skew。

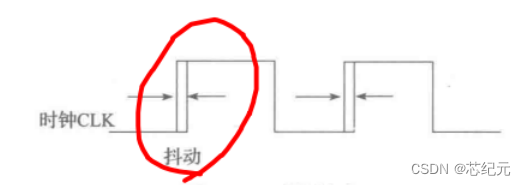

clock jitter

所谓抖动(jitter)指的是在某一个给定的点上时钟周期发生短暂性的变化,使得时钟周期在不同的周期上可能加长或缩短。这是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。

二、create_clock

SoC的时钟一般是由PLL产生,然后经过时钟生成电路和分配网络,最终给具体的功能模块使用。一般地,第三方IP供应商都会提供比较成熟的SDC,SoC集成时只需稍作修改。对于自研的IP和SoC顶层,设计人员在提供RTL的同时,也需提供一份时钟结构图,一方面是方便撰写SDC,另一方面对后端P&R有针对性的进行CTS也非常有帮助。

create_clock命令比较简单易懂,格式如下:

create_clock [-name clock_name

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

776

776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?