SUB-LVDS 与 LVDS介绍 电气规范

今天有同学问SUB-LVDS输出是否能接到LVDS输入上,以前没用过SUB-LVDS,一起学习一下。

Sub-LVDS is a differential low-voltage standard that is a subset of LVDS, and uses a reduced-voltage swing and lower common-mode voltage compared to LVDS. For sub-LVDS, the maximum differential swing is 200 mV compared to 350 mV for LVDS. The nominal common-mode voltage for sub-LVDS is 0.9 V, while it is 1.25 V for LVDS.

下表是SUB-LVDS的电压规格,其共模电压是0.8-1.0V;差分电压是100-200mV;

| Parameter | Min | Typical | Max | Unit |

|---|---|---|---|---|

| Fixed common mode voltage VCMF | 0.8 | 0.9 | 1.0 | V |

| Differential voltage swing VOD | 100 | 150 | 200 | mV |

| Drive current range | 0.833 | 1.5 | 2 | mA |

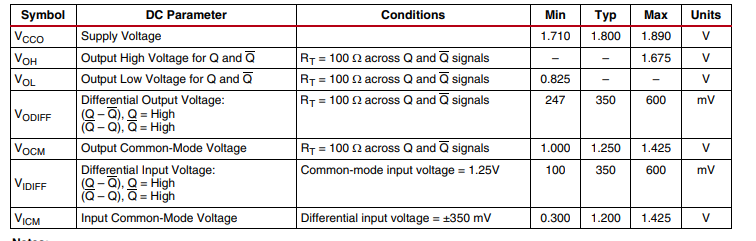

下表是Xilinx K7 FPGA LVDS的电压规格,其输入和输出共模电压范围不同,输入共模电压是0.3-1.425V,输出共模电压是1.0-1.425V,电压摆幅输入和输出也不同,输入是100-600mV,输出是247-600mV;

SUB-LVDS 输出接LVDS输入

根据电气规范,可以直接连。SUB-LVDS 共模电压是0.8-1.0V,在LVDS规定的0.3-1.425V 范围内,差分电压100-200mV在LVDS规定的100-600mV内;

LVDS 输出接 SUB-LVDS 输入

根据电气规范不难直接连接,需要降低共模电压和差分电压摆幅;

具体方法,这里不做详细介绍,参考 https://www.ti.com/lit/an/snla353/snla353.pdf?ts=1683770277650&ref_url=https%253A%252F%252Fwww.google.com%252F

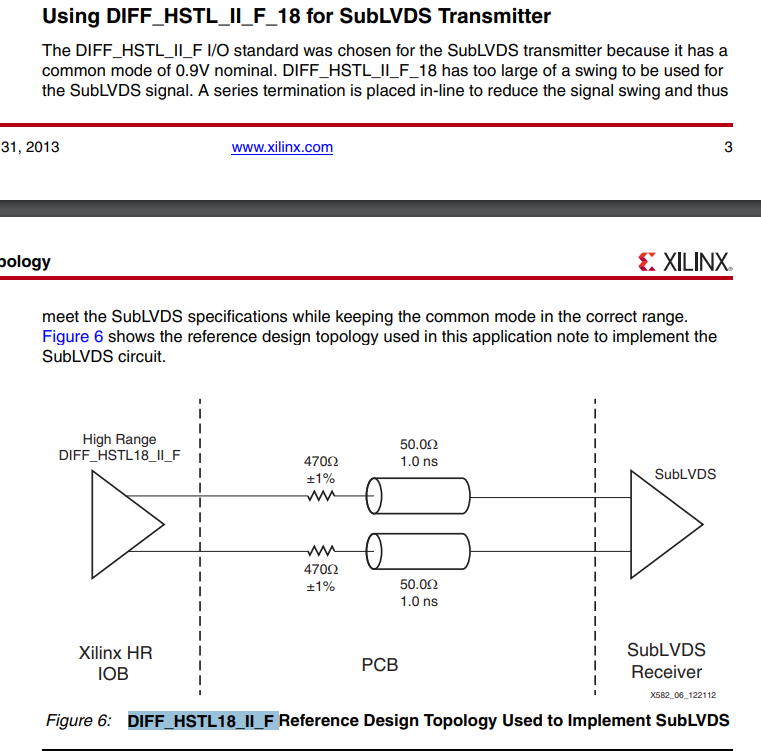

用FPGA 的话,xilinx 也给出了方案

详细请参考手册

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?