UART的Loopback测试原理

之前在X86的项目中,有现成的测试套件burnintest来完成UART的loopback测试。其中的原理可能并不是很命令。只是简单的认为只会是TX-RX数据对传,并判断发送接收的数据的一致性。其实,真正测试的时候,并不是如此千篇一律。

目前在MIPS架构上测试UART,需要编译测试程序出来。大概的研究了下原理。下面是UART loopback测试的环节,以Function的方式呈现。

/* Set of available UART tests */

testDesc tests[] = {

/*loopbackinternal*/

{ "SetLoopback", test_uart_loopback, UART1, 1,0, 0},

{"Signal Check", test_uart_signals, UART1, 1,0, 0},

{ "LineBREAK", test_uart_break, UART1, 1, 0, 0},

{"Internal RX FIFO", test_uart_rx_fifo, UART1, 1, 0, 0},

{"Internal TX FIFO", test_uart_tx_fifo, UART1, 1, 0, 0},

{"ASCII", test_uart_data, UART1, 1,0, 0},

{ "Commformats", test_uart_comm_formats, UART1, 1, 0, 0},

{ "Baudrates", test_uart_baud_rates, UART1, 1,0, 0},

{"Interrupts", test_uart_interrupts, UART1, 1,0, 0},

/*loopbackexternal*/

{ "SetExternal", test_uart_external, UART1, 1, 0, 0},

{"Signal Check", test_uart_signals, UART1, 1,0, 0},

{"ASCII", test_uart_data, UART1, 1,0, 0},

{ "Commformats", test_uart_comm_formats, UART1, 1, 0, 0},

{ "Baudrates", test_uart_baud_rates, UART1, 1,0, 0},

{"Interrupts", test_uart_interrupts2, UART1, 1,0, 0},

{ NULL,NULL, 0, 0, 0, 0}

};

测试UART loopback还需要弄清楚下面几个问题:

1、 UART的接口定义和各个Register。

2、 测试治具。UART上需要插上什么治具?

3、 测试中涉及到的autoflow。

这里先解决这几个问题吧。

UART全称为通用的异步收发装置。有9Pin,各个定义如下:

| DB-9 Pin | EIA abbreviation | Description |

| 1 | DCD | Data carrier detect |

| 2 | RXD | Receive data |

| 3 | TXD | Transmit data |

| 4 | DTR | Data terminal ready |

| 5 | GND | Signal ground |

| 6 | DSR | Data set ready |

| 7 | RTS | Request to send |

| 8 | CTS | Clear to send |

| 9 | RI | Ring Indicator |

其他各个Register的说明还是参阅spec吧。

参考: http://retired.beyondlogic.org/serial/serial.htm

测试治具:

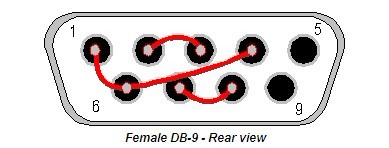

Loopback原理本来就是tx-rx对接完成,完整的连接会涉及到CTS/RTS。下图是一般使用的loopback治具。

其中连接的方式是这样的:

1、 RX—TX;

2、 RTS—CTS;

3、 DCD—DTR—DSR.

这个剖面是母头的接口,公头的接口顺序反过来。

至于autoflow的功能,主要涉及到RTS和CTS的运作。RTS表示请求发送,CTS则是清零发送。在正常工作的时候,此UART的RTS会连接到另外UART的CTS。如果autoRTS功能打开,当RX FIFO的数据量达到设置的FIFO trigger,则会让RTS处于不工作状态。对面的UART的CTS则会检测到这个状态,停止TX的数据发送,直到RX的FIFO中清空了。

下面简单的描述一下uart loopback测试程序的各个环节。

1、 signalcheck

internal和external的信号检测都是一样的,主要是RTS和CTS信号状态的动态设定和检测,通过内部register来设定:MCR和MSR。

2、 ASCII

通过分别对TX和RX的Write 和Read,比较数据的一致性。

3、 commformats

UART不同的基本设定:数据长度、stopbit、奇偶校验等。设定之后在通过ASCII方式测试,并检测是否有error。

4、 Baudrate

不同波特率的设置,在通过ASCII方式验证。并检测是否有error。

5、 Interrupts

通过设定内部register来使能各种中断,并将中断程式注册到CIU中。再通过相应的方式触发中断,使其进入中断程序中做相应动作:比如printf。

在external interrupt测试环节,主要应该有两种方式:1、FIFO enable,通过RTS和CTS控制数据流,并适时的触发FIFO level Trigger,从而产生中断。2、FIFO disable,通过单字节的传输,RX有数据则产生中断。

6、 LineBreak

指在internal loopback中特意发一个break信号,将TX线保持低电位。同时会产生一个中断,并造成有数据发送的假象,如果rx有实际的数据接收到,则failed。

1496

1496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?