(说明,本文所用图片来自于Google图片搜索)

layout engineer应该知道的一些专业术语:

1. layout design 所生成的数据格式: *。gds文件。

2. Tapeout: 标志着设计工作的完成。

3. Tapeout后的芯片加工流程:

设计公司提供设计好的GDS文件, 然后又掩膜工厂提供mask,接着Foundry芯片代工,如此我们就有了wafer(die), 记着就是封装(packer), 得到封装好的芯片,再交由到设计者手中完成最后的芯片测试。

对于纯数字电路设计流程来讲:

Layout Engineer 主要是为设计者提供经过验证的单元板图库(Library), 一般来说这样的工作主要是由Foundry和Service公司来完成的。对于Fabless来讲,主要是应用亦有的库和IP Core来做布局布线,以及验证等一些工作。

对于Analog/ Mix-signal电路的设计来讲:

由于一般的模拟部分采用全定制(Full-Custom)方法来设计,故而模拟部分的layout设计要求较高,需要一定的技巧,这就对Layout Engineer提出较高的要求,保持同前段设计人员的紧密联系,才能做出理想的芯片。

那么进行版图设计,我们需要哪些条件呢?

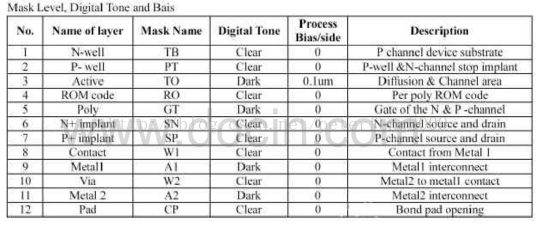

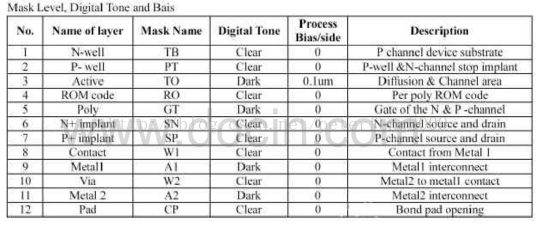

针对工艺的不同,Foundry厂都会提供该工艺各层的说明文件,ts文件(包含工艺信息等),以及DRC和LVS文件等。如果没有GDS文件,那么一般需要自己创建一个tf文件。

Cadence简介

基于UNIX平台的IC开发工具软件包,能够完成从前端到后端的几乎所有的设计工作,业界中记性Layout Design主流工具就是Cadence软件包中就是Virtuoso Layout Editor。、

登入UNIX系统: .cshrc

运行Cadence: .csinit cds.lib 和 .cdsenv

.csinit包含信息有bindkey, default, SKILL command等,还可定制affirma模拟仿真环境;

.cds.lib 包含库同目录的对应关系;

Library-Cell and view-Open a design-Edit inside of library.

Create工艺库方法一:适用于有Technology File的情况,

1. 使用该tf file来构建一个new library, 具体的操作,FIle-New-library。

2. 填入name, 选择Compile new Techfile。

3. 填入tf文件路径和文件名, 点OK, 完成。

方法二:适用于提供GDS文件的情况。

现在主流的设计结构都是设计库与工艺库分离的结构,只在设计库中进行设计,而工艺库则只作为一个参考提供不同的设计库所引用。

步骤一与方法一种的步骤一相同,不同的步骤二选择Don't Need a Techfile, 点OK, 完成。如果你需要在设计库中进行版图开发的话,就需要进行如下的操作,建立设计库同工艺库之间的联系:现则CIW menu ----Technology File ----Attach to. 然后选择设计库 attach to 工艺库,完成。

- LSW窗口(Layer Selection Window)

Set Drawing Layer: 在LSW窗口中用鼠标left-click你要使用的layer.

Ser Layer Visible: 点AV按钮,所有层都可见。

点NV按钮,除了当前选中层意外,其它层都不可见。

“Shift +Click” 快捷键 可以改变层的显示,包括层的名字以及显示的信息。

"Middle - Click" 快捷键 可以是层在可见与不可见之间进行转化。

"Shift + Middle - Click" 快捷键 使得除了当前选择层以外的其他所有层均不可见。

Set layer Selectable: LSW窗口默认状态是都都选,也可以通过按钮AS来确认全部按钮都可以选择。

点NS按钮,确定全部都不可选的状态。

“right-click” 快捷键 可以使一个层在选择与不选择之间进行转换。

“Shift + right-click” 快捷键 可以使某个layer可选,其余不可选。

Set Valid layer: 选择的LSW当中valid layer.

Set Layer Purpose Pair: 在CIW当中选择Edit layers ....,

弹出的窗口选择,点ADD ...(注意: 每次修改都要save. )

出现窗口,可设置增加pair

出现窗口可设置display.drf文件,配置layer的显示。

在cadence中层次化的概念,我们可以用tree的结构来理解。在一个设计当中往往会由一些较小的单元,组成一个相对比较大的单元;然后再由这些较大的单元组成一个更大的单元,以此类推,。。。。。。,最后,我们会得到一个最大的单元,成为最高层(level = 0), 而前面构成它的小单元,我们以此称为level = 1, 2, .......。

有两种方法可以控制不同层的显示:

1. Shift + f , Ctrl + f;

2. 设置display option中的display levels;

Flatten:所谓Flatten就是将level低的层提高;

Make Cell: 可以说是Flatten的你操作,将一部分Layout做成一个单独的cellview。

Hierarchyical Editing: 对层次化版图编辑的方法。

Stream Translation:

- Stream out ( layout-----to----gds文件):在CIW窗口中File-------Export-----------Stream...。

- 在弹出的的窗口中,Return Directory是指导出gds文件所在的路径。

Top Cell Name要导出Cell name。

View name: layout

Output File: 导出文件名,主要这里必须加上gds的文件名后缀。

3. Stream in (gds文件--------to--------layout): 在CIW窗口中File--------Import----------Stream...。

4. 在弹出的的窗口,你同样要确定导入文件所在的目录以及文件的名字。这一次要注意的是:

你需要确定这个gds文件要导入到什么库当中,一般情况下,如果你所填写的库还没有建立起来,系统会帮你自动建立。但是这只是适用于 Foundry只提供给你gds文件,你可以创建工艺库。

- Starting from Simple layout ( Inv, Nand, Nor, And)

我们的目标只有一个就是在最小的面积情况下,达到最好的performance, at least reaonable to fabrication.

2. Tap: There're two kinds of well taps: Ndiff inside Nwell and Pdiff inside Pwell (or P-sub). The former is used to connect the Nwell to Vdd, and the latter is used to connect the Pwell ( or P-sub) to Vss. At the same time, well tap can reduce resistance between metal and Nwell or Pwell ( or P-sub).

8904

8904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?