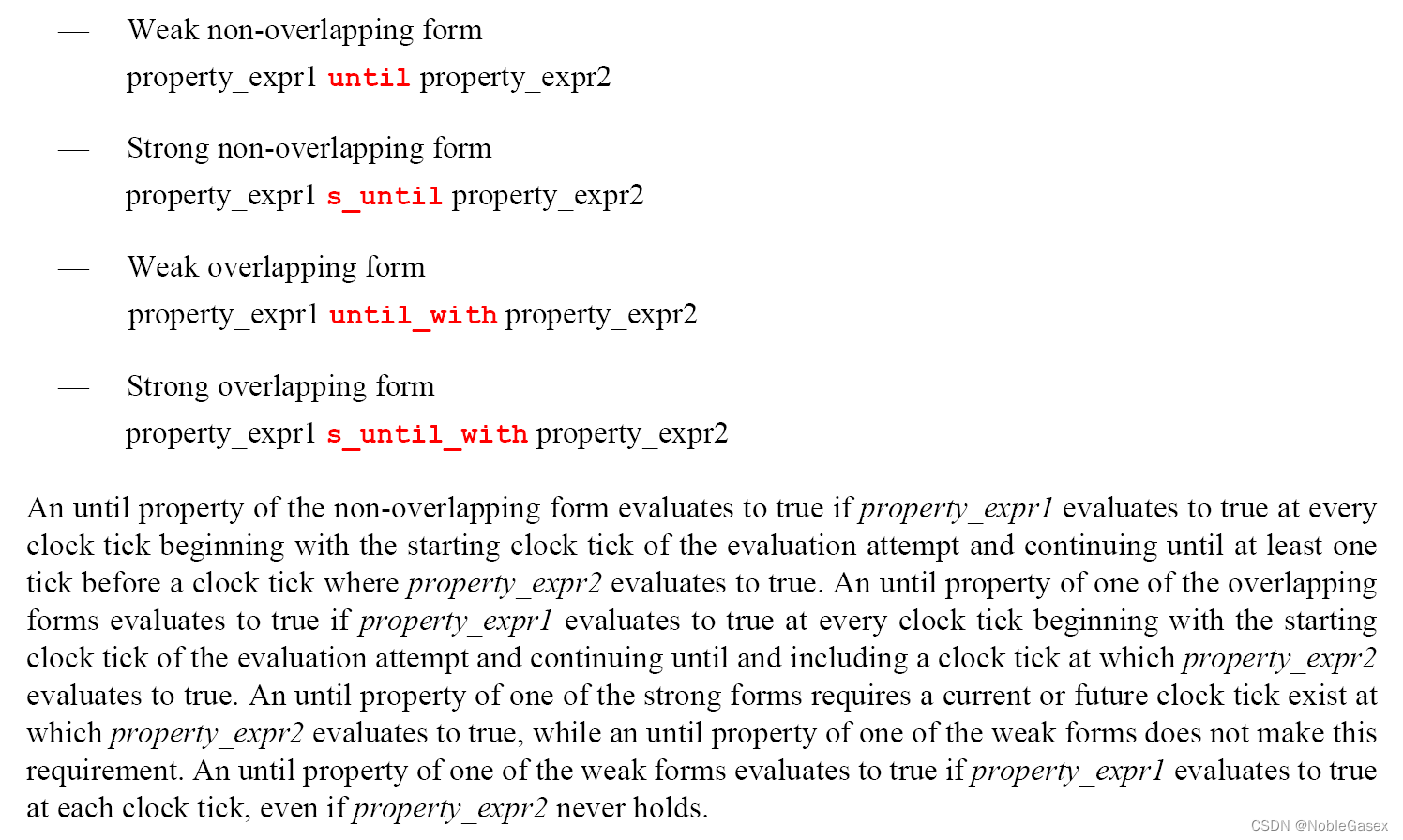

until

直到property_expr2满足的情况的前一拍,property_expr1一直满足,当property_expr2满足的时候property_expr1不满足

until_with

直到property_expr2满足的情况,property_expr1一直满足,当property_expr2满足的时候property_expr1满足

具体类容参见下图

An example

问题描述

cs拉高时,数据、地址不变,直到cs拉低,具体保持的时间不定。

Solution 1

property dout_stable_fell_property;

@(posedge clk) $rose(cs) |=> ($stable(dout)[*0:$] ##1 !cs);

//@(posedge clk) $rose(cs) |=> ($stable(dout)[*1:$] ##0 !cs);

endproperty下面注释的也可以使用。

solution 2

property dout_stable_fell_property;

@(posedge clk) $rose(cs) |=> $stable(dout) until $fell(cs);

endproperty运行代码脚本使用可以参考:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?