xilinx FPGA srio 接口verilog源码程序,顶层接口封装为fifo,使用简单方便,已运用在实际项目上。

本源码支持srio NWRITE、NWRITE_R、SWRITE、MAINTENCE、DOORBELL等事务。

1、提供srio源码

2、提供srio license文件

3、提供操作文档

ID:43468670735087329

在逃码农

xilinx FPGA srio 接口verilog源码程序,顶层接口封装为fifo,使用简单方便,已运用在实际项目上。

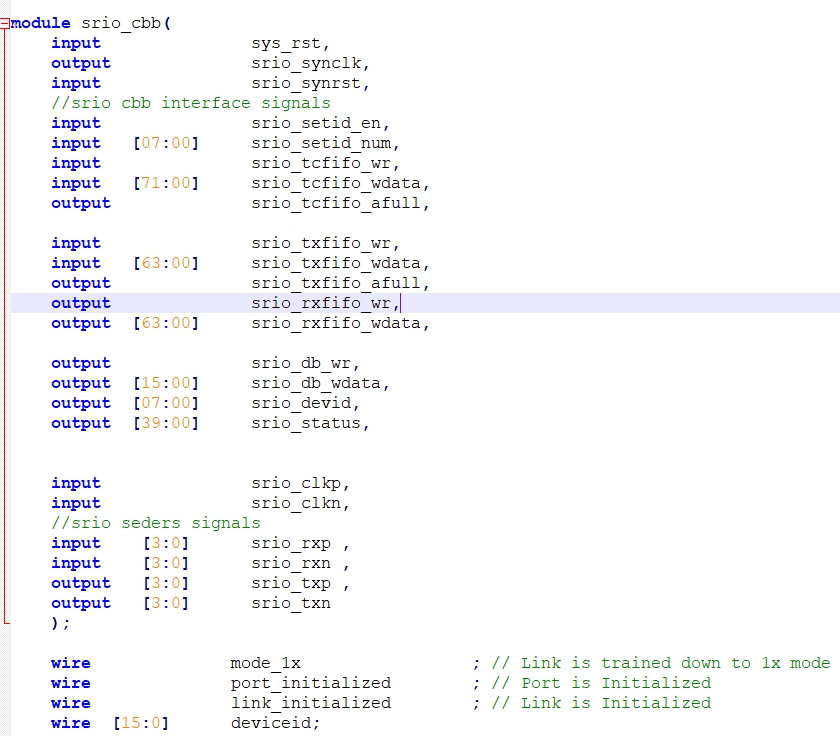

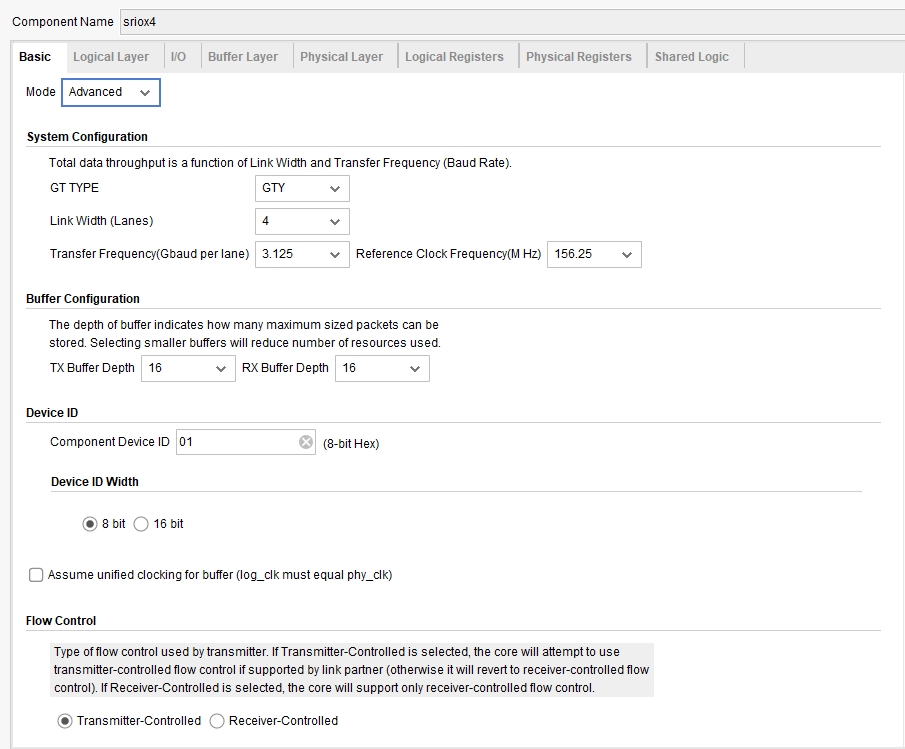

首先,我们介绍一下xilinx FPGA的SRIO(Serial RapidIO)接口,它是一种高速串行通信接口,用于连接FPGA芯片与其他设备或处理器。SRIO接口具有高带宽和低时延的特点,适用于各种数据密集型应用,如数据中心、高性能计算和通信系统等。

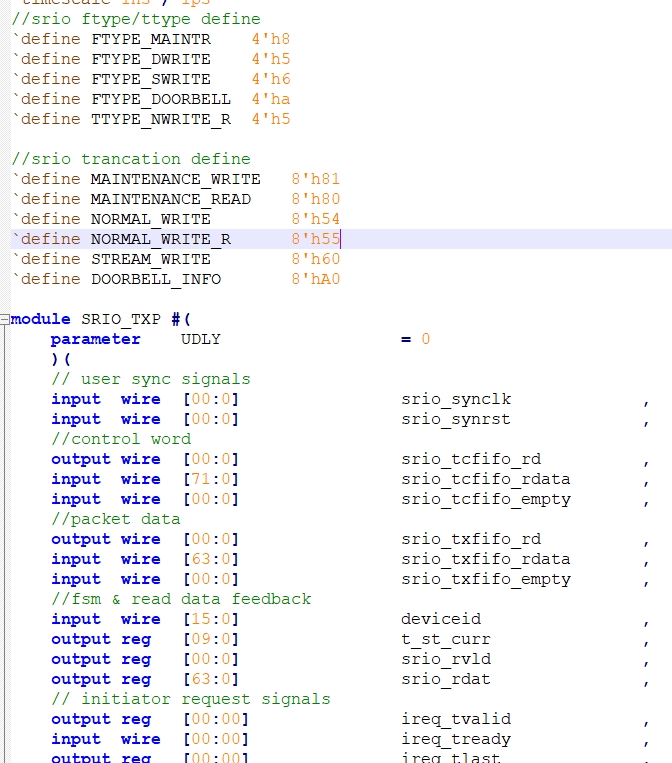

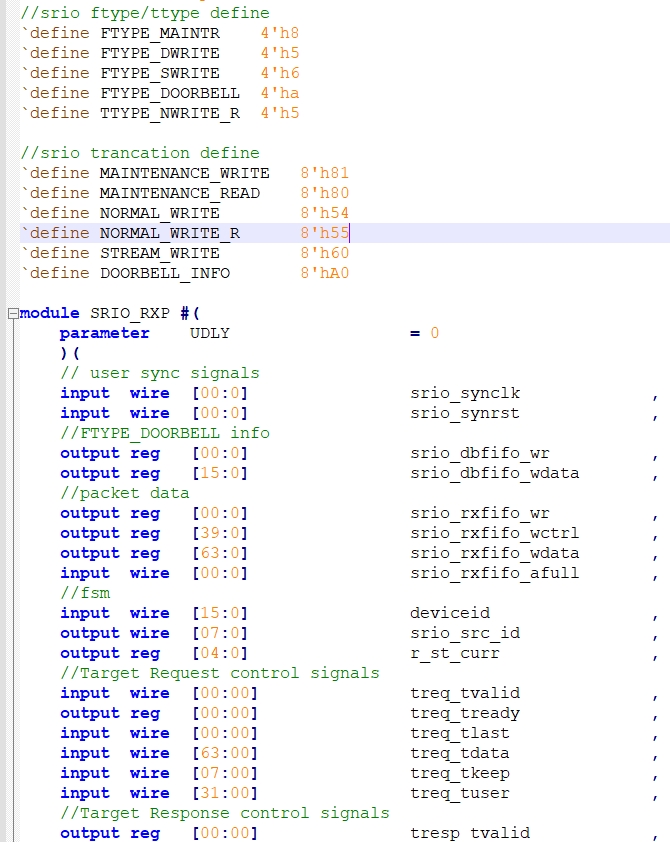

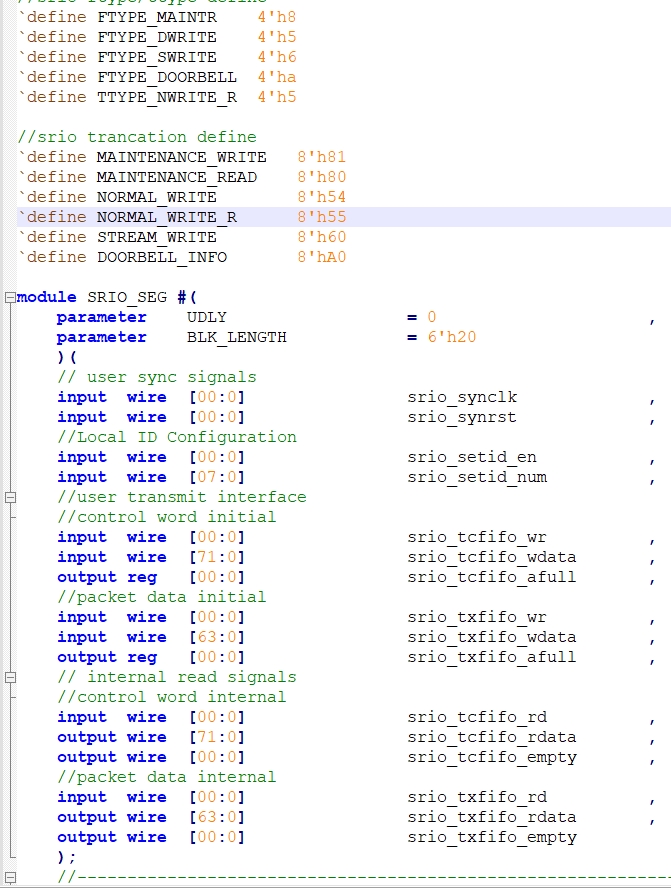

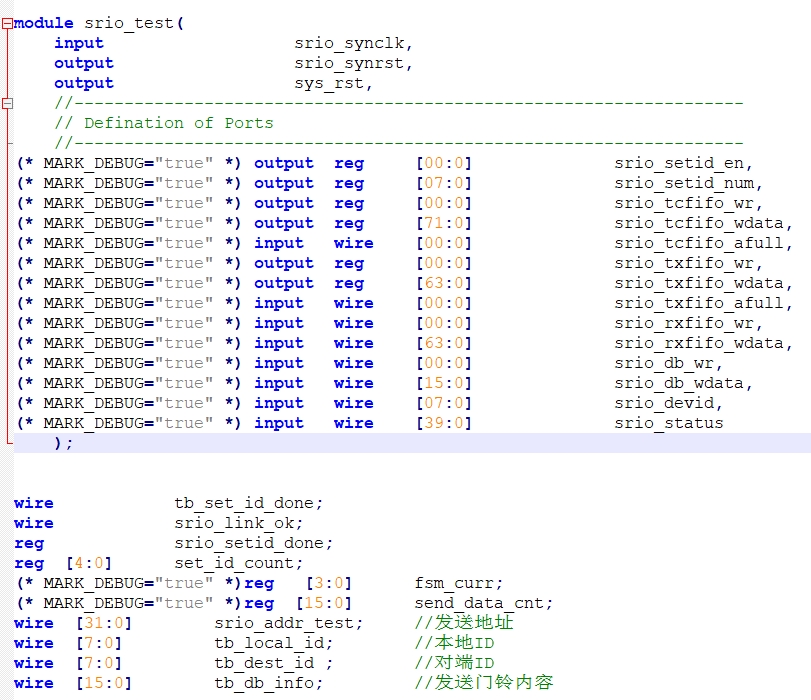

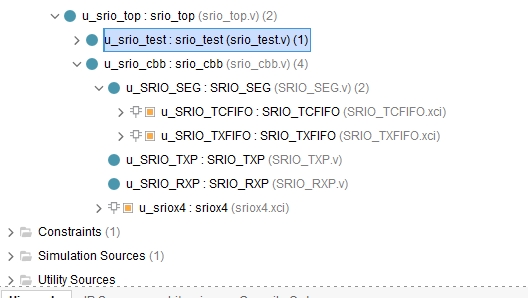

在这里,我们提供了一份基于xilinx FPGA的SRIO接口的Verilog源码程序,我们将顶层接口封装为fifo,这样使用起来更加方便,同时也提供了对应的操作文档和SRIO license文件。

我们的源码程序支持SRIO的多种事务,包括NWRITE、NWRITE_R、SWRITE、MAINTENCE和DOORBELL等。这些事务涵盖了SRIO接口的各种功能,可以满足不同应用场景的需求。

对于需要使用SRIO接口的开发者来说,我们提供了方便快捷的解决方案。通过使用我们的源码程序,开发者可以直接集成SRIO接口,节省了大量的开发时间和精力。同时,我们提供的操作文档和SRIO license文件,可以帮助开发者更好地理解和使用SRIO接口,确保项目的顺利进行。

我们的源码程序已经在实际项目中成功运用,经过实践验证,在稳定性和可靠性方面表现出色。我们经过精心设计和优化,保证了源码程序的性能和效率。开发者可以放心使用,并根据自身需求进行二次开发和定制。

总结一下,我们提供了一套完整的解决方案,包括xilinx FPGA的SRIO接口的Verilog源码程序、操作文档和SRIO license文件。我们的源码程序支持多种SRIO事务,使用简单方便,已经在实际项目中验证过。如果您需要使用SRIO接口,我们相信我们的解决方案将会是一个非常理想的选择。

希望我们提供的这份源码程序和相关文档能够帮助到您,如果您有任何问题或者需要进一步了解,欢迎随时与我们联系。我们将竭诚为您提供支持和帮助,共同推动技术的发展和应用的创新。

相关的代码,程序地址如下:http://wekup.cn/670735087329.html

790

790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?