1. 评估的背景目的

考虑维度:

资源需求,开放程度,学习难度,工具链资源。

最好是国产FPGA支持,或者开源EDA工具链支持。

目标还是寻求一款在FPGA上低成本跑起来并能够支持一定的程序开发,最好实现一款能把RT-THREAD或FREERTOS跑起来的MCU.

2. CSDN&知乎综合性文章

1).汇总性文章

五、分享优秀的 RISC-V 项目资源_玩转risc-v-CSDN博客

开源 riscv 的一些实现和资料链接_riscv-v 开源代码-CSDN博客

知乎的汇总文章:

FPGA/IC优质开源项目(九)RISC - 知乎 (zhihu.com)

2)其中几个特色项目

sifive家的freedom

仓库:

GitHub - sifive/freedom: Source files for SiFive's Freedom platforms

介绍文章:

开源RISC-V 项目Freedom在Arty-7-100T开发板上的实现_arty a7 100t 程序烧写-CSDN博客

这个Freedom项目其实是可以生成两种SoC的:

- E300

- U500

以及支持四种FPGA平台:

- Arty-35T

- Arty-100T

- VC707

- VC118

FPGA 开发板约2699, 淘宝可购买,淘宝链接就支持riscv,文档应该较为齐备。

Arty A7-100T Artix-7 Xilinx FPGA RISC-V 开发板 Digilent-淘宝网 (taobao.com)

35T已停产,不过只要1500左右。

蜂鸟:

基于ZYNQ7010实现的蜂鸟E203:

RISCV SOC项目(基于蜂鸟E203开源RISCV CPU)_蜂鸟e203搭建soc-CSDN博客

蜂鸟处理器是在国内RISC-V社区大名鼎鼎的芯来科技开发的RISC-V MCU系列。E203是其开源的一款单privilege mode,两级流水(不严格说法)的MCU,主打小面积、低功耗。使用Verilog开发。麻雀虽小,五脏俱全,也包括debug module,代码严谨优美,用来学习设计没得说。官方文档不算多,但是市面上可以买到胡振波大牛写的两本书,也算是学习资料丰富了。

两本什么书?

胡振波大牛写的《手把手教你设计CPU——RISC-V处理器篇》

官方仓库:

github: https://github.com/SI-RISCV/e200_opensource

一句话点评:初学者学习RISC-V处理器设计首选。

无剑100:

官方仓库

github: https://github.com/T-head-Semi/wujian100_open

优势是带了AI能力。

项目链接:

项目首页 - wujian100_open - GitCode

探索Wujian100_open:T-head Semi打造的高性能AI芯片开源框架-CSDN博客

平头哥目的应该是推广这套平台,里面包括软硬件系统及SDK,从开源的程度来看,重点应该是软件。当然我是从研究学习硬件部分出发来说的,如果是使用无剑平台,包括仿真、FPGA、软件开发,应该是没有问题的。

Ibex

提到开源RISC-V就不能不提Riscy系列了,尤其是zero-riscy,使用很广泛。Ibex是脱胎于zero-riscy的core,支持RV32IMC及一些Z系列指令,由LowRISC维护。Ibex小巧精悍,文档详实,学习资料丰富,支持verilator, 可以使用verilator+openOCD+GDB 仿真时debug。对于我这样的重度Verilator依赖者来说非常友好。

github: https://github.com/lowRISC/ibex

文档:https://ibex-core.readthedocs.io/en/latest/introduction.html

VexRiscv

VexRiscv可配置,可支持RV32IMCA,可配置为经典5级流水。VexRiscv使用SpinalHDL开发,类似Chisel,也是一款基于Scala的硬件建构语言。可配置MMU,所以理论上可以支持操作系统。

VexRiscv有个官方的SoC:Briey,使用AXI接口。和Rocket Chip一样,支持Verilator+OpenOCD+GDB仿真。和Rocketchip一样都是使用scala解释器sbt工具,超占内存,快把我的老爷机拖垮了。

VexRiscv文档很少很粗略。

github:https://github.com/SpinalHDL/VexRiscv

一句话点评:佳作,SpinalHDL代表作,需入SpinalHDL的坑。

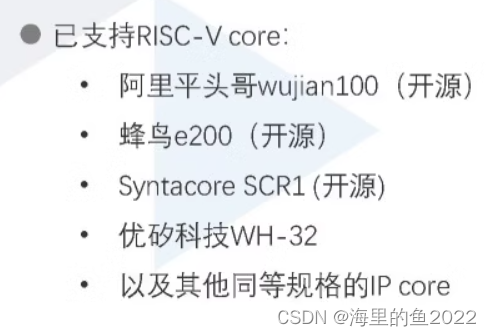

3. 从能买到开发板的硬件实现平台来看

开发板选择:

1) XILINX 平台:

A7通用开发板:

XILINX FPGA开发板A7全功能开发板豌豆FPGA零基础自学到进阶-淘宝网 (taobao.com)

有个性价比还不错,针对RISV的xilinx开发板:

Perf-V/perfv/riscv开发板/Artix-7 35T/50T/100T/xilinx/FPGA-淘宝网 (taobao.com)

芯来的官方开发板: (蜂鸟就是芯来的开源项目)

MCU200T开发板/蜂鸟FPGA/riscv/RISC-V 国产FPGA开发板/芯来科技-淘宝网 (taobao.com)

芯来的文档, 针对蜂鸟平台专用的开发板,应该资源和环境是比较容易上手的。

RISC-V开发板_专业RISC-V处理器IP及解决方案公司 (nucleisys.com)

芯来是两家主要的国产IP厂商之一,官方支持的好处是产品化可直接衔接IP厂商走向商品化芯片设计。

2)国产高云平台:

高云TANG MEGA 138K

Sipeed Tang Mega 138K Pro Dock 高云 RISCV FPGA 开发板 集创赛-淘宝网 (taobao.com)

可以运行软核的TANG

Sipeed Tang Primer 25K高云GW5A RISCV FPGA开发板PMOD SDRAM-淘宝网 (taobao.com)

25K级别, 者20K 都可以。

开发板资料可以仔细研究下。 都可以上“小麻雀处理器”

4. 软件仓库汇总

1).github上的汇总项目:

GitHub - riscvarchive/riscv-cores-list: RISC-V Cores, SoC platforms and SoCs

这个够全了。

比较典型的几个

GitHub - xiaowuzxc/SparrowRV: An embed RISC-V Core with RV32IMZicsr ISA named SparrowRV.

典型如lbex

Open source silicon · lowRISC: Collaborative open silicon engineering

2). GITEE上的其他开源项目:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?