接https://blog.csdn.net/pxy198831/article/details/85340554

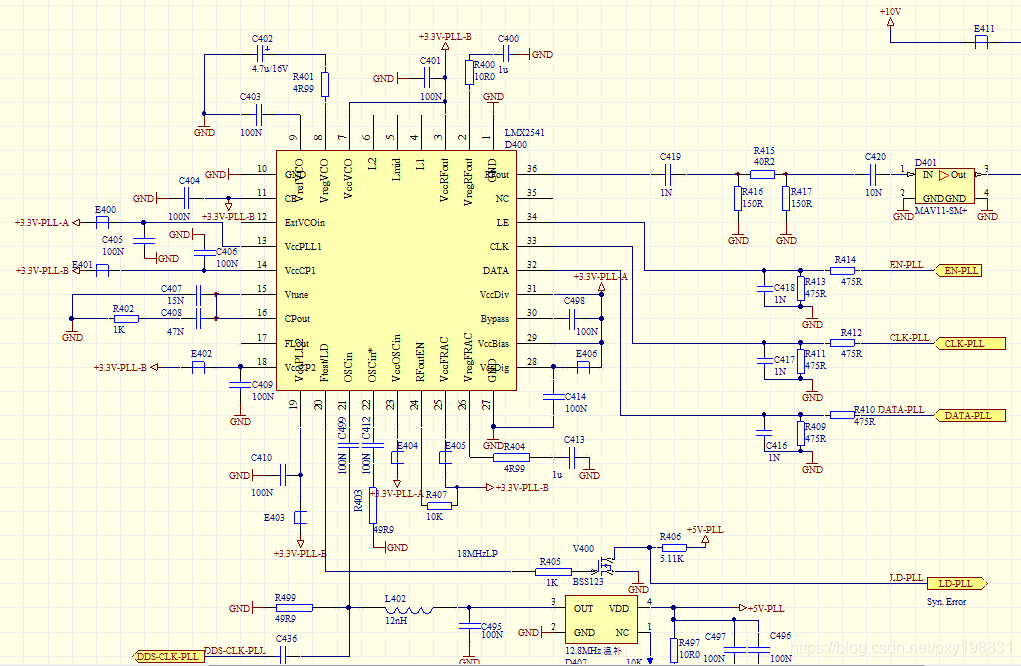

NUC140之PLL(频率合成器LMX2541)

PLL。即相位锁相环,实际上就是一个频率合成器。拥有指标好,杂散低的优点。

但是对比直接频率合成器DDS,频率锁定时间较慢,一般为数ms,

而DDS的时间在us甚至ns级别。

芯片采用多路3.3V供电,有条件的可以采用2-3个独立的3.3V供电,

电压加了滤波磁珠,就是E开头的器件。

根据芯片手册推荐的电源引脚来分开接,已达到电源隔离,为了获取较好的指标。

我们知道一个PLL芯片相位噪声是一个很重要的指标,这就需要在设计的时候,

尽可能满足芯片手册的推荐条件。

由于频率准确度要求2ppm(百万分之一),所以选用12.8MHz的温补晶振。

该信号芯片可以输出40MHz到3、4GHz的频率。

以100MHz为例,1ppm就是频率误差100Hz,这个误差随着温度和时间都会逐渐恶化,

当恶化到10-20ppm的时候,需要进行从新校准。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

681

681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?