1.ZYNQ介绍

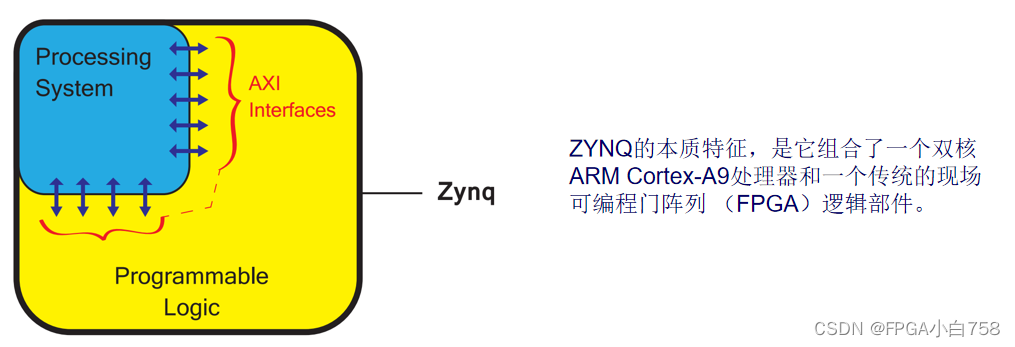

全称为Zynq-7000 All Programmable Soc

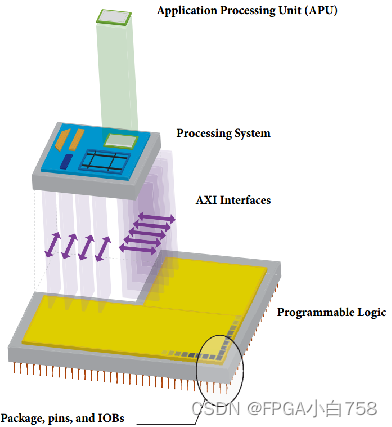

1.Zynq是赛灵思(Xilinx)推出的新一代全可编程片上系统,将处理器的软件可编程性和FPGA的硬件可编程性完美结合。具有较强的系统性能、灵活性与可扩展性。

2.旨在为视频监控、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。

3.是一颗SOC(System on chip)芯片也就是片上系统,此芯片既有传统FPGA也有ARM处理器。开发时需同时掌握verilog硬件描述语言和C语言。

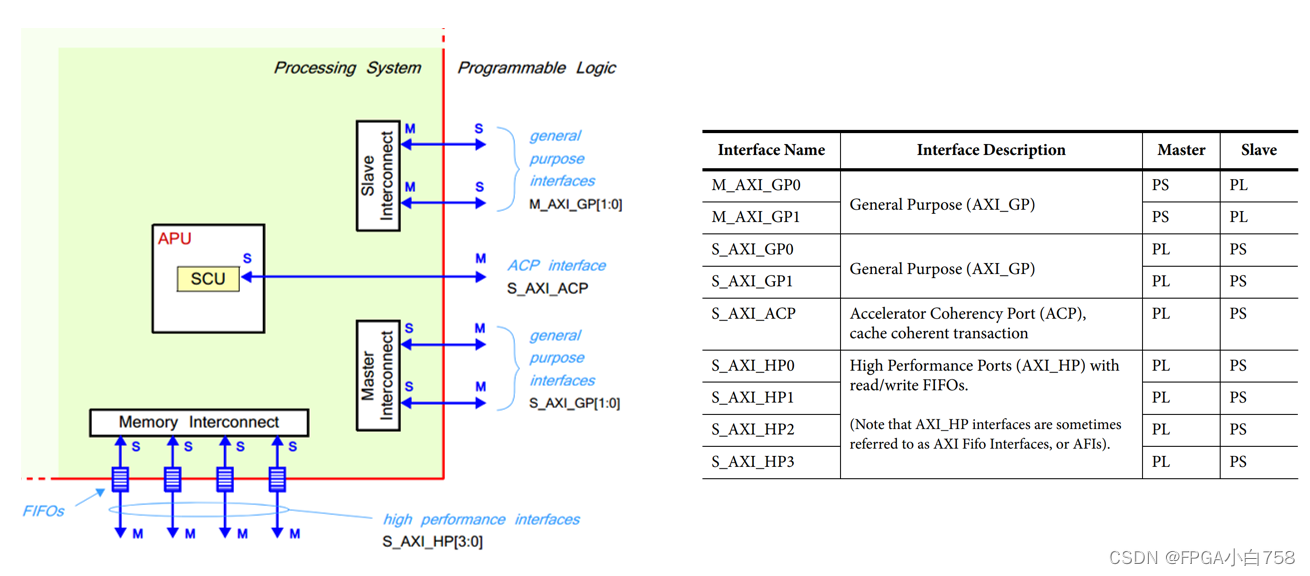

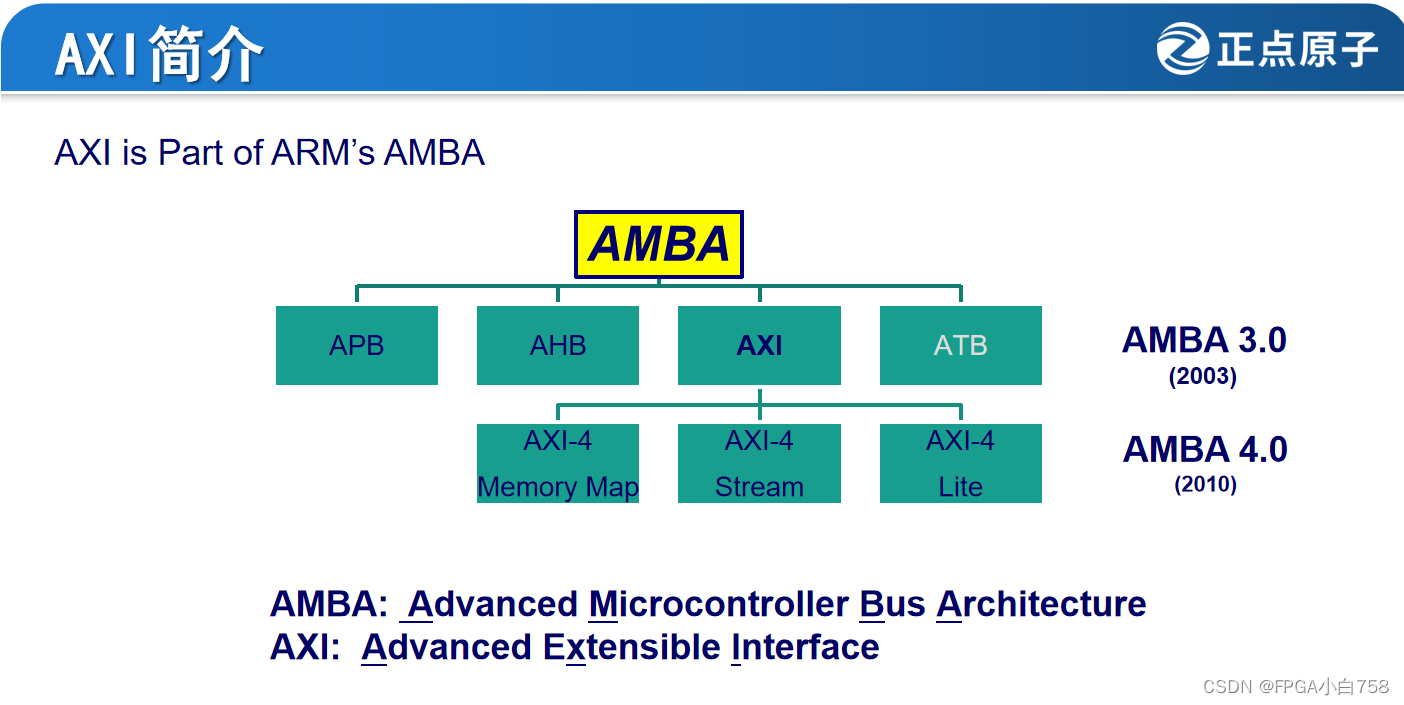

4.FPGA与ARM通讯总线接口为AXI总线,PS(ARM端)PL(FPGA端)进行通讯。

5.EMIO可以把PS端接口扩展到PL端使用。

2.PL(FPGA)

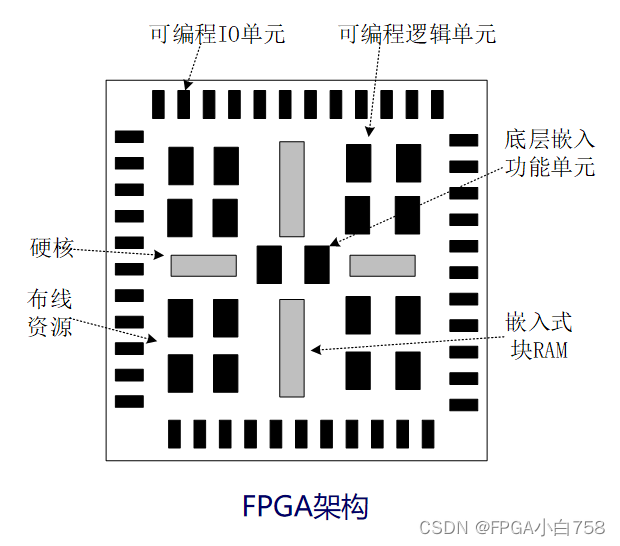

早期生产的数字集成电路逻辑都是固定不变的。要想改变它的逻辑功能,就必须改变内部各单元电路之间的连接,而这种连接在集成电路制作过程中已经固定下来了。

允许用户自行修改内部连接的集成电路:可编程逻辑器件(Programmable Logic Device)

1、PLD内部的电路结构可以通过写入编程数据来设置;

2、写入PLD的编程数据还可以擦除重写;

常用的可编程逻辑器件:

CPLD:复杂可编程逻辑器件(Complex Programmable Logic Device)

FPGA:现场可编程门阵列(Field Programmable Gate Array)

本质差异:电路结构不同。

CPLD:基于“乘积项”的与或逻辑阵列

FPGA:基于“查找表”(LUT,Look UP Table)的CLB阵列

3.PS(ARM)

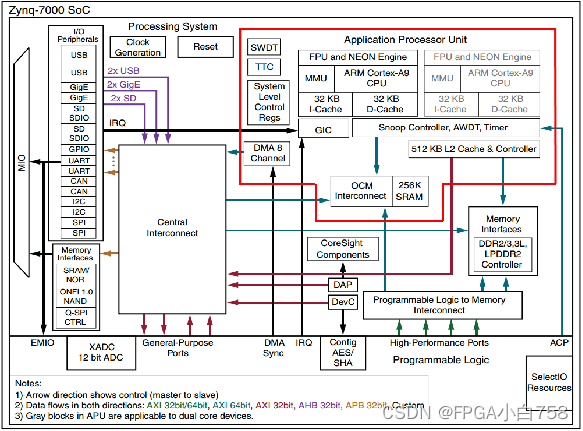

3.1 APU

1.FPU and NEON Engine:FPU浮点运算单元,NEON单指令多数据引擎。大量并行计算加速。

2.MMU:存储管理单元,物理地址到虚拟地址映射。

3.I-Cache,D-Cache:指令Cache和数据Cache。一级Cache。

4.512KB L2 Cache:二级Cache,两个处理器共用资源。

5.OCM:on chip memory,片上存储器

6.DMA:直接存储范围,数据搬移

7.GIC:中断控制器

3.2 PS

1.Central Interconnect:终端互联,负责管理并指挥AXI接口之间的通信。

2.I/O:与外界的接口,通过MIO与外界连接。54个

3.Memory Interfaces:存储器接口,静态(左下角)或者动态(右侧)存储器接口。

4.Clock Generation:时钟生成模块,生成内部各个模块所需要的时钟频率。

5.Reset:复位模块

PL端(下面部分)

6.EMIO:扩展IO,通过连接到PL的IO进行扩展。

7.XADC:PL里面的硬核,实现数模转换。

8.DMA:PL到PS直接存储访问。

9.IRQ:中断请求,PL端可产生中断传到PS的中断控制器。

10.Config AES/SHA:FPGA配置接口。PL部分其实是由PS配置的。PS先启动配置PL。

11.AXI接口:包括ACP、High-Performance Ports Programmable Logic、General-Purpose Ports。

3.2.1AXI

1536

1536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?