基本的寄存器register是D-type Flipflop。而D触发器有两种,一种是同步复位(synchronize),另一种是异步复位(asynchronize),两者的不同表现在reset这个信号上。

同步复位D触发器的原理:因为同步的意思是复位信号与时钟同步,即遇到时钟上升沿后,根据复位(reset)信号判断最终的结果,所以首先检测时钟的上升沿信号。若出现时钟上升沿时检测到复位(reset)信号,则 输出Q置0,若出现时钟上升沿时没有检测到复位(reset)信号,则正常进行D触发器的功能:输出Q置输入D。

异步复位触发器原理:因为异步的意思是复位信号与时钟异步,即复位(reset)信号出现时,输出立即置0,与时钟信号无关,所以首先检测复位(reset)信号。若有复位(reset)信号,则输出Q立即置0。若无复位(reset)信号,则在时钟上升沿正常进行D触发器功能。

根据上面的描述,可以写出两种寄存器的VHDL,因为存在条件判断,所以用到process:

同步复位D触发器:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity DFF_syn is

PORT(D,CK,RESET:IN STD_LOGIC;

Q :OUT STD_LOGIC);

end DFF_syn;

architecture Behavioral of DFF_syn is

begin

SYN:PROCESS(CK,RESET)

BEGIN

IF ck='1' AND ck'event THEN

IF RESET='1' THEN Q<='0';

ELSE Q<=D;

END IF;

END IF;

END PROCESS;

end Behavioral;

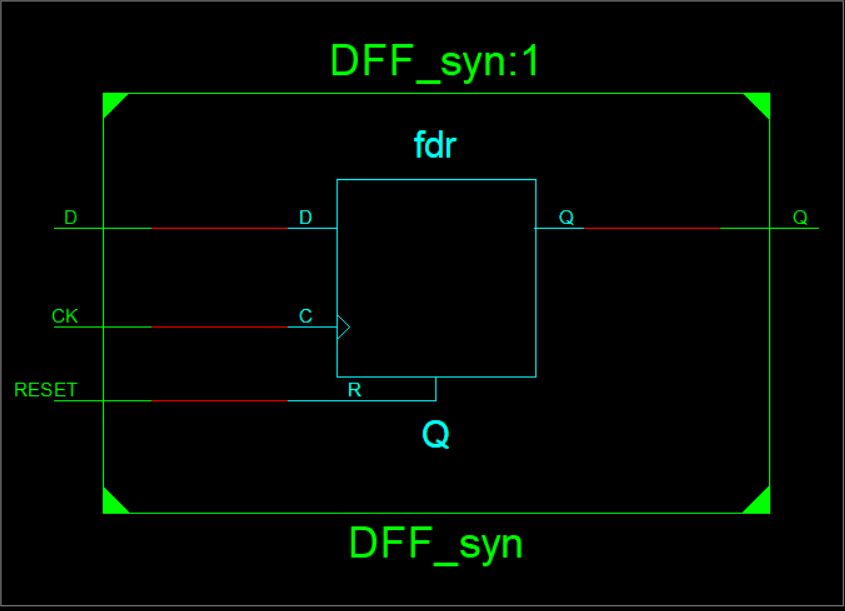

RTL图:

异步复位D触发器:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity DFF_asyn is

PORT(D,CK,RESET: IN STD_LOGIC;

Q : OUT STD_LOGIC);

end DFF_asyn;

architecture Behavioral of DFF_asyn is

begin

ASYN:PROCESS(CK,RESET)

BEGIN

IF RESET='1' THEN

Q<='0';

ELSIF CK'EVENT AND CK='1' THEN

Q<=D;

END IF;

END PROCESS;

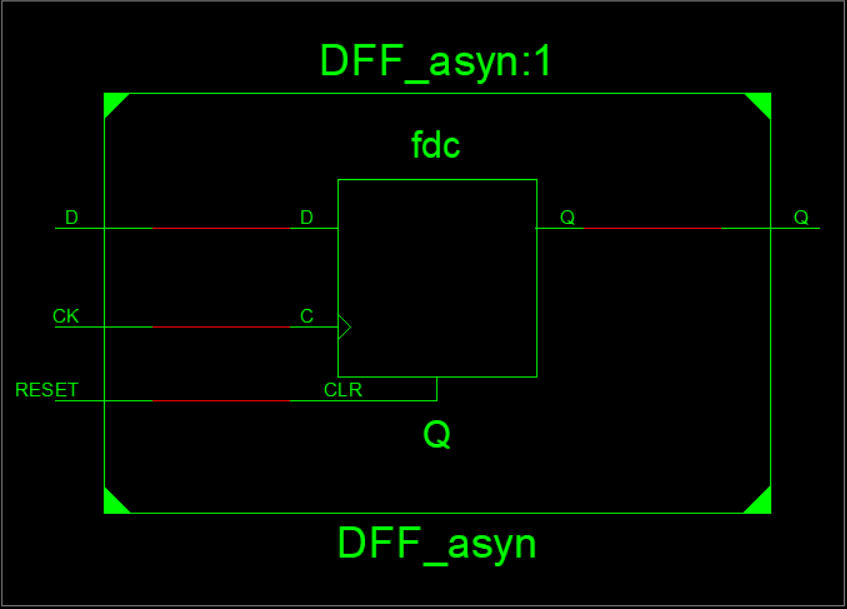

end Behavioral;RTL图:

testbench测试:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_DFF_asyn IS

END tb_DFF_asyn;

ARCHITECTURE TEST OF tb_DFF_asyn IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT DFF_asyn

PORT(

D : IN std_logic;

CK : IN std_logic;

RESET : IN std_logic;

Q : OUT std_logic

);

END COMPONENT;

--Inputs

signal D : std_logic:='0';

signal CK : std_logic:='0';

signal RESET : std_logic:='0';

--Outputs

signal Q : std_logic:='0';

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

--constant CLK_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: DFF_asyn PORT MAP (

D => D,

CK => CK,

RESET => RESET,

Q => Q

);

-- Clock process definitions

CLK_process :process

begin

--wait for 100 ns;

CK <= '0';

wait for 5 ns;

CK <= '1';

wait for 5 ns;

end process;

-- Stimulus process

process

begin

wait for 100 ns;

--

-- D<='0';

-- --CK<='0';

-- reset<='0';

-- wait for 10 ns;

--

-- D<='1';

-- --CK<='1';

-- reset<='0';

-- wait for 10 ns;

--

-- D<='1';

-- --CK<='1';

-- reset<='1';

-- wait for 10 ns;

--CK <= NOT CK AFTER 10 ns;

D <= NOT D AFTER 50 NS;

RESET <= NOT RESET AFTER 200 NS;

wait;

end process;

END TEST;

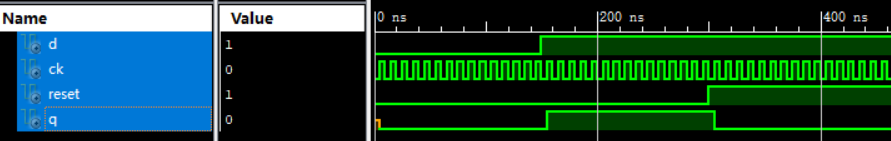

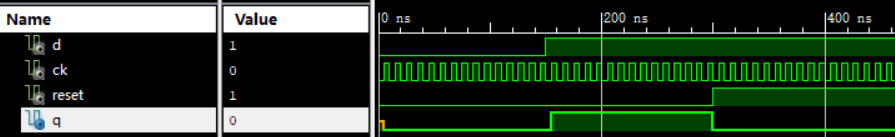

测试结果:

同步复位D触发器:

异步复位D触发器:

则一般来说的寄存器REG的

behavioral结构为:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY REG_MULTI IS

GENERIC(NBIT:INTEGER:=16);

PORT( D:IN STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0);

CLK:IN STD_LOGIC;

RST_n:IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0)

);

END REG_MULTI;

ARCHITECTURE BEHAVIORAL OF REG_MULTI IS

SIGNAL TEMP:STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0);

BEGIN

PROCESS(RST_n,CLK)

BEGIN

IF RST_n='0' THEN

Q<=(OTHERS=>'0');

ELSIF (RISING_EDGE(CLK)) THEN

Q<=D;

END IF;

END PROCESS;

--Q<=TEMP;

END BEHAVIORAL;

3339

3339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?