最近做了一些USB主控芯片的验证工作,具体是OTG2.0,可作host也可以做dev。

其中对ULPI总线的各个信号总是弄混,时常看又时常忘记。今日直接完全弄懂。

用的ULPI PHY是USB3320,其信号如下所示。注意,这些信号的方向是从PHY这一侧看的。其中CLK和DATA没啥好说的,在大多数情况下,CLK基本上是输出;DATA是双向端口;DIR和NXT是PHY的输出,STP是PHY的输入。

下图文字中的Link可简单理解为单片机或者CPU上的USB;transceiver可理解为PHY。

看下实际板载的连接情况。对于CPU或者单片机,DATA是双向的,CLK、DIR、NXT都是输入信号,唯有STP是输出的。

DIR:PHY的输出。在传输数据时,DIR拉高说明PHY在控制总线,向CPU发送数据;在传输数据时,DIR拉低说明CPU在控制总线,PHY被动接受。另外,DIR拉高还有一种情况:在刚上电不稳定的时候,说明PHY此时无法接收Link传来的数据。

NXT:PHY的输出。在传输数据时,当DIR拉高,且NXT拉高,说明PHY向CPU传输,此时NXT表明当前数据有效,相当于tx data valid信号;在传输数据时,当DIR拉低,且NXT拉高,说明CPU向PHY传输数据,且拉高NXT表明当前数据被PHY接收,相当于一个握手反馈信号。

STP:CPU的输出。在CPU向PHY传输数据时,当STP拉高,说明上一个周期是CPU传输的最后一个字节。另外,当刚上电不稳定时,STP也会拉高。

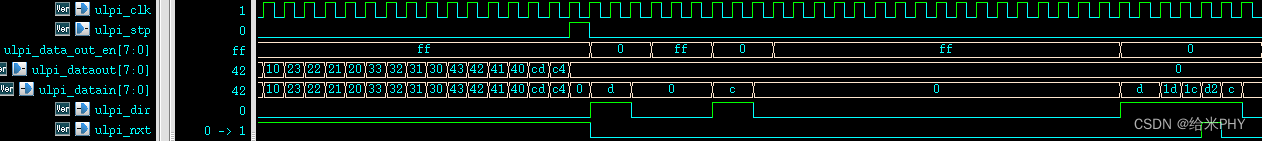

看下实际波形。

将CPU配置成USB HOST模式,向dev的地址0x11的端点1发送数据,LSB优先,数据分别为0xaaabacad、0xaeafbabb、0xbcbdbebf、0xcacbcccd。

令牌阶段:0x49->0x11->0x8是令牌包,发起bulk in传输。此时DIR拉低,NXT拉高,说明CPU向PHY传输数据,也就是CPU向外部传输数据。0x49占据两个CLK周期,说明第一个周期时,PHY没有成功接收0x49,而在第二个CLK时,NXT拉高,说明PHY成功接收了0x49。对于0x11和0x8也同理。

数据阶段:DIR和NXT都拉高,说明PHY向CPU传数据,NXT此时相当于tx data valid信号。0x4b为PID,后续跟着数据和CRC。

握手阶段:此时DIR拉低,发送0x42时又占据了两个CLK周期(高4bit的0x4代表发送,低4bit的2代表PID,这是芯片中规定的),直到NXT拉高后,0x42下一拍才变为0。NXT拉高后的下一拍,STP拉高,说明这是CPU传输数据的最后一个字节。至此,bulk in传输结束。

对于HOST的bulk out传输,贴上波形,请自行分析。

2342

2342

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?