前言

对BRAM的工作时序做简要介绍,

详细内容请参考官方数据手册:“pg058-blk-mem-gen,LogiCORE IP Block Memory Generatorv7.3”。

各个模式的时序图

1 Write First Mode: In WRITE_FIRST mode, the input data is simultaneously written into memory and driven on the data output, as shown in Figure 9. This transparent mode offers the flexibility of using the data output bus during a write operation on the same port. (输入数据同时写入memory与data_output)

如上图所示,WEA为低电平,ENA 为低电平时,处于DISABLED状态。 在第一个READ状态中,WEA为低电平,ENA为高电平,故DOUTA输出为ADDR(aa)的数据。在WRITE MEM(bb)状态中,WEA为高电平,ENA为高电平,DIN为1111,输入到MEM与DOUTA中。 同理, WRITE MEM(cc)状态中,DOUTA为2222。最后一个READ状态,WEA为低电平,为读数据状态,故读出MEM(dd)的数据。

2 Read First Mode: In READ_FIRST mode, data previously stored at the write address appears on the data output, while the input data is being stored in memory. This read-before-write behavior is illustrated in figure 10. (先前存储在写地址处的数据出现在数据输出上,而输入数据存储在存储器中)

如上图所示,在WEA为高电平,且ENA为高电平时,DINA均写入到bb与cc的MEM中,而DOUTA输出先前存储在地址线的数据。

3 No Change Mode: In NO_CHANGE mode, the output latches remain unchanged during a write operation. As shown in Figure 11, the data output is still the previous read data and is unaffected by a write operation on the same port.(在写操作中,输出latched保持不变,output始终保持先前的值不受影响)

如上图所示,由No Change Mode的特性可知,虽然在WEA与ENA同时为高电平的时候,DOUTA依然为MEM(aa)的值。而DOUTA保持在WEA变换为低电平后,读取ADDR(dd)的值输出。

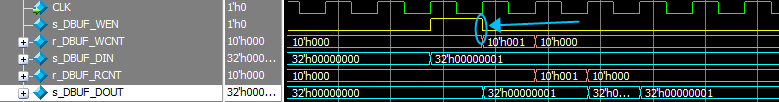

简单双口ram仿真,PORT B READ Latency=1。如下图所示,当箭头那一刻的时刻,有效数据写入,之后WEA拉低,PORT B端口立即有数据输出,也即WEA高电平的下一拍就可以采样PORT B端口的有效数据。

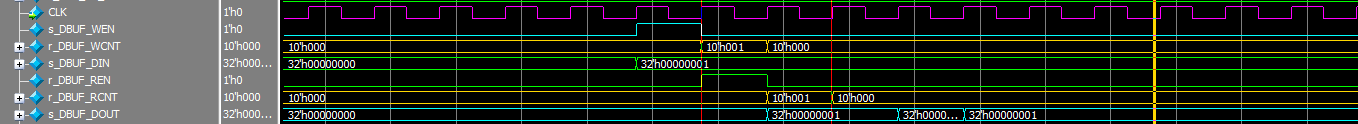

PORT B READ Latency=2,如下图所示。

参考

| 作者 | 博文 |

| 1、jtclm | ISE ip核调用RAM 与 RAM模式的时序分析 |

| 2、skyplain1984 | XILINX之RAM使用指南(加个人总结) |

| 3、ciscomonkey | Xilinx RAM IP核的使用 |

| 4、aikimi7 | Altera自带的RAM仿真学习 |

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?