一、总览

链路初始化和训练,由物理层进行控制,是一个基于硬件的过程。初始化设备的链路和端口,使得设备能够收发报文,在链路上正常通信。

在reset后由硬件自动启动完整的训练过程,并由LTSSM管理。

1 位锁定

训练开始,接收端时钟和发送端时钟不同步,接收端无法可靠采样输入信号的数据bit

训练期间,接收端的时钟和数据恢复(CDR,clock and data recovery)逻辑,通过使用数据bit流作为时钟的参考信号,来重建发送端的时钟,一旦从数据流中恢复了时钟,表示接收端完成位锁定。

2 符号锁定

编码8b/10b来说,下一步训练进行符号锁定,接收端可以接收单个bit,但是不知道10bit组成符号的边界,收发端交换有序集TS1和TS2时候,接收端接收可识别的pattern,如COM符号,因为COM符号独特编码导致它容易被识别找到,识别到COM后,接收方不但定位到两个符号的边界,还可以定位到两个有序集边界(TS1 TS2以COM作为开端,可区分)。

3 块锁定

和符号锁定不太一样,没有编码方案的支持,但是还是需要区分块边界。解决方式就是在有序训练集中包含更多的EIEOS(电气空闲退出有序集),用于定位边界。特定是00h和FFh交替的pattern。

4 链路宽度

PCIE可以使用不同的链路宽度,如X2和X4的端口设备连接,链路训练过程中, 两台设备会设置为两者能接受的最大值(交集)。

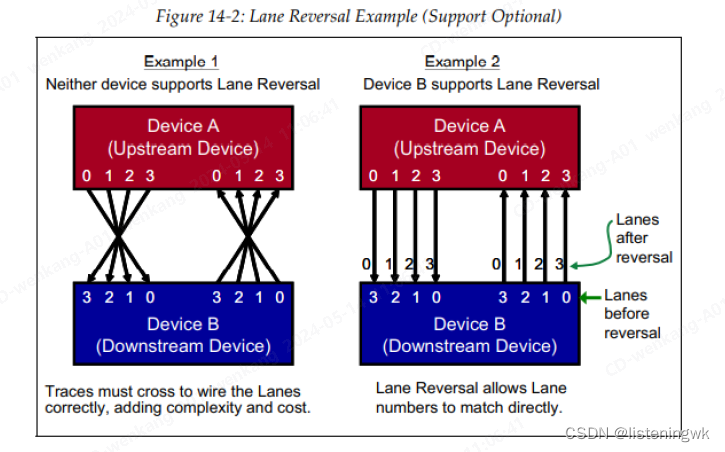

5 通道翻转

通常设备端口在多通道情况下,从0开始依次递增;端口对端口也是0对0,1对1这样;

这个功能主要是简化PCB布线,当支持通道翻转时候,如4通道情况下,默认是0-0,1-1,...这样的,但是某种原因,需要0-3 1-2 2-1 3-0这样交叉进行对接,如有通道翻转,开启后,效果和默认一样;这是可选项。

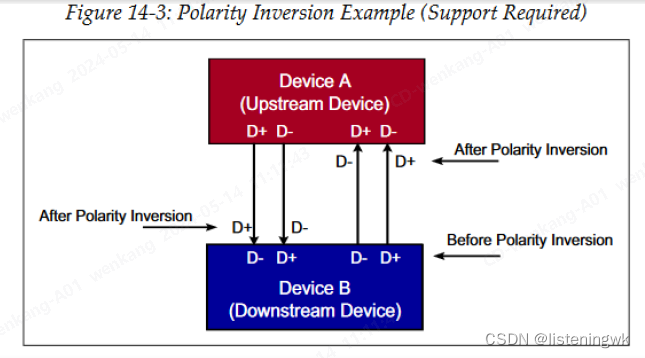

6 极性翻转

两个设备间D+和D-是支持反接的,目的也是为了简化PCB布局布线。任意的接收端都需要单独检测查分信号的连接情况,如发生极性翻转,训练期间自动纠正。这是必选项。

7 数据链路速率

reset后,链路初始化和训练状态机总是会将速率设置为默认的2.5Gbit/s,实现向后兼容(第一代就是2.5)。若是要实现更高的速率,完成训练后,LSTTM再重新进行一次过程更短的训练,以改变双方都支持的最高速率;

8 多lane信号去偏移

通道间的传输线长度有差异,导致多通道链路中同时并行传输的bit,到达接收端有差距,称为信号偏斜;接收方需要延迟到达早的通道,对齐所有通道的信号时间,补偿通道之间的信号传输快慢的差异;

6~8可以很大程度上简化PCIE PCB设计。

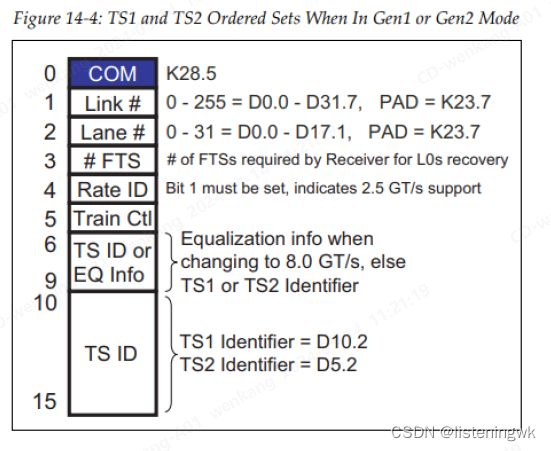

二、链路训练的有序集

链路训练过程设计的有序集TS1和TS2

LTSSM在轮询、配置以及恢复状态中,收发端都会交换TS1 TS2有序集。

| symbol | description |

| 0 | gen1/gen2:COM(k28.5)符号;GEN3: 1Eh->TS1有序集 |

| 1 | Link Number链路编号:

|

| 2 | Lane Number链路编号:

|

| 3 | N_FTS 有序集数量:从L0s返回L0时,接收方收到快速FTS有序训练集数量。 |

| 4 | data rate identitifer(数据速率标识符) bit 0:reserved; bit 1:必须置1,支持2.5GT/s bit 2: 若bit3为1,那么bit2必须为1,支持5GT/s bit 3:支持8GT/s bit 5:4::reserved; bit 6:LTSSM一些特定状态下使用,其他状态reserved; bit 7:speed change,只在recovery和rcvLock LTSSM状态设置,其余状态reserved; |

| 5 | training controller(训练控制)

|

| 6 | Gen1/Gen2:

bit0~bit2:receiver present hint bit3~bit6:transmitter present bit7:set 1 GEN3: bit0~bit1:equalization control(仅在recovery equalization 以及loopback状态使用) bit2:reset EIEOS interval Count(仅在recovery equalization 以及loopback状态使用) bit3~bit6:transmitter preset bit 7: use preset(仅在recovery equalization 以及loopback状态使用) |

| 7 | GEN1/GEN2 TS1标识符:4Ah(D10.2) GEN3: bit0~bit5:FS(Full Swing value) bit6~bit7:reserved |

| 8 | GEN1/GEN2 TS1(4Ah):D10.2 GEN3: bit0~bit5:LF(Low Frequency value),需要符号6的EC=01b bit6~bit7:reserved |

| 9 | GEN1/GEN2 TS1(4Ah):D10.2 GEN3: bit0~bit5:post-cursor coefficient bit6: reject coefficient values bit 7:parity(P)---该校验码覆盖范围:6 7 8 以及符号9[6:0],接收方需要重新计算校验码并且与之比较,通过后TS1才算有效 |

| 10~13 | Gen1/Gen2: |

| 14~15 | Gen1/Gen2: • TS1 标识符(4Ah) ,即 D10.2 Gen3: • TS1 标识符(4Ah),或者DC-balance符号 |

TS2:

| symbol | description |

| 0 | gen1/gen2:COM(k28.5)符号;GEN3: 2Dh->TS1有序集 |

| 1 | Link Number链路编号:

|

| 2 | Lane Number链路编号:

|

| 3 | N_FTS 有序集数量:从L0s返回L0时,接收方收到快速FTS有序训练集数量。 L0s:0~255 |

| 4 | data rate identitifer(数据速率标识符) bit 0:reserved; bit 1:必须置1,支持2.5GT/s bit 2: 若bit3为1,那么bit2必须为1,支持5GT/s bit 3:支持8GT/s bit 5:4::reserved; bit 6:LTSSM一些特定状态下使用,其他状态reserved; bit 7:speed change,只在recovery和rcvLock LTSSM状态设置,其余状态reserved; |

| 5 | training controller(训练控制)

|

| 6 | Gen1/Gen2:

bit0~bit2:receiver present hint bit3~bit6:transmitter present bit7:equalization command GEN3: bit0~bit5:reserved(仅在recovery equalization 以及loopback状态使用) bit6:Quiesce Guarantee(仅在recovery revrCfg状态使用) bit 7:request equalization(仅在recovery revrCfg状态使用) |

| 7~13 | GEN1/GEN2 TS2(45h):D5.2 GEN3: TS2(45h) |

| 14~15 | Gen1/Gen2: • TS1 标识符(4Ah) ,即 D10.2 Gen3: • TS1 标识符(4Ah),或者DC-balance符号 |

每个字段的详细含义:

1 symbol 0:

GEN1/GEN2:所有有序集的首个符号都是K28.5(COM)字符。

接收方通过接收COM字符,锁定符号,确定边界。COM字符需要同时出现在所有通道上,因此可以用于信号去偏移。

GEN3:有序集所在的block前面是2bit的同步头,后面的首个符号标识有序集类型(TS1是1Eh,TS2=2Dh)。

2 Symbol 1(Link #):链路编号;poll状态使用填充字符填充,其他状态为分配的链路编号;

3 Symbol 2(Lane #):通道编号,poll状态使用填充字符填充,其他状态为分配的链路编号;

4 Symbol 3(N_FTS):接收方,从L0s(电源状态)退出,返回L0,接收到快速训练序列(FTS)数量。

退出L0s状态时,发送方至少会发送N_FTS个FTS。取决于需要FTS的数量和当前链路速率。

5 Symbol 4(Rate ID):设备报告所支持的数据速率,和一些给由硬件发起的带宽改变功能信息。

所有信息都必须支持2.5GT/s速率,且复位后始终被训练为2.5GT的速率,任何新设备都需要后向兼容(如支持8GT,那么必须支持5GT/s)

Autonomous change:

若为1,任何带宽改变请求都是基于电源管理方面原因发起的;

若发起带宽请求时候,未置1,那么代表设备在较高速率或者较宽链路检测到工作不稳定的情况时候,需要改变带宽设置(如降低速率或减小链路宽度)来解决这些问题。

Selectable De-emphasis

上游端口:5GT速率下期望的去加重水平设置,具体设置取决于实现。

下游端口/根节点端口:在polling.Compliance状态中,接收该bit数据设置select_deemphasis变量。

Link Upconfigure Capability:表示一个较宽的链路减少宽度后,是否有能力重新恢复原来的链路宽度。

Symbol 5(training control):链路双方一些特殊情况交流(或者说通信)。如一次热复位,使能回环或者关闭加扰。

Symbol6~9:

GEN2/GEN1:符号7~9表示TS1和TS2的标识符。符号6的bit7若是0,那么也表示标识符。

若bit7为1,表示当前有序集面向一个下游端口,发送的是EQ TS1或者EQ TS2,发送EQ TS意味着链路速率达到8GT,上游端口是需要知道当前使用的均衡参数。信息包括发送端的预设集选择,接收预设集选择提示。

GEN3:6~9符号提供均衡过程所需的预设集选择数值及参数。

Symbol10~13:TS1或者TS2标识符

Symbol 14~15:

GEN1/GEN2:表示TS1或者TS2标识符;

GEN3:表示基于本通道DC均衡的需要。DC均衡指的是目前发送的0和1的数量差值。

三、数据训练与状态控制机

LTSSM包含11个顶层状态:

detect、polling、configuration、recovery、L0、L0s、 L1、 L2、Hot Reset、Loopback、DIsable;

可分五大类:

链路训练状态;

重训练状态;

软件驱动电源管理状态;

主动电源管理;

任意复位释放后,LTSSM进入训练类状态,一切正常情况下,顺序如下:

detect->polling->configuration->L0,进入L0状态后,便可以正常收发报文。

进入链路重训练(recovery)状态的原因很多,如L1重恢复或者链路带宽切换。在此状态下,链路重复类似训练操作的状态,来解决链路问题,并最终回到L0(正常工作状态)。

设备进入低功耗状态下,会强制链路进入低功耗软件管理链路状态,如L1 L2;

如果链路上很长时间没有报文需要传输,ASPM硬件逻辑会使得链路进入低功耗ASPM状态,如L0s或者ASPM L1。

其他状态:禁用状态(disable)、回环状态(loopback)、热复位(hot reset)状态。

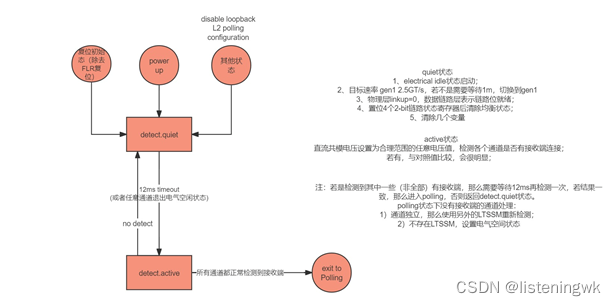

检测状态(detect):复位释放后进入的初始状态,用于检测链路对端设备是否存在。其他LTSSM的状态也可转移到detect状态。

轮询polling:发送端将以2.5Gbps的速率向对端发送TS1和TS2序列,使用协议最低速率以实现对早期协议的后向兼容。接收端接收到序列后,完成如下功能:

位锁定;

符号锁定或者块锁定;

必要情况下校正通道极性翻转;

获取通道支持的链路数据速率 ;

测试条件下,发起兼容性测试(主要是快速验证链路的电压 BER 时序以及其他指标都在链路可容范围内);

配置状态(configuration):上游或者下游器件,按照2.5速率,交换TS1和TS2序列,实现如下目标:

协商链路宽度;

为各个通道指派编号;

检测通道是否顺序或者极性交换,在本地恢复这些交换;

补偿各个通道之间的时序偏斜;

这个状态可以关闭加扰,进入disable或者loopback状态,还会记录TS1和TS2序列交换时候的N_FTS,即L0s状态进入L0状态所需的FTS序列数量。

L0状态:L0是一个链路全功能正常的状态,链路上可以正常进行TLP DLLP和有序集的交换。L0状态下,链路速率可以比2.5GT/s更高,但只能在进入recovery状态,经历一次速率切换后,才能达到更高的速率。

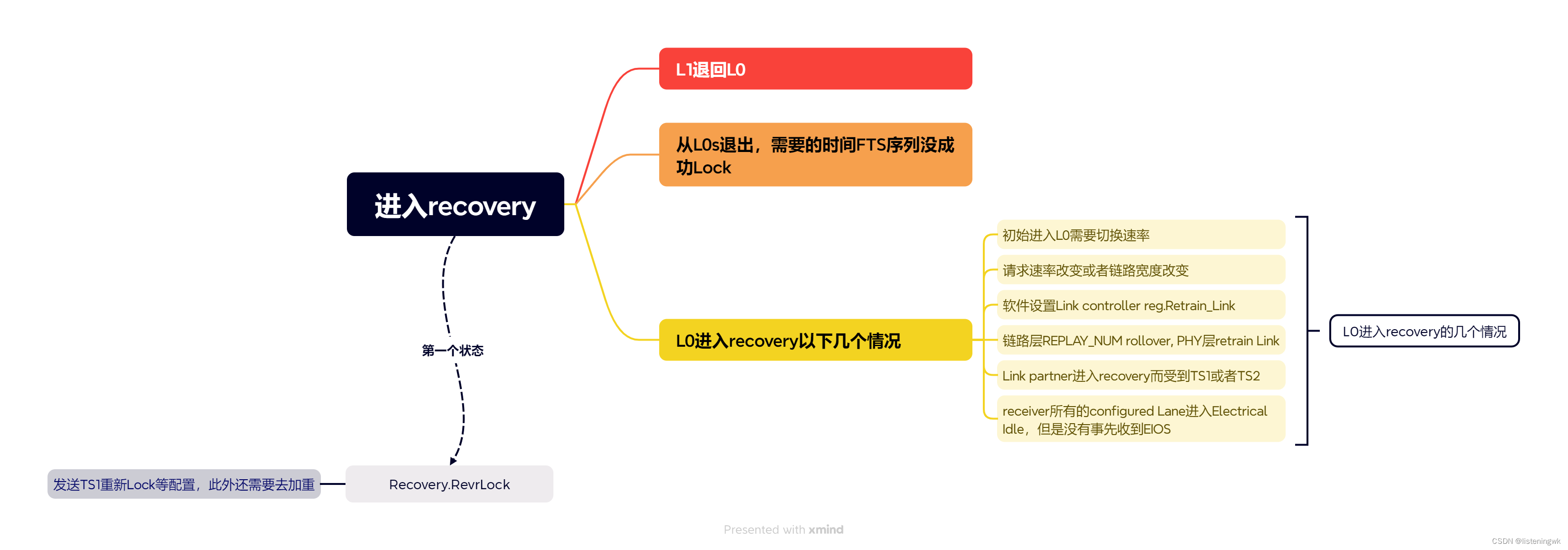

恢复状态recovery:当链路需要重训练时,进入recovery状态。可能原因:L0状态中发生了错误、从L1低功耗状态恢复到L0状态、从L0s状态恢复到L0时,无法通过FTS序列重新完成训练。该状态下会重新进行bit和字符/块锁定,方法是和polling时候一样,一般来说,此次更快。

L0s状态:L0s是一个由硬件控制的ASPM低功耗状态,L0s状态的目标是在节约一定功耗的同时,能够快速地恢复到L0状态。进入方式:L0状态下,链路一方发送EIOS。退出L0s:会通过FTS序列重新完成bit和字符/块锁定。

L1状态:L1状态能够比L0s状态降低更多的功耗,代价在于需要更长时间恢复到L0状态。进入L1状态需要链路双方进行协商,并一起进入。进入L1方式:

其一,ASPM控制下,自动进入L1。如上游端口没有DLLP或者TLP包时候,硬件自动与下游端口协商,链路一起转向L1状态。如果下游同意,那么链路进入L1状态,否则上游端口将单方面进入L0s状态。

其二,功耗管理软件命令设备进入低功耗状态。上游端口通知下游端口,下游端口响应通知,链路进入L1。

对比L0s和L1:

L1需要双方协商,链路状态才能到达L1,但是L0s可以单方面进入;

L0s快速恢复,L1恢复相对较慢;

L1功耗更低;

L2状态:更显著功耗节约状态;

回环状态loopback:测试状态;目的是验证链路完整性。

禁用状态(disable):链路配置为禁用状态;发送逻辑为电气空闲,接收逻辑为低阻状态。

热复位状态(hot reset):桥控制寄存器配置次级总线复位bit,复位链路。

四、详细次状态

(一)detect

(二)polling

(三)configuration

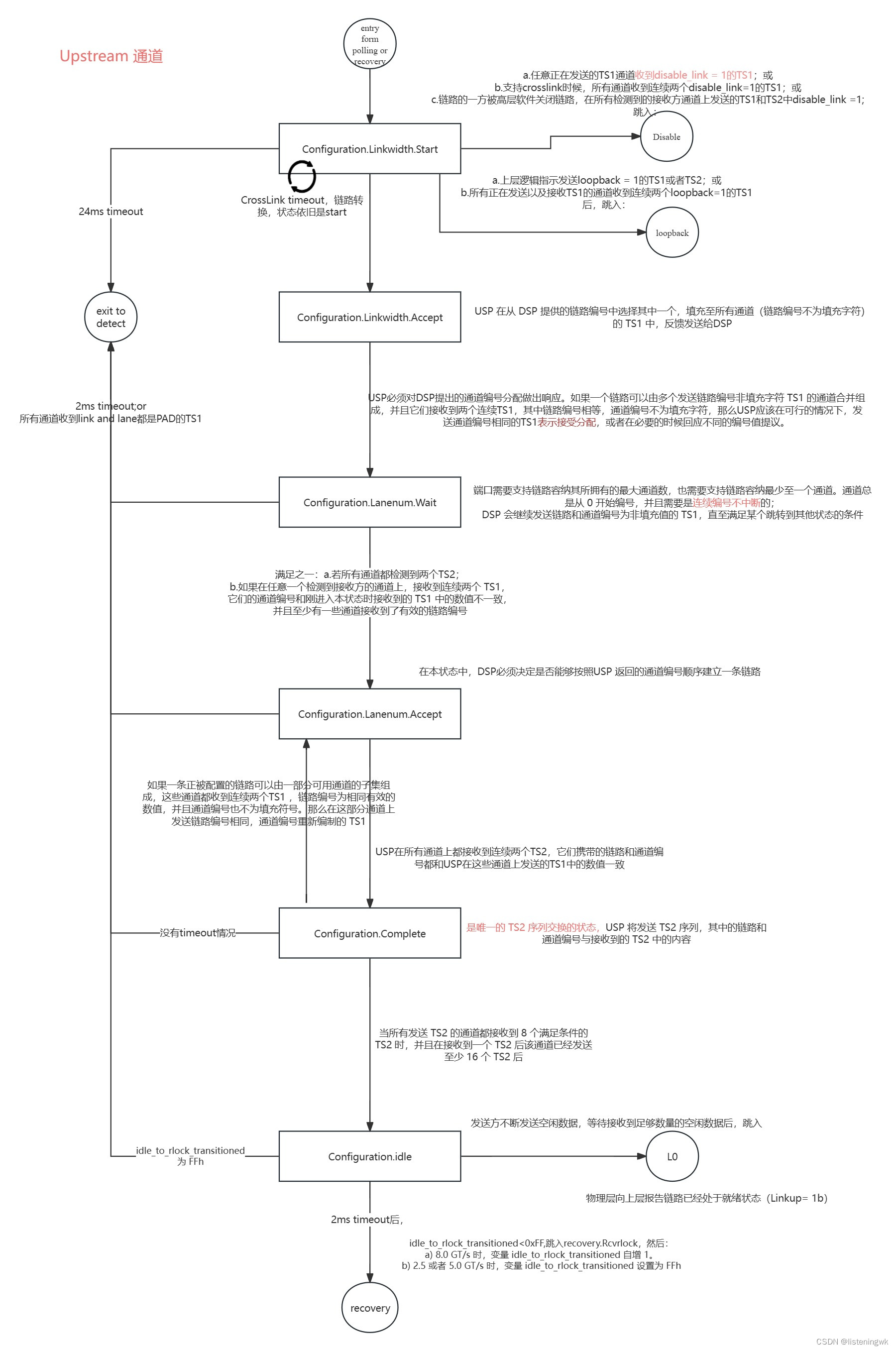

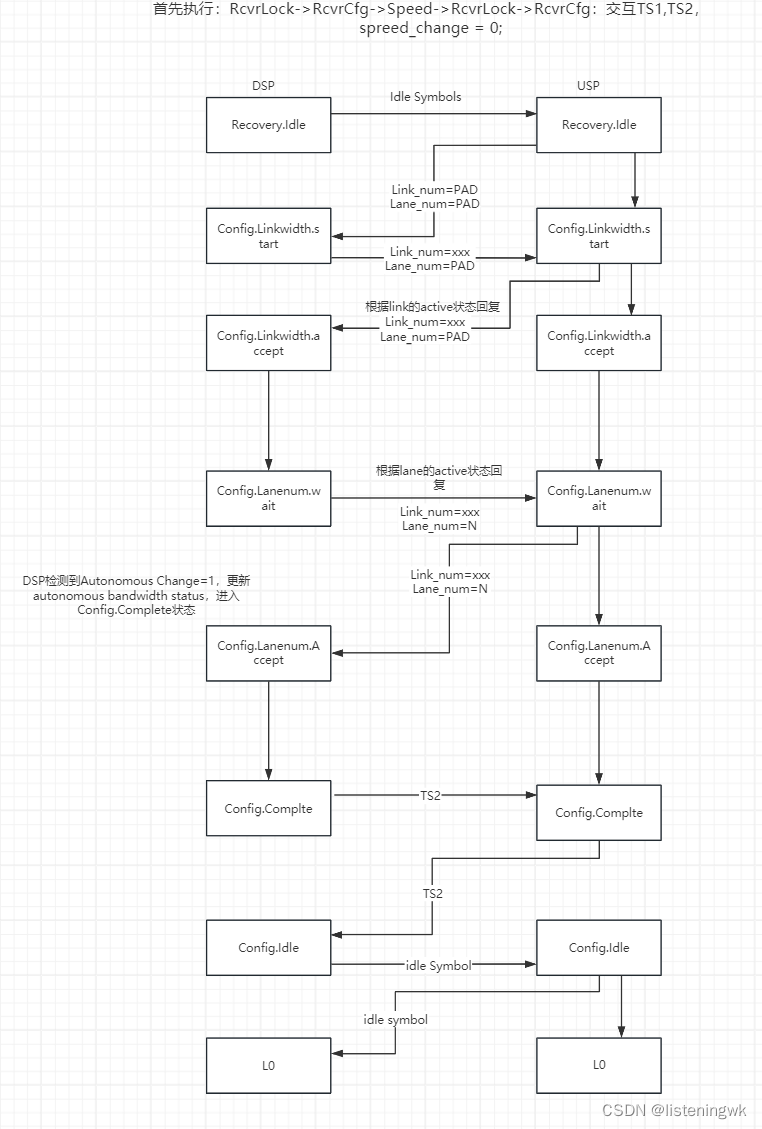

本状态目标主要是弄清楚设备端口(port)和各个通道(lane)的连接情况,以及为连接的通道分配编号。

端口在此状态下分面向上游端口和面向下游端口,这是两个不同的端口。配置过程也会根据上游端口和下游端口行为进行讨论。

DSP(downstream Port)端口在链路中是扮演“领导者”,USP(upstream port)端口是跟随者。

configuration状态训练过程分析

具体分析见下图:

(四)L0

L0状态介绍可以参考此处。

总结L0状态:

链路的全功能正常工作状态。实际使用时候,判断链路正常与否就是看进入L0状态。L0进入L0s和L1、L2,进入低功耗状态。L0若进入recovery,可能是切换速率或者链路宽度(lane)。

(五)recovery

比较常见进入recovery状态场景:

1 切换速率

2 切换链路宽度

3 链路需要重新EQ

具体可以参考此文,介绍比较详细。

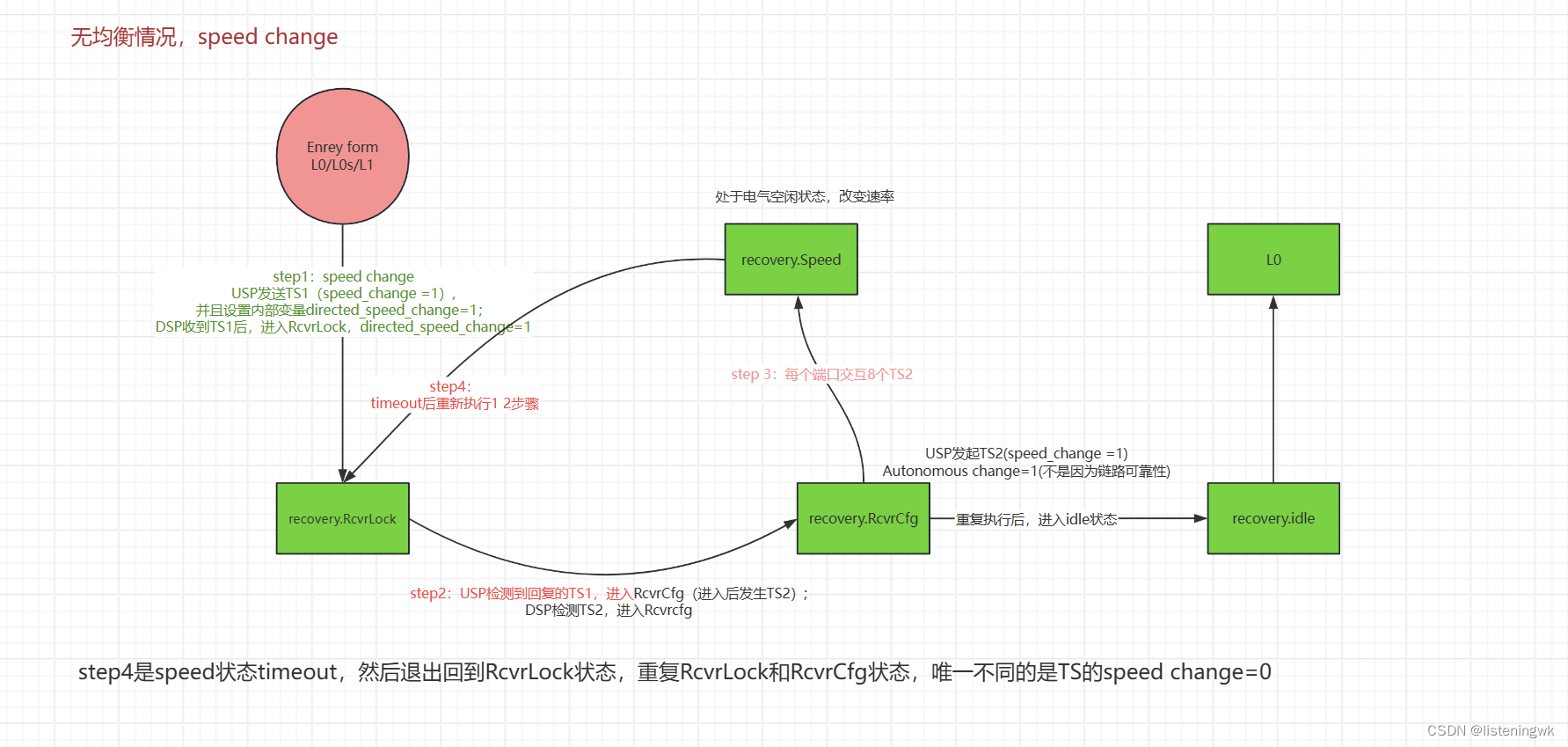

5.1 speed change

链路切换的流程图如下,具体叙述可以参考知乎链接的文章。

软件控制speed change

涉及到两个寄存器:Link controller 2 reg和Link controller reg

预先处理如下:Link controller 2 reg->Target_Link_Speed支持最高速率;

Link controller reg->retrain_link置1

流程和上述一样。

5.2 linkwidth change

9225

9225

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?