PCIe Link Initialization and Training Process

PCIe 链路初始化及训练是由物理层控制的硬件过程。该过程对设备的端口及链路进行配置及初始化,从而能够支持后续的数据传递。

复位之后,硬件会开始链路训练流程,并且流程由 LTSSM(Link Training and Status Machine)管理。LTSSM 的位置如下图所示:

链路初始化及训练过程会对进行许多配置,可能会涉及到以下内容:

-

Bit Lock:当链路训练开始时,接收设备的时钟尚未与发送设备的传输时钟同步,无法可靠地对传入的数据进行采样。在链路训练过程中,接收设备的 CDR (Clock and Data Recovery)从收到的比特流中复原出一个时钟作为参考时钟。一旦接收设备成功复原了时钟,就可以说接收设备已经获取到了 Bit Lock,此时接收端已经可以有效的对收到的比特流进行采样。

-

Symbol Lock:对于 8b/10b 编码(即 PCIe Gen1 或 Gen2),获取 Bit Lock 之后就需要获取 Symbol Lock。在获取到 Bit Lock 后,虽然接收端能够对比特流进行完整采样,但是它不知道 10 bit 的符号边界在哪里。在 TS1 和 TS2 进行交换时,接收端会在比特流中搜索能够识别的 pattern。最简单的就是识别 COM Symbol,它独特的编码方式使其易于识别,而且它也标识了 Symbol 和 Ordered Set 的边界。

-

Block Lock:在 PCIe Gen 3 中不再使用 8b/10b 编码,没有 COM 符号,因此 Symbol Lock 就不能用了。为了能够识别到数据包的边界,需要在链路训练流程中加入更多的 EIEOS (Electrical Idle Exit Ordered Set) 实例。EIEOS 被识别为一系列交替的 00h 和 FFh 字节,它定义了 Block 的边界。

-

Link Width:每个设备支持的 lane 数量不一定相同,所以在链路训练过程中,发送端和接收端会对不同的 lane 进行测试,最终选择一个可用的最大值。

-

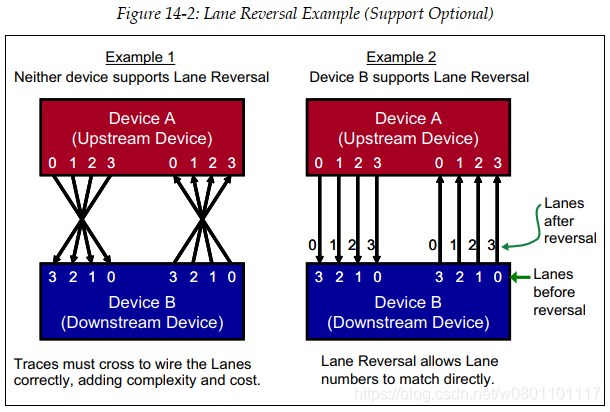

Lane Reversal:对于包含多个 lane 的设备,都是从 lane 0 开始顺序编号。一般情况下,两个 PCIe 设备相连时都是 lane 0 接 lane 0,lane 1 接 lane 1,以此类推。但是,有些场景中,为了简化 PCB 的布线,需要从逻辑上反转 lane 的编号,从而避免在 PCB 交错布线。只要一个设备支持 Lane Reversal 就可以。首先,一个设备在内部反转 lane 的编号,然后在链路训练时会检测到 lane 编号被反转。鉴于 Lane Reversal 并不是 PCIe 协议规定必须支持的特性,所以硬件设计人员在设计板级电路时需要确认 PCIe 发送设备或者接收设备的其中一个支持 Lane Reversal 特性之后才能按照非交错方式布线。下图展示了 Lane Reversal 的效果:

-

Polarity Inversion:PCIe 协议规定,必须支持该特性。该特性的目标也是为了简化 PCB 的布线。每个 lane 都包含一组发送(Tx)和接收(Rx),而 Tx 和 Rx 分别包含两根差分信号线(D+ 和 D-)。Polarity Inversion 的作用就是把某个设备的 D+ 变成 D-,D- 变成 D+。开启 Polarity Inversion 之后的效果如下图所示:

-

Link Data Rate:复位之后,默认会在 2.5 Gbit/s 的速度模式下进行链路初始化及训练。如果支持更高的速度,那么会在链路训练过程中进行声明。在链路训练完成后,设备会再进行一次快速链路训练切换到支持的最快传输速度上(5.0 Gbit/s, 8.0 Gbit/s 等等)。

-

Lane-to-Lane De-skew:对于包含多个 lane 的设备,数据传输是在所有 lane 上并行传输的。由于种种原因,很难保证每个 lane 上的数据在同一时刻到达接收设备,这种现象称为 signal skew。接收设备为了应对 signal skew,需要让早到的数据等一会,等其他 lane 的 bit 流数据一起到了之后一起处理。接收设备必须能够自动的处理这些 skew ( 2.5 Gbit/s 传输速度下,可以允许到达时间相差 20 ns)。这个特性能有效 PCB 布线的难度,因为这个机制能放宽等长布线的要求。lane 与 lane 的长度有些许的差异也不会造成信号传输问题。结合之前的 Lane Reversal、Polarity Inversion 特性,一定程度上降低了高速 PCB 的设计的难度。

8472

8472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?