PCIe link 协议:

本部分主要目的是host在识别枚举PCIe设备之前,设备与主机在PCIe链路上都发生了什么事情,,主要流程为上电后两侧根据PCIe总线协议进入LTSSM流程,主要分为以下几个方面去介绍:

1,什么是 symbol lock和bit lock

PCIe总线的的接收端链路上没有时钟,因此获取时钟的办法是通过接收到发送端发过来的报文信息(带有时钟信息)来获取时钟信息,将此过程称之为bit lock,同理symbol lock表示PCIe链路上获取开始训练的标记符COM字符的过程。

2,LTSSM流程介绍

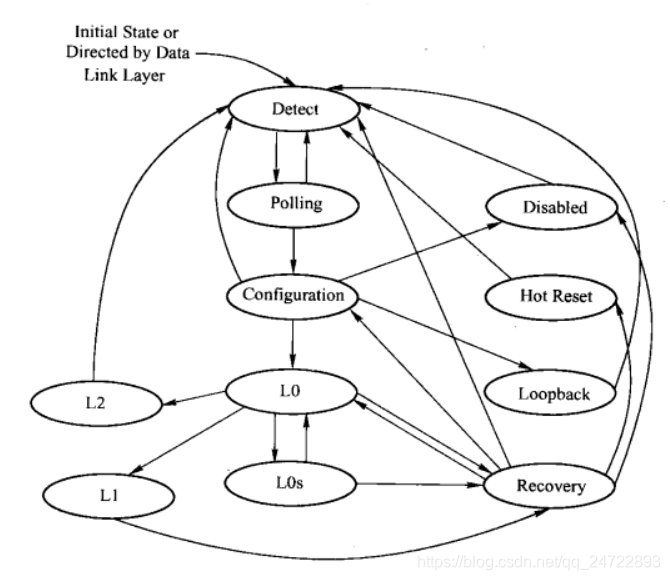

PCIe总线在硬件训练的过程中主要使用这几个序列:TS1、TS2,这两个序列主要作用是在LTSSM状态机之间来回跳转。FTS序列协助PCIe的链路获取bit lock和symbol lock。SKIP序列负责处理各个lane上面的skew,使其保持一致,具体技术细节可参考elastic buffer技术。整个训练过程pcie链路使用默认gen1速率进行传输,LTSSM状态机精简流程如下:

detect <------->polling------config------L0状态(主机可以枚举到device侧设备)

2.1 detect状态

此部分主要的作用是用来确认PCIe链路上可以正常工作的lane资源

detect.quiet<----->detect.

本文详细介绍了PCIe链路训练的过程,包括Detect、Polling、Config和L0状态,重点讲解了symbol lock、bit lock以及LTSSM状态机的工作原理。在Detect状态中,设备和主机确认lane资源;Polling状态负责获取锁并同步链路;Config状态完成主要配置,包括lane deskew;L0状态则是链路正常工作状态。

本文详细介绍了PCIe链路训练的过程,包括Detect、Polling、Config和L0状态,重点讲解了symbol lock、bit lock以及LTSSM状态机的工作原理。在Detect状态中,设备和主机确认lane资源;Polling状态负责获取锁并同步链路;Config状态完成主要配置,包括lane deskew;L0状态则是链路正常工作状态。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2467

2467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?