迄今为止讲的最好的D触发器

转载自www.runoob.com

https://www.runoob.com/w3cnote/verilog2-gate-delay.html

D 触发器

下面从门级建模的角度,对 D 触发器进行设计。

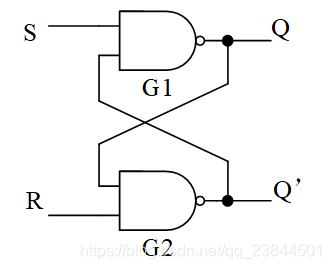

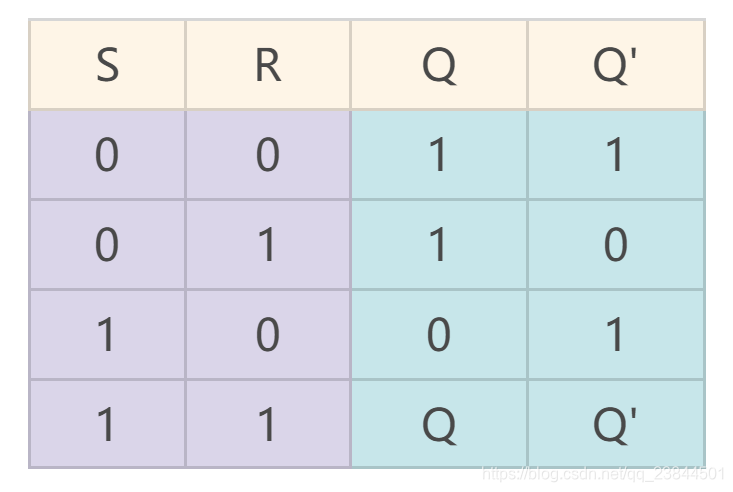

SR 触发器

SR 触发器结构图及真值表如下所示。

1、当 S 为低电平,G1 输出端 Q 为高电平,并反馈到 G2 输入端。如果此时 R 为高电平,则 G2 输出端 Q’ 为低电平。

2、R 为低电平 S 为高电平时,分析同理。

3、S 与 R 均为高电平时,如果 Q = 1 (Q’ = 0) , 则 Q 反馈到 G2 输入端后输出 Q’ 仍然为 0, Q’ 反馈到 G1 输入端后输出 Q 仍然是 1,呈现稳态。如果 Q =0 (Q’ = 1) 同理,Q 与 Q’ 的值仍然会保持不变。即 S 与 R 均为高电平时该电路具有保持的功能。

4、如果 S 与 R 均为低电平,则输出 Q 与 Q’ 均为高电平,不再成互补的关系。所以此种情况是禁止出现的。

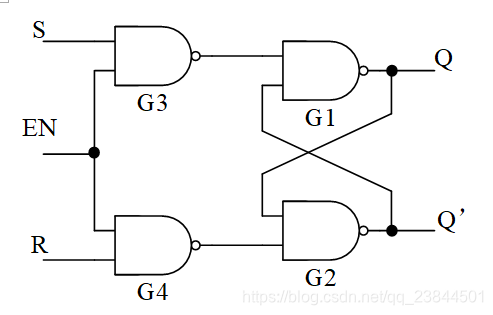

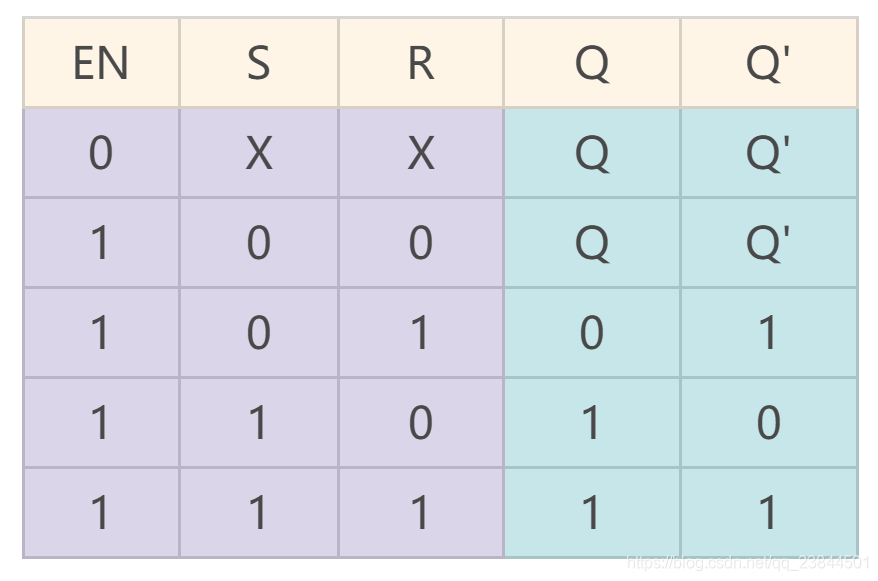

SR 锁存器

在基本的 SR 触发器前面增加 2 个与非门,可构成带有控制端 SR 锁存器。

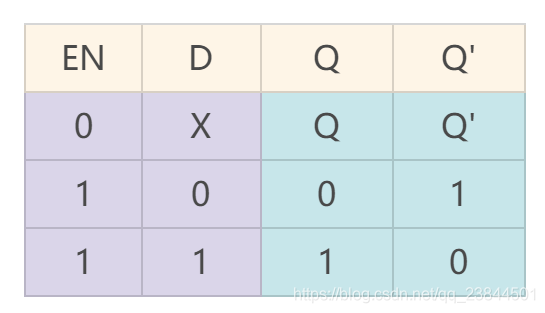

SR 锁存器及其真值表如下所示。

当 EN=0 时,G3、G4 截止,SR 锁存器保持输出状态不变。

当 EN=1 时,与基本的 SR 触发器工作原理完全相同。

D 锁存器

基本的 SR 触发器输入端不能同时为 0, 带有控制端的 SR 锁存器输入端不能同时为 1,否则会导致输出端 Q 与 Q’ 的非互补性矛盾。

为消除此种不允许的状态,在带有控制端的 SR 锁存器结构中加入取反模块,保证 2 个输入端均为相反逻辑,则形成了 D 锁存器。

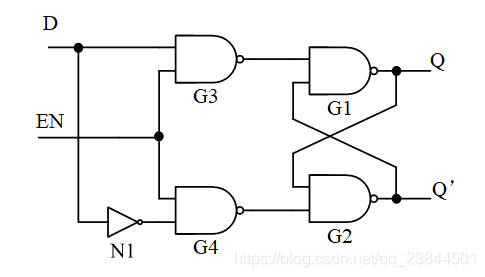

其结构图和真值表如下所示。

1、当 EN=1 时,输出状态随输入状态的改变而改变。

2、当 EN=0 时,输出状态保持不变。

D 锁存器是一种电平触发。

如果在 EN=1 的有效时间内,D 端信号发生多次翻转,则输出端 Q 也会发生多次翻转。这降低了电路的抗干扰能力,不是实际所需求的安全电路。

为提高触发器的可靠性,增强电路抗干扰能力,发明了在特定时刻锁存信号的 D 触发器。

D 触发器

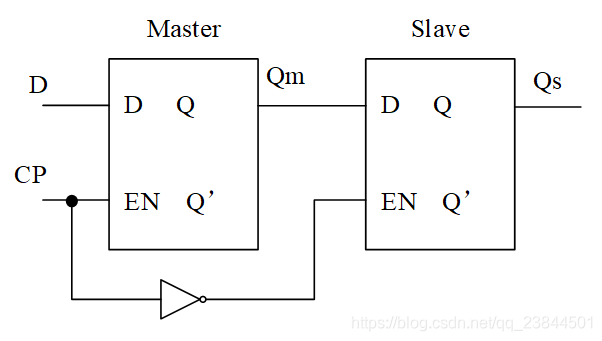

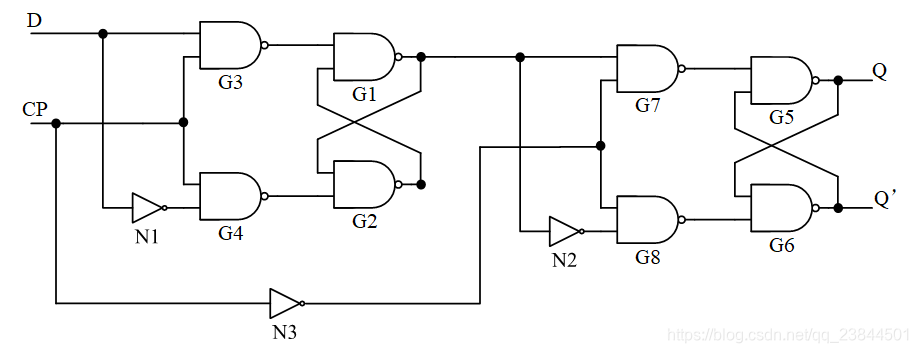

将两个 D 锁存器进行级联,时钟取反,便构成了一种简单的 D 触发器,又名 Flip-flop。

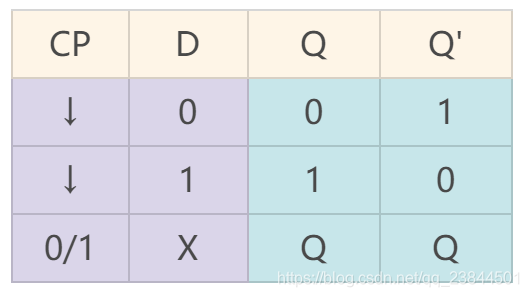

其结构图和真值表如下所示。

第一级 D 锁存器又称为主锁存器,在 CP 为低电平时锁存。第二级 D 锁存器又称为从锁存器,时钟较主锁存器相反,在 CP 为高电平时锁存。

1、CP=1 时,主锁存器输出端 Qm 会和 D 端信号的变化保持一致,而从锁存器处于保持状态,输出 Qs 保持不变。

2、CP由高电平变为低电平时,主锁存器锁存当前 D 的状态,传递到输出端 Qm 并保持不变。而从锁存器输出端 Qs 会和 Qm 的变化保持一致。此时处于锁存状态下的主锁存器输出端 Qm 会保持不变,所以 D 触发器输出端 Qs 端得到新的 Qm 值后, 也会保持不变。

综上所述,D 触发器输出端 Qs 只会在时钟 CP 下降沿对 D 端进行信号的锁存,其余时间输出端信号具有保持的功能。

将双级 D 锁存器展开为门级结构,如下图所示。

3520

3520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?