本来只想做一下序列信号发生器的手撕代码,但是综合之后看了一下生成的原理图,觉得无法理解,就研究了一下。

序列信号发生器很简单,我用移位实现的,代码如下

module xuliexinhao(

input sys_clk, //时钟

input sys_rst_n, //复位,低有效

input [9:0] in, //待输出序列

output reg out //输出

);

reg [9:0] data;

always @(posedge sys_clk,negedge sys_rst_n) begin

if (!sys_rst_n) begin

out <= 0;

data <= in;

end

else begin

out <= data[9];

data <= {data[8:0],data[9]};

end

end

endmodule这个没有什么好说的很简单,再仿真例化一下就行了,就不贴代码了。

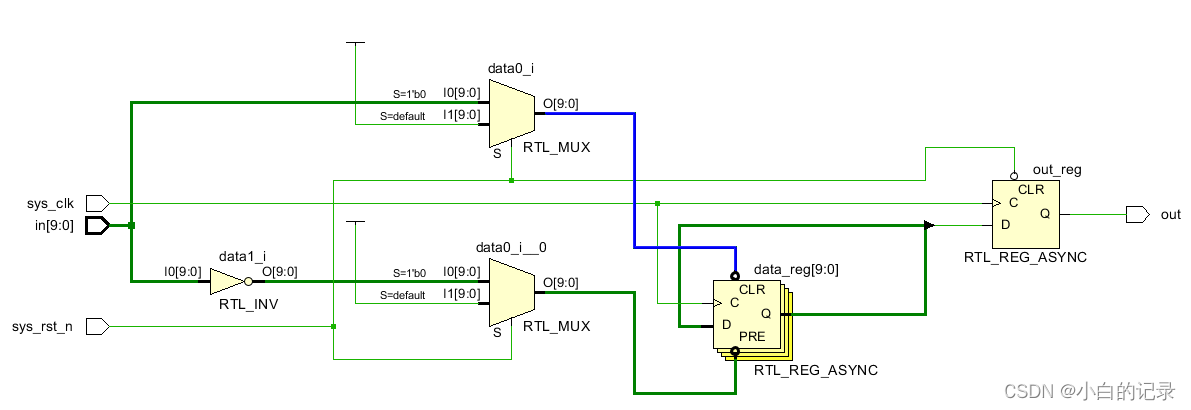

但是这个生成的电路图是这样的

难点在于我不理解异步置位,即data寄存器的PRE引脚,对D触发器的异步置位和异步复位讲解的文章不多,所以就写一下。在这里要知道D触发器特性,CLR是异步复位,PRE是异步置位&

本文探讨了D触发器的异步复位和异步置位特性,通过序列信号发生器的实现来分析。作者指出,CLR为异步复位,PRE为异步置位,低电平有效,且CLR优先级高于PRE。当CLR为0时,Q立即输出0;当CLR为1且PRE为0时,Q输出1。文章还解释了复位信号如何通过二选一选择器影响D触发器,并提醒读者网上的相关资料可能存在错误,欢迎纠正。

本文探讨了D触发器的异步复位和异步置位特性,通过序列信号发生器的实现来分析。作者指出,CLR为异步复位,PRE为异步置位,低电平有效,且CLR优先级高于PRE。当CLR为0时,Q立即输出0;当CLR为1且PRE为0时,Q输出1。文章还解释了复位信号如何通过二选一选择器影响D触发器,并提醒读者网上的相关资料可能存在错误,欢迎纠正。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

867

867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?