xilinx zynq(二)

四、Zynq GPIO介绍

4.1. Zynq GPIO介绍

GPIO英文全称General-Purpose Input/Output Ports.

GPIO至少包含两个寄存器,控制(GPxCON)和数据(GPxDAT)。

4.2. Zynq 寄存器

XC7Z020 GPIO由4个Bank组成,共54个I/O,54个MIO由PS控制:

Bank0有32个GPIO引脚;

BANK1有22个GPIO引脚;

BANK2和BANK3通过EMIO接口将CPU的GPIO连接到PL部分引脚上。

五、Zynq 中断

5.1. 中断原理

ARM体系中通常会在存储地址的地段固化一个32字节硬件中断向量表,用来指定各中断和中断处理程序。从中断处理程序退出时,要恢复被中断的程序现场。

当一个中断发生,ARM微处理器一般会处理几步:

保存处理器当前状态、中断屏蔽位一级各条件标志位;

设置当前程序状态寄存器CPSR中相应的位;

将寄存器lr_mode设置成返回地址;

将程序计数器(PC)值设置成该中断向量的地址,从而跳转到相应的中断处理处去执行;

执行中断;

从中断程序中返回,恢复屏蔽的程序处理器状态;

返回到发生中断的指令的下一条指令处继续执行。

5.2. 中断分类

ARM体系中断种类:

复位;

数据访问终止;

快速中断请求;

外部中断请求;

预取指令终止;

软件中断;

未定义的指令;

Zynq中断类型包括:

5个私有中断(Private Peripheral Interrupt);

16个软件中断(Software Generated Interrupt);

64个共享外设中断(Shared Peripheral Interrupt);

通用中断控制器是核心资源,用于管理PS或者PL的中断。

5.3. 中断向量表

ARM处理器响应中断时候,首先是从固定地址的中断向量表开始。

5.3. Zynq中断程序设计实现

Zynq中断编程主要包含7方面:

设置中断向量表和解析程序;

对中断源进行配置;

中断分配器初始化;

中断控制器初始化;

中断分配器配置;

CPSR(ARM程序状态寄存器)寄存器配置;

中断服务程序设计。

六、Zynq 定时器

6.1. 概述

Zynq中每个Cortex-A9处理器都有自己私有32位定时器和32位看门狗定时器。

定时器计算公式:

时间间隔 = [ (预分频的值 + 1)(加载值 + 1)] / 该定时器频率

七、Zynq UART

7.1. 概述

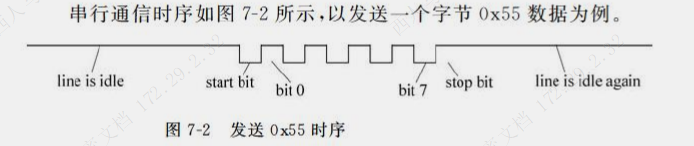

通用异步收发器(UART)是一种通用串行数据总线,用于异步通信。可实现全双工传输和接收。

0x55的二进制码为:01010101

7.2. 框图

可编程波特率发生器;

64个字节接收和发送FIFO;

支持产生中断;

比特率发生器

UART 寄存器

(slcr )UART_CLK_CTRL:UART时钟控制寄存器;

mode_reg0:设置UART数据格式寄存器;

Baud_rate_divider_reg:UART波特率发生器BDIV寄存器;

Channel_sts_reg:查询UART各种状态寄存器,如FIFO是否满状态;

TX_RX_FIFO:发送接收FIFO寄存器

感谢阅读,祝君成功!

-by aiziyou

948

948

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?