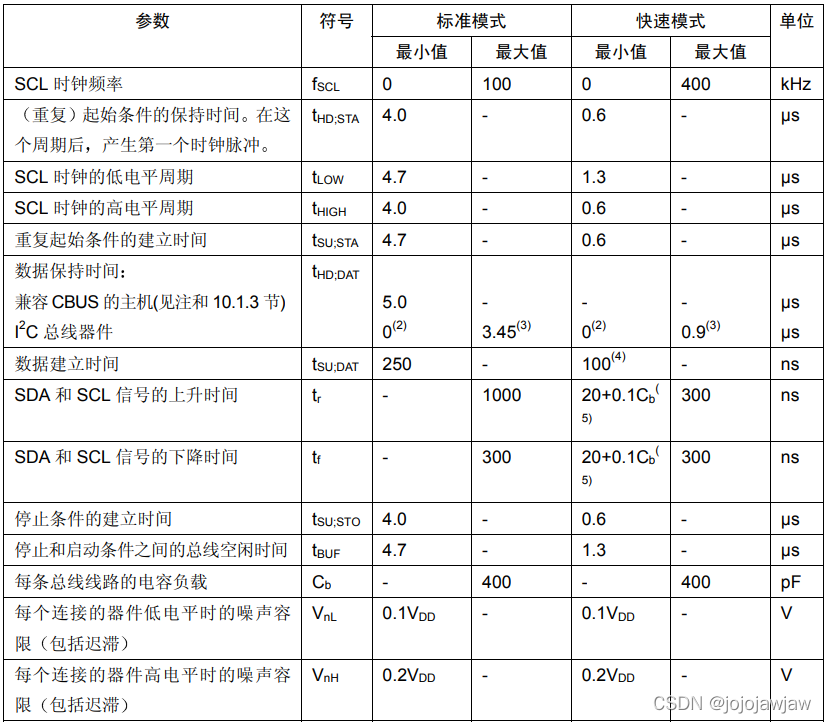

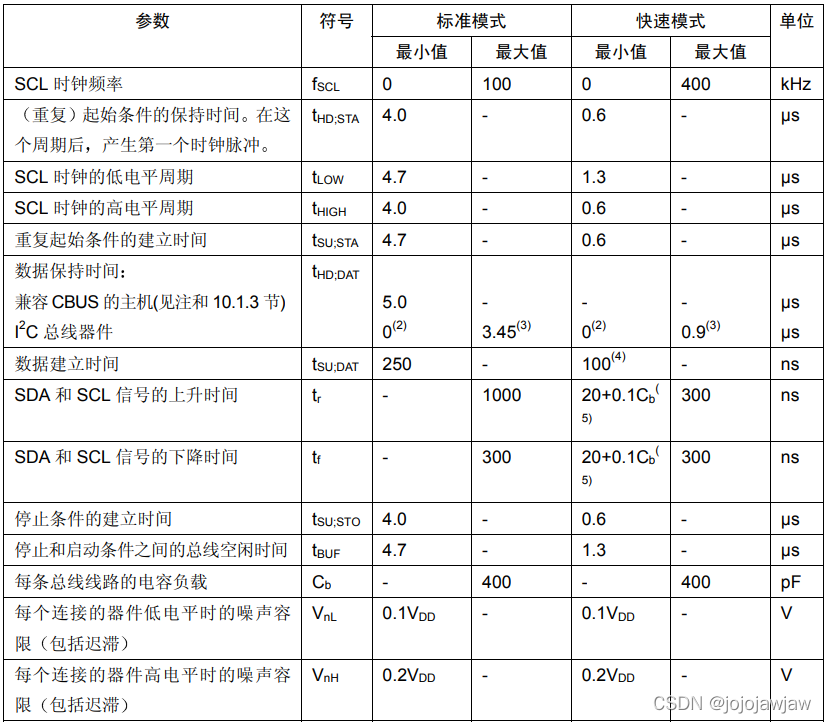

时序图大家可以对照手册来看,出现问题时大多是由于scl和sck保持时间有问题导致NACK

IIC原理超详细讲解---值得一看 大佬对于IIC原理讲解的很细致,推荐大家看一下。

下面结合几个示例给大家一个清晰的理解

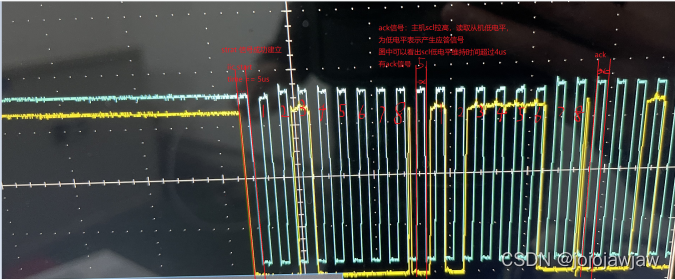

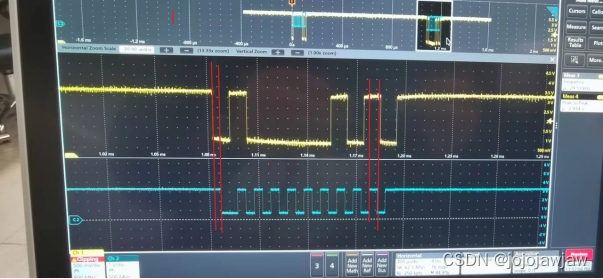

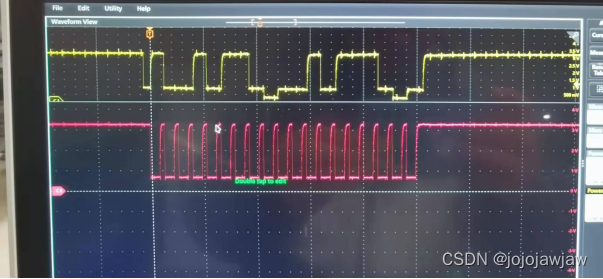

1、正常时序波形

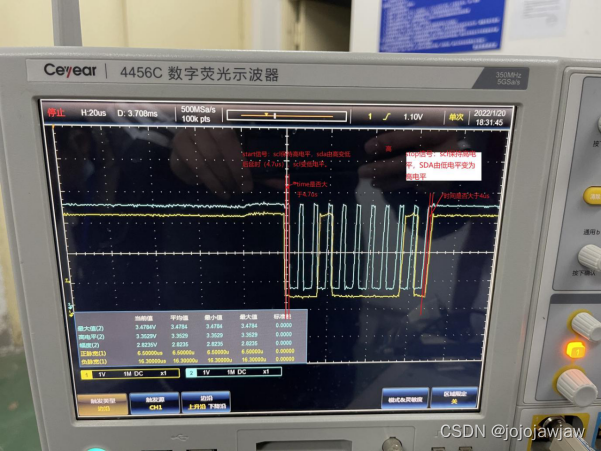

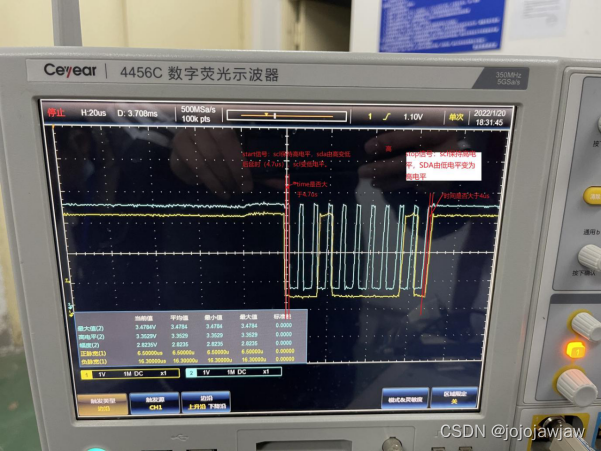

2、start 信号时序sda延时不够,导致NACK

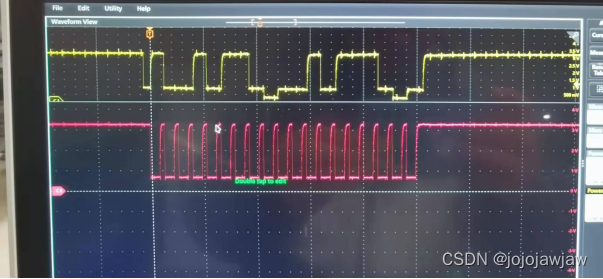

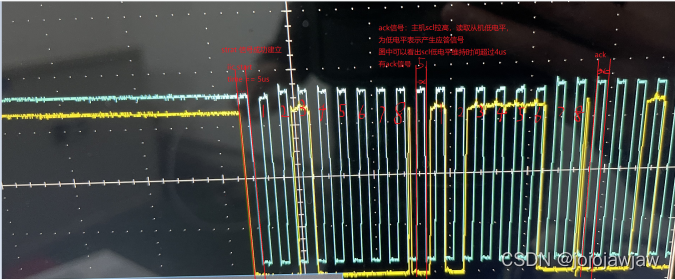

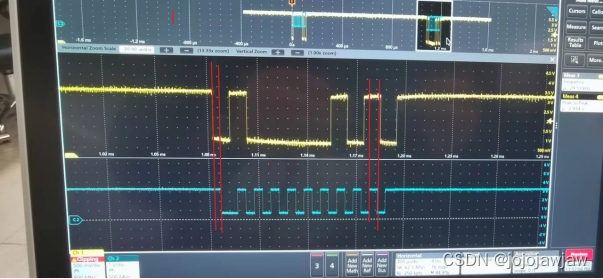

3、sck高电平时间维持太短,导致NACK

4、start 信号时序sda延时不够,导致NACK

时序图大家可以对照手册来看,出现问题时大多是由于scl和sck保持时间有问题导致NACK

IIC原理超详细讲解---值得一看 大佬对于IIC原理讲解的很细致,推荐大家看一下。

下面结合几个示例给大家一个清晰的理解

1、正常时序波形

2、start 信号时序sda延时不够,导致NACK

3、sck高电平时间维持太短,导致NACK

4、start 信号时序sda延时不够,导致NACK

2万+

2万+

2万+

2万+

8053

8053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?