解释完带宽这一概念,我们来考虑如何才能通过仿真准确的预测信号完整性。

信号带宽的确定、器件模型的获取

当我们确定了要分析的信号的信息(包含速率、接口电平、上升时间等等)、以及驱动器和接收器型号之后,我们就可以计算得到信号的带宽。一般来说芯片厂家提供的仿真模型无论是IBIS还是Spice模型都是很信号带宽相匹配的。比如说一个器件的IBIS模型中肯定不会包含serdes信号的模型,如果器件中有serdes接口厂家肯定会提供Spice或者IBIS-AMI模型供仿真使用。也就是说芯片厂家提供的仿真模型的带宽一般情况下要比模型中包含的信号带宽要高,我们是可以放心使用的。

无源链路的建模

对于无源链路需要工程师借助仿真软件进行建模。第一,建模的过程中必须保证模型的准确度,也就是模型必须能够准确的反映无源链路的真实特征。这就要求SI工程师能够根据所设计的总线接口的特性选择合适的仿真建模方法以及软件工具。第二,无源链路的性能要能够满足信号带宽的要求。SI工程师需要通过对模型进行仿真优化使模型在信号的带宽范围内具有良好的损耗和反射性能,如果无源链路的性能不能满足要求,工程师就需要对无源链路的材料或者结构进行调整以提高模型带宽。

第一点就是保证模型的准确,保证使用这个模型进行仿真的结果和实际测试结果的偏差可控。第二点包含的意思就是我们需要通过对无源链路的优化来达到信号完整性最优的效果。如果无源链路的模型带宽太低会出现什么情况呢?

为了解释这个问题,我们再来看一下带宽的计算公式:BW= 0.35/Trise,可以导出Trise = 0.35/BW。应用在互连线模型中,Trise就代表了互连线的本征上升时间。互连线的带宽为1GHz,那么它能传输信号的最短上升时间就是350ps,这个350ps就是这条互连线的本征上升时间。驱动器输出一个上升时间为Trise_drv的信号输入到一条本征上升时间为Trise_interconnect的互连线,在接收器处接收到的信号上升时间为Trise_rev,则有如下关系:

不难看出,由于互连线的本征上升时间导致接收器接收到的信号上升时间Trise_rev相对于Trise_drv增大了,我们通常也说信号经过互连线传输之后发生了边沿退化。如果互连线的带宽太低,其本征上升时间就会比较长,那么接收器接收到的信号上升时间就会比较大,也就是说信号在传输过程中发生的边沿退化就越严重。

测试设备的带宽和本征上升时间

同样,在使用测试设备对接收器的信号进行测量时也会有上升时间的退化问题。一般来说示波器和测试探头都有自身的带宽和本征上升时间,以此来描述它所能测试信号的最高带宽和最短上升时间。接收器上升时间为Trise_rev的信号,通过本征上升时间为Trise_probe的探头在示波器上显示测试波形的上升时间为Trise_measure

也就是说当示波器、探头的带宽很低时,其本征上升时间就会比较长,测试到的信号上升时间也就比实际信号上升时间要长。这样的话很可能会错过实际信号的一些细节特征得到错误的结论。

如果测试结果没有能够测到实际存在在上边沿上的台阶、回沟,这对时钟信号来说是致命的,因为回沟会导致时钟对数据信号的误采样。我们在进行时序测试也会导致我们得到错误的建立保持时间裕量;也可能导致测试到的信号过冲、振铃幅度比实际的过冲和振铃要小,很可能实际信号的过冲以及超过了芯片手册的要求这样会影响器件寿命,也有可能实际信号的振铃已经严重的影响了信号的噪声裕量,在恶劣情况下很容易导致数据错误。等等这些都是产品开发中的隐患。由此可见正确的对信号进行仿真预测和测量验证有着非常重要的意义。

什么是高速信号

通过上面关于时域、频域的转换以及信号、互连线带宽的分析,我们现在就可以理解什么是高速信号了。高速信号并不等于高频信号,信号是不是高速信号关键要看信号的带宽,也就是信号的上升时间是否足够短。而信号的上升时间和信号频率之间并没有必然的关系系,唯一的关系就是信号的上升时间肯定要小于信号周期的50%。当信号的频率达到5GHz、10GHz时,其上升时间必然会小于100ps、50ps,此时信号的带宽必然会很高,无疑这种信号就是高速信号,其信号完整性问题就会非常突出。但是对于一个频率仅为1MHz的信号,我们能否就说它不是高速信号呢?当然不能,因为尽管芯片的频率很低,但是它的上升时间也可能非常小也可能是高速信号。

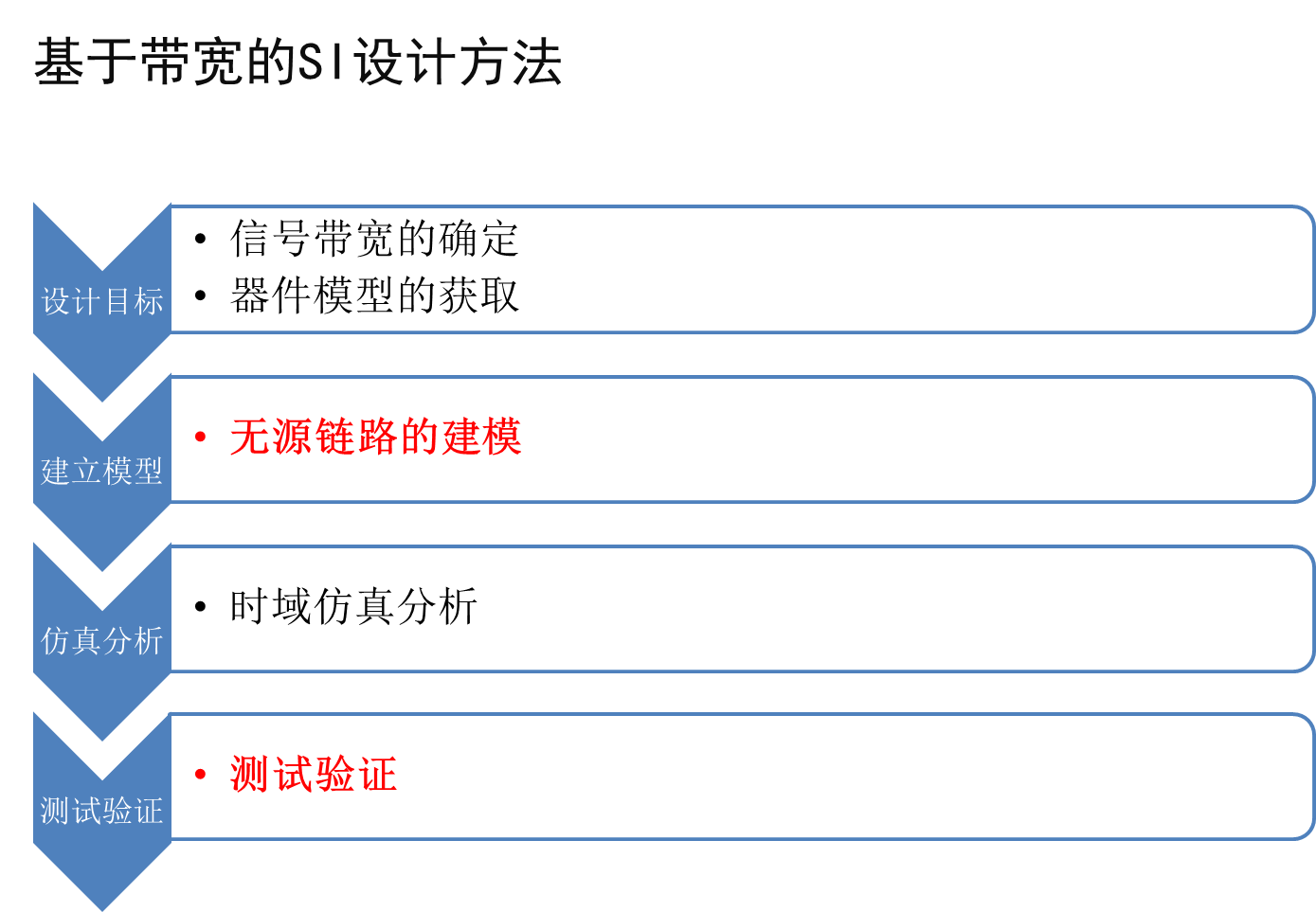

信号完整性的设计流程

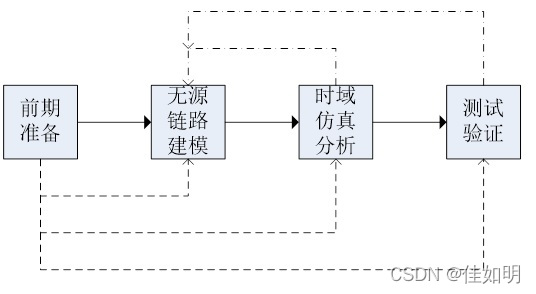

基于前两个章节的关于时域、频域以及带宽的介绍,我们这里对信号完整性分析设计流程进行归纳总结,整个过程大体可分为前期准备、无源链路建模、时域仿真分析、测试验证四个环节。其中前期准备是基础、无源链路建模和时域仿真分析是核心、并通过测试验证形成闭环。下面简要介绍这四个阶段所涉及到的主要工作内容,后续篇幅会针对高速并行总线、高速串行总线的信号完整性、以及电源完整性设计详细介绍设计流程。

SI分析设计流程图

前期准备

前期准备工作是通过对器件手册的研读和芯片仿真模型的分析得到仿真设计所需要的信息,主要包含: 信号或者电源的特性,包含时域波形和电流的大小、频谱特性等等,以及接收或者负载芯片对信号质量和电源噪声、压降等要求。并以此确定无源链路模型建立的方法、仿真分析的评判标准以及测试验证方案。

无源链路建模

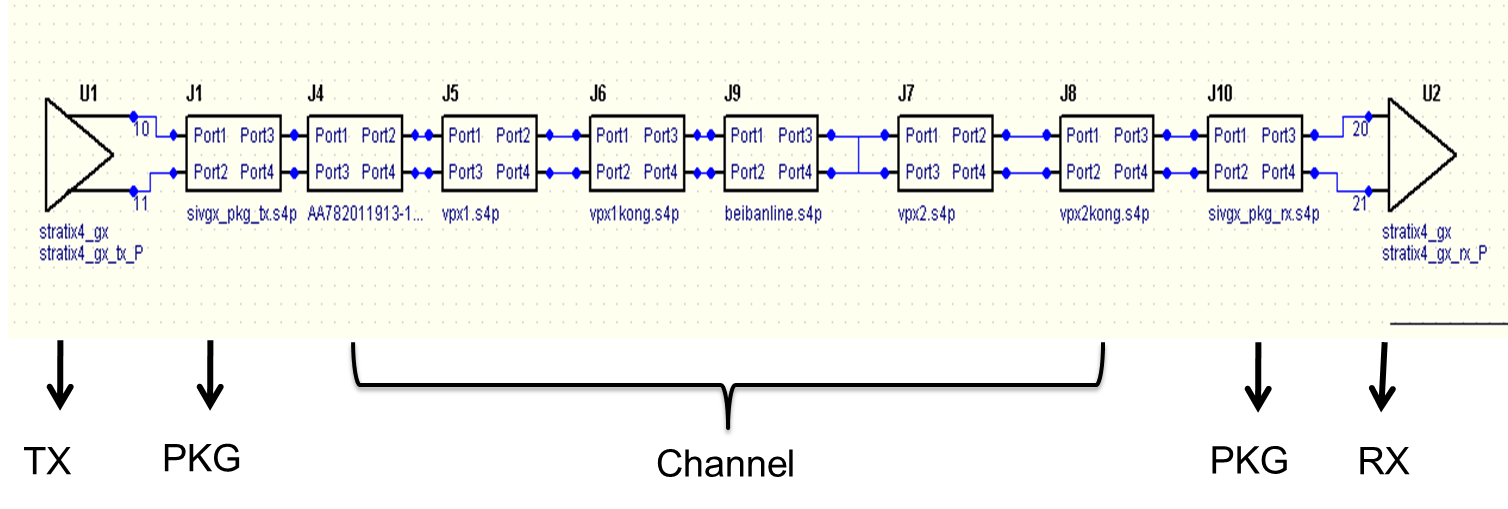

无源链路建模就是对信号传输路径进行建模优化,其目的就是为信号“安全”到达接收器件扫清障碍。信号完整性设计和电源完整性设计都需要对无源链路进行建模,但由于信号和电源对无源链路的要求不同,因此建模的关注点也有所不同。信号完整性关注链路的损耗、阻抗连续性,而电源完整性则要求PDN阻抗尽量低,主要关注各组成部分的寄生电感特性,并配合去耦电容消除电感影响。

同时无源链路建模的过程就是频域仿真的过程,通过无源链路的建模观察信号和电源无源传输路径的频域特性并对其进行优化使其满足设计要求。

时域仿真分析

时域仿真分析就是在无源模型上加入激励源进行仿真从而观测时域仿真结果。对于信号完整性仿真将芯片的有源模型(IBIS、Spice或者AMI模型)、传输路径的无源模型搭建成仿真电路,在驱动器端添加激励在接收器端直接观测信号波形和眼图,并对仿真结果进行分析。对于电源完整性则需要加入电流负载以及VRM模型仿真观测负载端的电源噪声。有些情况下无法获取芯片的电流模型,此时就不能进行精确的电源完整性时域仿真,此时要求PI频域仿真有足够的裕量,时域仿真也是可以缺省的。

时域仿真分析目的有两个:一是更加直观的判断信号、电源质量是否满足要求;二是确定芯片buffer选型、加重、均衡等各项参数配置为后续测试调试工作提供参考。

测试验证

测试验证是在产品生产完成后,在实际的系统中进行信号质量测试。测试验证的目的有两个,一是验证接收端信号质量是否满足要求;二是与前期的仿真结果进行对比进行差异分析,优化仿真建模方法。

测试验证要得到正确的测试结果需要注意以下事项:

- 根据信号带宽选择合适的示波器和探头;

测试点位置选择需靠近接收芯片管脚,往往选择PCB上的过孔。但我们选择的测试点并不是芯片实际的接收端,因此测试波形会受到封装内部布线的影响。此时需要使用“去嵌入”技术消除封装内部布线的影响。

31

31

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?