本期介绍的是德科技在DesignCon2017上发表的一篇paper--《Accurate Statistical-Based DDR4 Margin Estimation using SSN Induced Jitter Model》。虽说DDR4的数据速率较当前的DDR5、GDD6要低很多,但文章提出的关于SSN引入的抖动的分析方法值得借鉴。文章聚焦 DDR4 内存设计中的SSN开关噪声问题,针对传统统计模拟方法无法考虑 SSN 中 Delta-I 噪声的局限,提出通过瞬态仿真提取抖动模型和掩码校正因子的方法,以提高 DDR4 统计模拟的准确性,并且经实际验证该方法在 DDR4 设计中效果显著。

仿真方法面临的困境

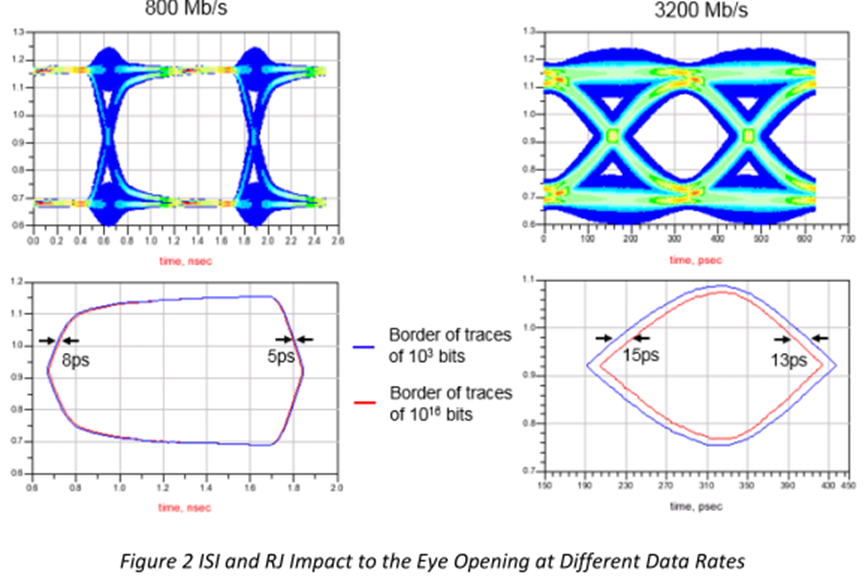

在低数据速率(800 Mb/s)下,符号间干扰(ISI)和随机抖动(RJ)引起的眼图收缩相对较小。而DDR4的速率达到3200Mbps,码间干扰和抖动的影响就不能再忽略,下图所示为800Mbps和3200Mbps数据速率的眼图仿真结果,可以看到ISI和抖动对3200Mbps信号影响更大。

仿真方法面临的困境:传统基于 SPICE 的时域仿真难以模拟大量比特数计算超低误码率(如1e-8,1e-16)下的眼图开口情况。统计仿真虽能快速获取超低误码率轮廓,但无法考虑 Delta-I 噪声。

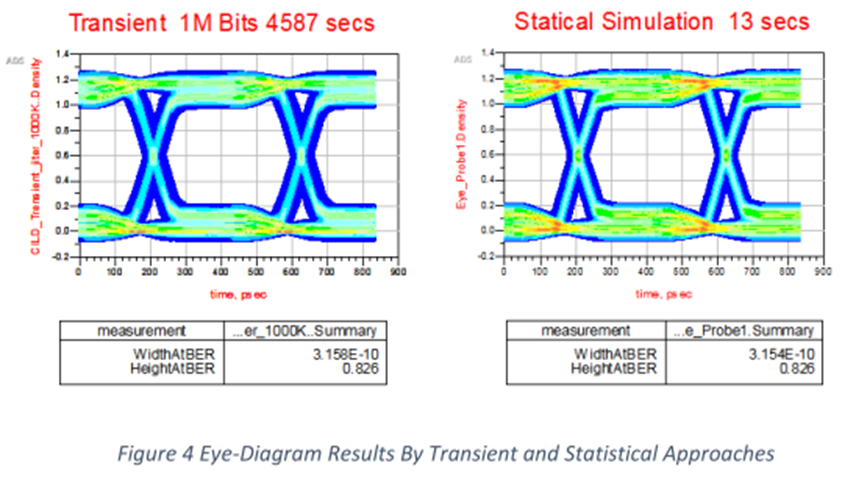

统计仿真方法是先基于IBIS模型表征信道、发射机和接收机的脉冲响应,再运用统计技术结合无限不重复比特模式的统计分布,直接获取超低误码率下的眼图概率分布,可快速测量误码率轮廓。

相比瞬态仿真的优势:以简1byte DDR4的前方真为例,统计仿真获取误码率仿真结果仅需13秒,而类似SPICE的瞬态仿真获取准确RJ,至少需仿真100万bit(误码率),耗时4587秒,统计仿真速度快350倍。

相比瞬态仿真的劣势:串扰相关噪声是线性时不变(LTI)的,统计仿真在脉冲响应表征中可处理;SSN噪声(Del

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

583

583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?