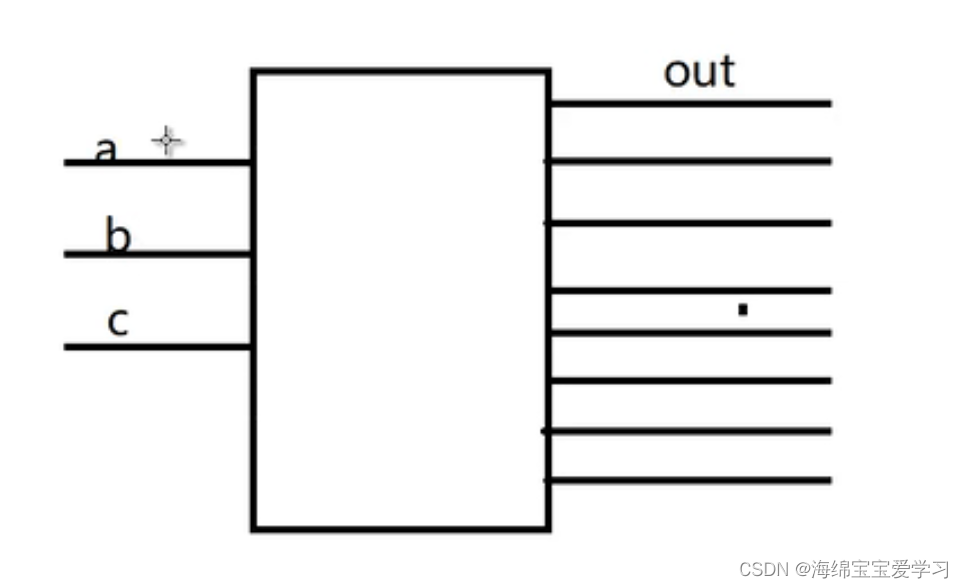

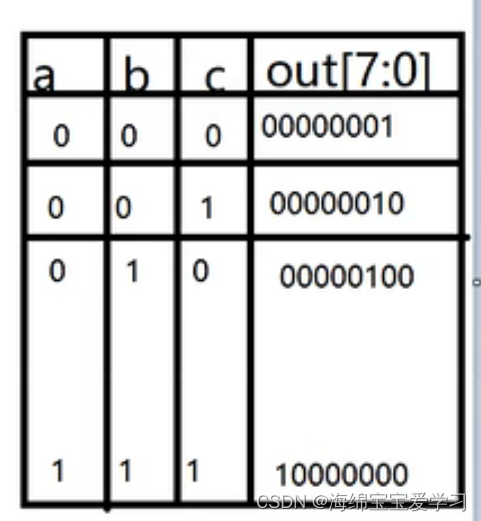

1. 3-8 译码器设计

将3位的输入信号输出8位的输出信号。

通过三个信号来控制8个信号的组合。

2. 创建vivado工程

2.1 设计定义

3个输入,8个输出

a 画框图

b Verilog

c IP

module decoder_3_8(

a,

b,

c,

out

);

input a;

input b;

input c;

output reg [7:0]out; // 表示多位宽的数据

// 以always 块描述的信号赋值,被赋值对象必须定义为reg类型

// wire [3:0]d;

// assign d = {a, 1'b0, b,c}

always@(*) // 第一种写法 *代表通配符, 描述一段逻辑块

case({a,b,c})

3'b000; out=8'b0000_0001;

3'b001; out=8'b0000_0010;

3'b010; out=8'b0000_0100;

3'b011; out=8'b0000_1000;

3'b100; out=8'b0001_0000;

3'b101; out=8'b0010_0000;

3'b110; out=8'b0100_0000;

3'b111; out=8'b1000_0000;

endcase

end

// b 二进制 d 十进制 h 十六进制

// always@(a,b,c) // 总是

// {a,b,c} 变成了一个三位的信号,这种操作叫做位拼接

endmodule

// test bench(tb 文件)

`timescale 1ns/1ns

// a b c为输入端口,设置激励为 reg类型

reg s_a;

reg s_b;

reg c;

wire [7:0]out; // 输出为线型

module decoder_3_8_tb:

decoder_3_8 decoder_3_8_(

.a(s_a), // 连线

.b(s_b),

.c(c),

.out(out)

);

initial begin

s_a=0;

s_b=0;

c=0;

#200;

s_a=0;

s_b=0;

c=1;

#200

...

$stop // 自己停

end

endmodule

2.2 扳级调试

配置管脚

下载程序

125

125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?