时钟管理单元介绍与应用

B的物理意义是 频率控制字,Fclk越大能够输出的频率Fout越大,将Fclk提高到125M,从硬件的角度,开发板上只有一个50Mhz的有源晶振。使用verilog的方法从50Mhz得到125Mhz的时钟信号是不可能的。逻辑实现不了,就提供专业电路。

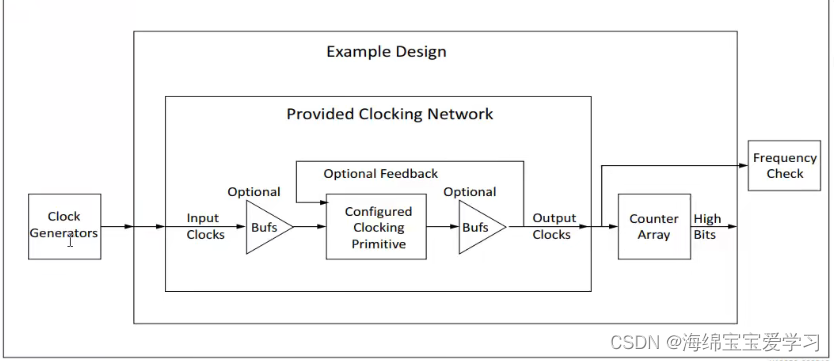

锁相环PLL来实现(时钟管理单元)

时钟管理器:

功能:通过GUI的界面形式,帮助用户来创建自己的时钟网络,能够基于一个输入时钟源(晶振),进行分频,倍频,得到其他频率、相位、占空比的时钟信号。这个时钟管理器根据用户的设置参数,去生成配置FPGA内部的时钟管理硬件资源。

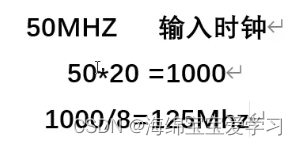

加入,时钟频率为50Mhz,要生成125Mhz。

50*5 = 250 / 2 = 125Mhz, 找最大公约数

先5倍频再2分频

MMCM 一般用在DDR3

PPL 时钟质量高

单就PPL的工作原理,会有一个反馈,通过不断调整内部的移动。

Lock信号 标志着时钟管理单元完成了对用户设置的需求的时钟信号的产生,此时的输出时钟信号就是满足要求且稳定的。

Locked 信号经常用作整个系统的复位信号。

分频因子和倍频因子。

1 选择时钟信号

2 选择输出 信号

3 复位,锁定信号

例化到工程文件中:

MMCM MMCM(

.clk_out1(CLK125M),

.resetn(Reset_n),

.locked(),

.clk_in1(clk_in1)

);

凡是用到clk替换成125Mhz

1223

1223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?