DDS信号发生器 通信系统里的调制解调

DDS 即数字合成器,是一种新型的频率合成技术,具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域

DDS的基本结构:

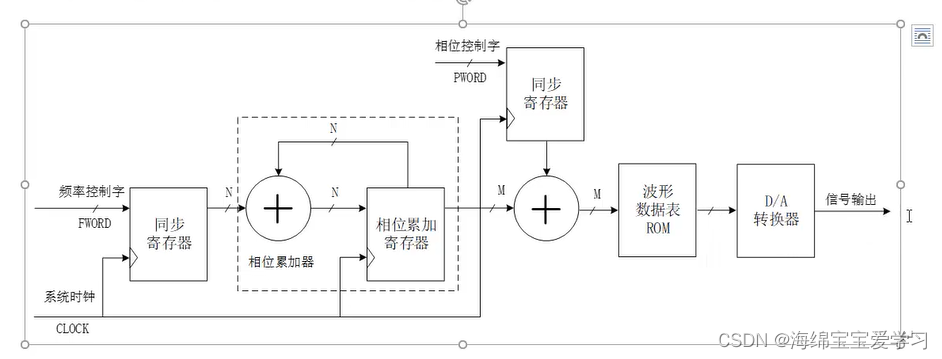

DDS主要由相位累加器、相位调制器、波形数据表以及D\A 转换器构成。

其中相位累加器由N位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

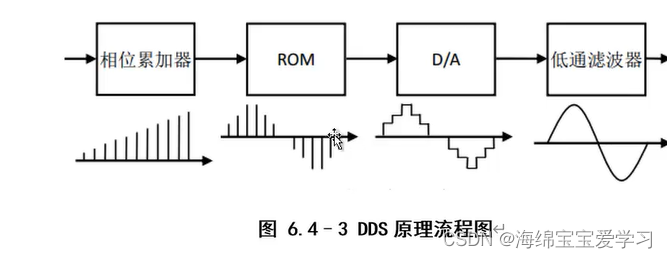

相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率,就是DDS输出的信号频率,下图所示,相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出数据到DA转换器,由DA转换器将数字信号转换成模拟信号输出。

DDS信号流程示意图 如下所示:

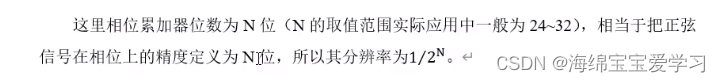

这里相位累加器位数是N位(N的取值范围实际应用中一般为 24-32),相当于把正弦信号在相位上的精度定义为N位,所以其分辨率为 1/2N次方。

因为理论中由以上三个参数就可以得到任意的fo输出频率。且可得出频率分辨率由时钟频率和累加器的位数决定的结论。当参考时钟频率越高,累加器位数就越高,输出频率分辨率就越高。

形象的解释:

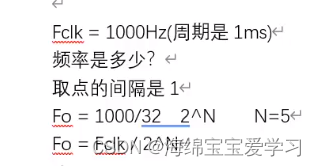

当FPGA控制DAC输出一个周期的正弦信号时,每1ms输出一个数值。如果每个点都输出,则总共输出这一个完整的周期信号需要输出32个点,因此输出一个完整的信号需要32ms,可知输出信号的频率为 1000/32 Hz

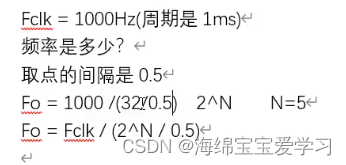

如果需要用这一组数据来输出一个 2*(1000/32)Hz的正弦信号,因为输出信号频率为 2*(1000/32)Hz,那么输出一个完整的周期的正弦波所需要的时间为32/2,即16ms。为了保证输出信号的周期为16ms,我们需要对我们的输出策略进行更改,上面输出周期为32ms的信号时,我们采用的时逐点输出的方式,以32个点来输出一个完整的正弦信号,而我们FPGA控制DAC输出信号的频率固定为1ms。因此我们要输出周期为16ms的信号,只能输出16个点来表示一个完整的周期,我们就选择每隔一个点输出一个数据的方式来输出即可。我们可以选择输出(1,3,5…) 这些点,我们还是能够组成一个完整的周期的正弦信号,而输出时间缩短为一半,即频率提高了一倍。最终结果如下图所示。

如果需要64ms来输出一个完整的周期?第一个和第二个时刻输出相同的第一个数据,依此类推~

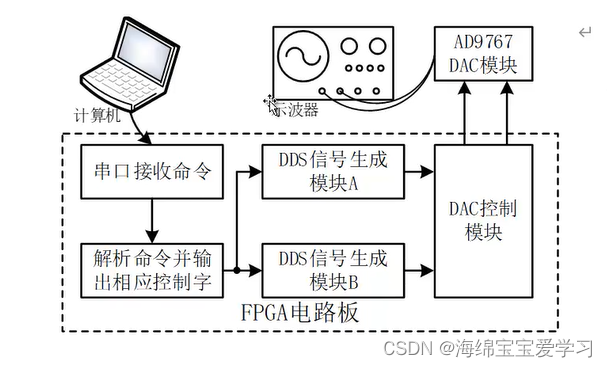

DDS基本原理与FPGA实现

32ms:

16ms:

64ms:

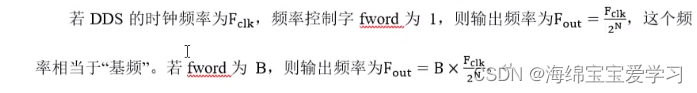

Fo的变化取决于取点间隔的变化,我们就把取点间隔 称为 频率控制字 Fword B

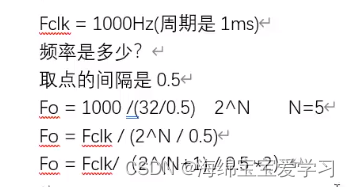

然后想FPGA可以表示0.5这个值吗?是很麻烦的,如果我还想用这个公式,保证值不变。

这样相当于N+1,现在这个N就是相位累加器的个数。N越大,相位控制值控制的范围就更广。假设N=32,还是要求每毫秒输出一个数字。

B = 2的27次方,一个完整的周期,被分成了2的32次方个点,输出32个点,每1ms输出一个点,得到一个完整周期的波形。2的32次方 / 32 这就是每次的步进 = 2的27次方。

如果是 32个点,那么N就是5。

7828

7828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?