文章目录

功能仿真

功能仿真的意思就与C++中利用数据结果调试代码类似,只用于解决在理论层次上对应输入的输出是否正确,是没有考虑门输入延迟的,所以结果就更加接近理论值标准,具体操作如下:

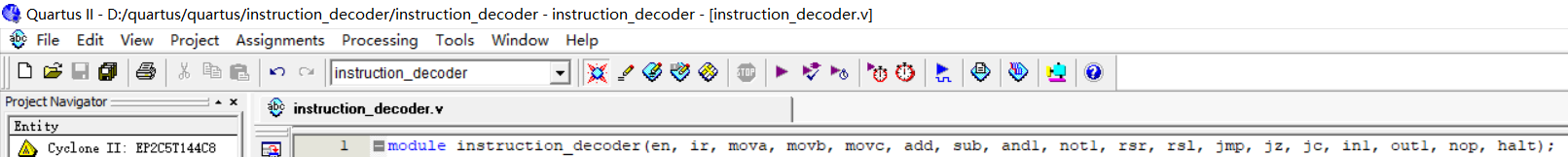

1.首先我们要先建立一个Verilog HDL 或者 VHDL文件,并且编译成功

注意此时的模块名字应与顶层相同。

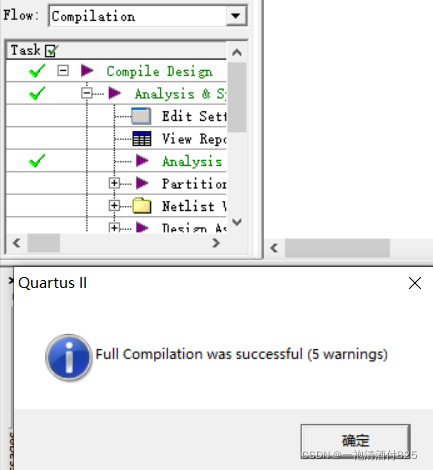

编译成功:

狗都不管warnings

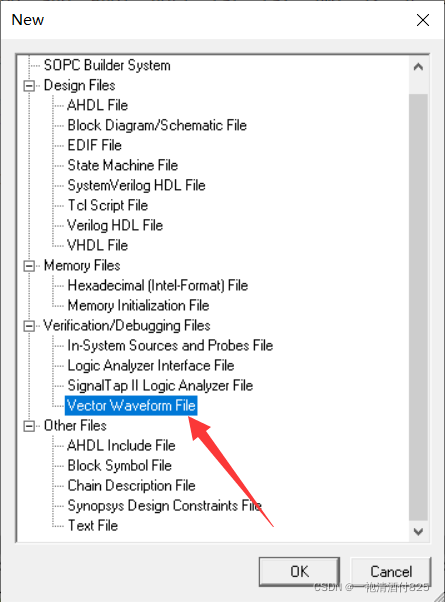

2.为了功能仿真我们应该建立一个vwf文件

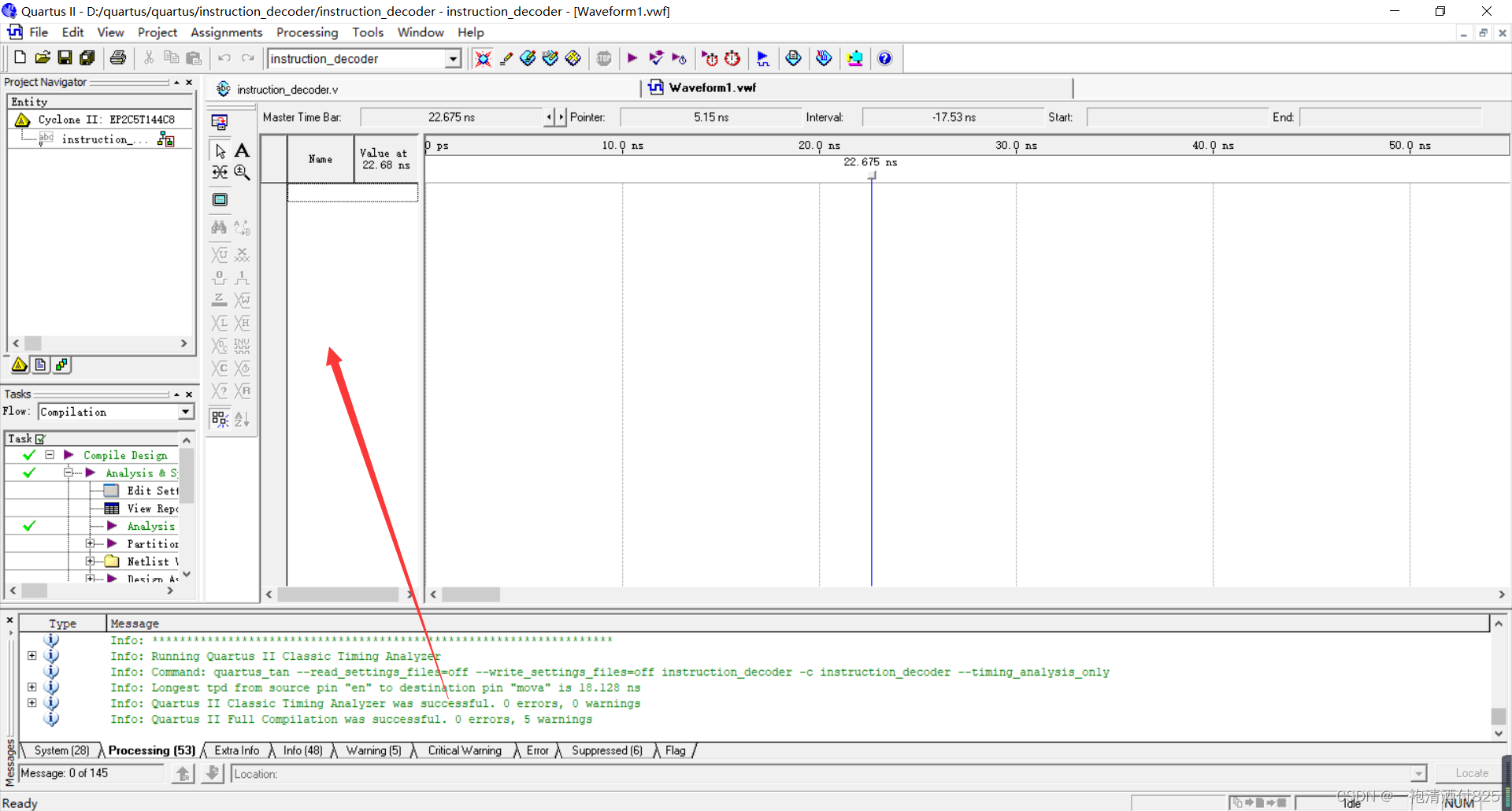

3.对vwf文件的操作

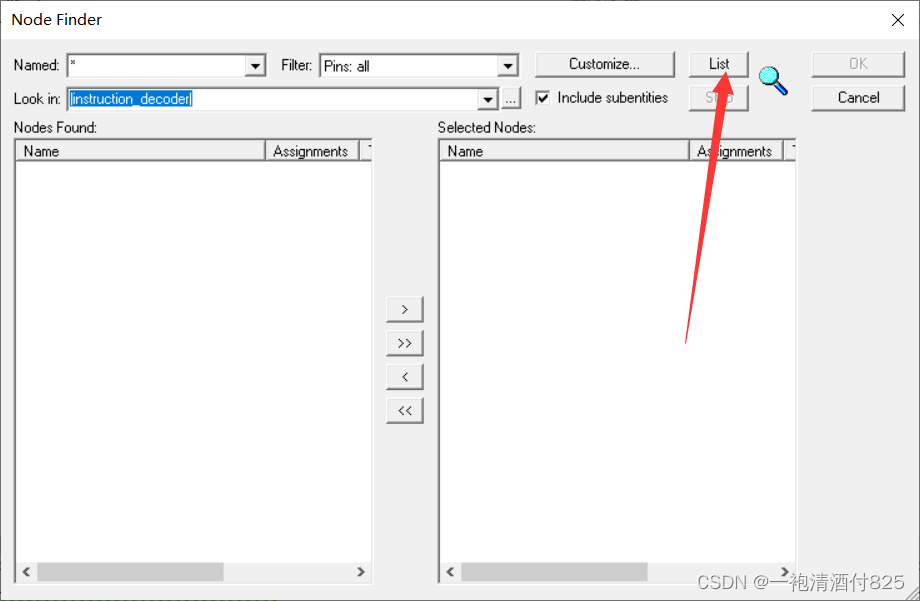

首先在下图所标示的地方右击。然后Insert->Insert Node or Bus->Node Finder.

然后就会出现下图,点击List,再点击那个右移符号">>",就ok了。

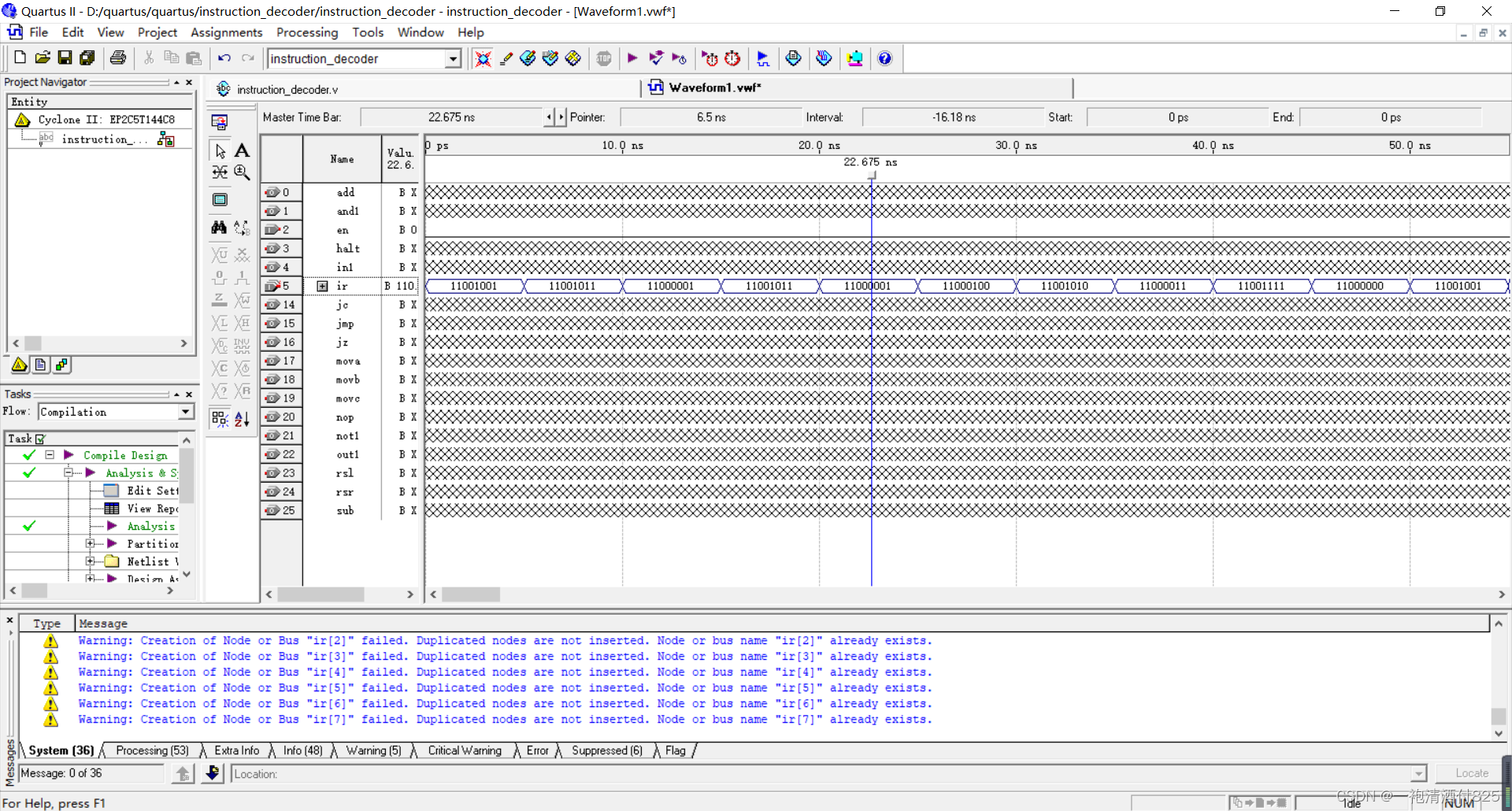

然后便有了下图,我们可以选择信号进行“调试”,比如这里我想看看模型及MOV指令是否写的正确,那么我就需要把输入ir的高四位定义为1100,然后就可以了。

4.功能仿真

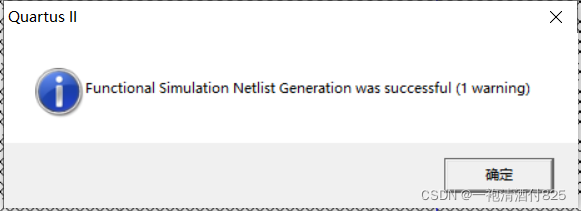

注意!!! 默认的是时序仿真!!! 所以在功能仿真前要先生成功能仿真网表!!!

首先要Processing->Generate Functional Simulation Netlist。

看到这个图之后才能进行后面的操作!!

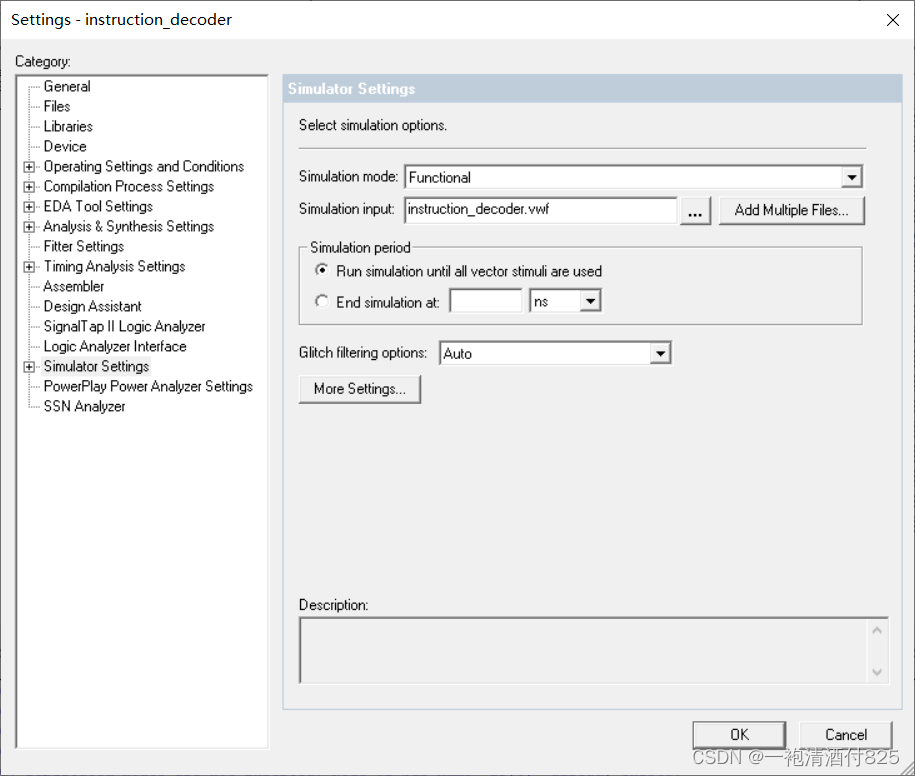

然后就是选择功能仿真了,Assignments->Setting->Stimulator Settings,然后把mode类型改为Functional再Add自己对应的vwf文件即可。

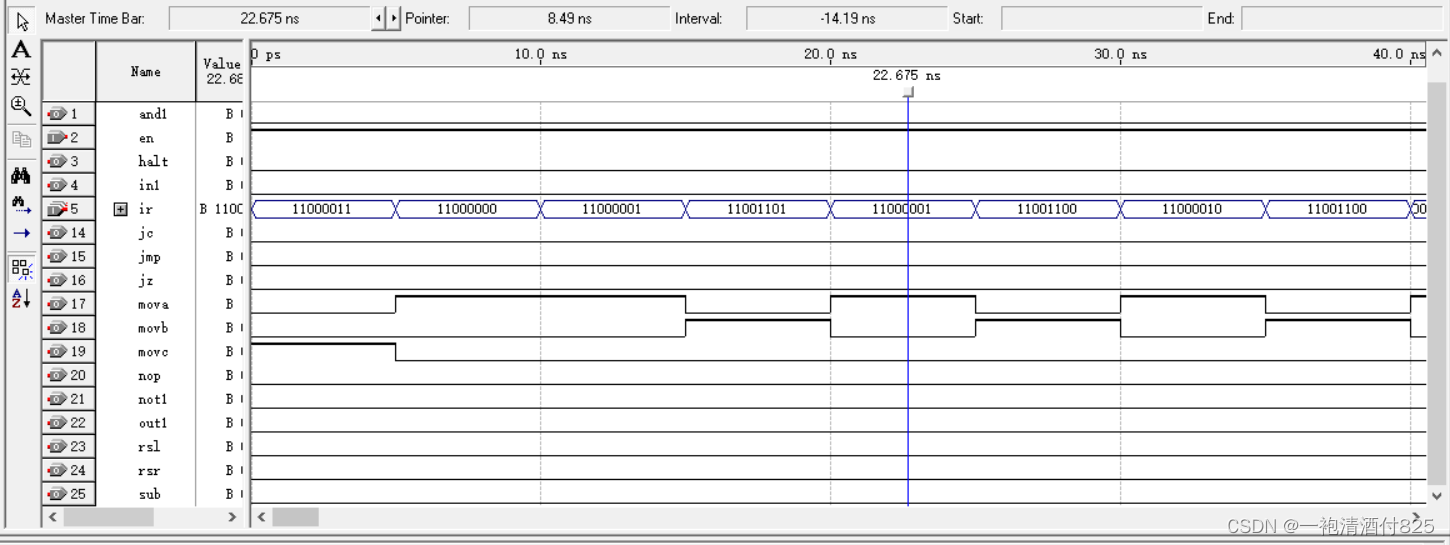

波形如下:

可以发现我的MOV指令是正确的。

本文详细介绍了如何使用Verilog HDL进行功能仿真,包括建立模块、创建vwf文件、设置仿真参数和检查MOV指令效果。重点在于通过实际操作演示如何在不考虑门延迟的情况下验证理论输出,适合初学者和调试工程师参考。

本文详细介绍了如何使用Verilog HDL进行功能仿真,包括建立模块、创建vwf文件、设置仿真参数和检查MOV指令效果。重点在于通过实际操作演示如何在不考虑门延迟的情况下验证理论输出,适合初学者和调试工程师参考。

3187

3187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?