一、前言

本人没什么FPGA的开发经验,然而一上来就要搞zynq和PCIE通信,上手真的太难了。查阅了各种网上资料,经历了一个多月各种测试终于成功调通了。因为网上关于pcie的资料太少,翻来翻去就是那么些内容,因此想要详细总结一下这方面的要点,帮助小伙伴少走弯路。我使用的平台是VIVADO 2017.4,芯片型号XC7Z015-2CLG485I,开发板是ALINX的AC7015。好了,废话不多说,进入正题。

二、建立工程

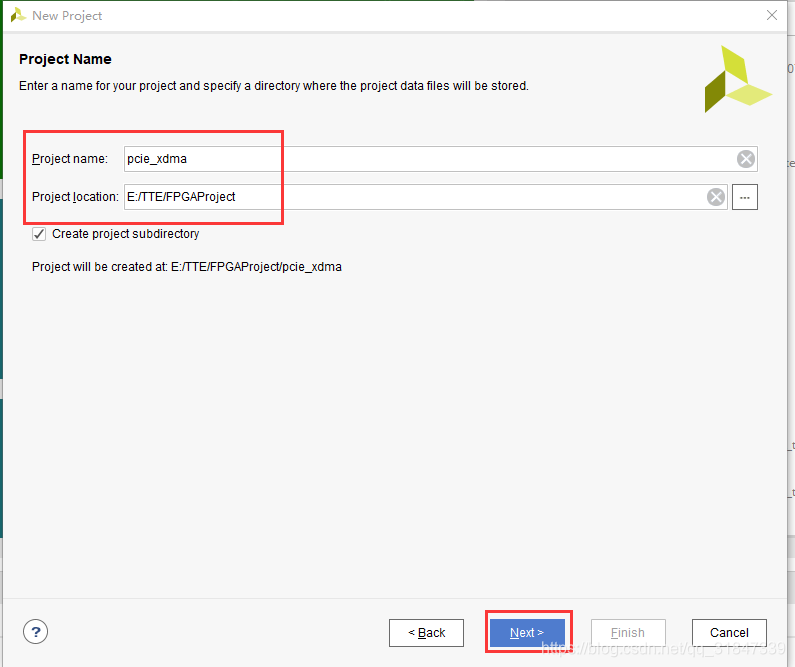

取好工程名字,选好路径(注意:工程名称和路径都不要有中文和空格),点击下一步

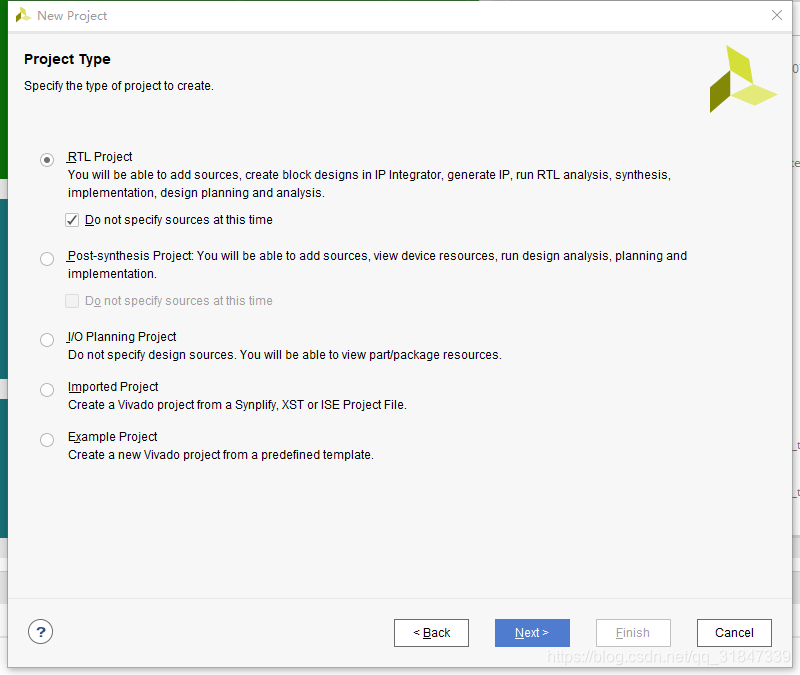

选择RTL工程

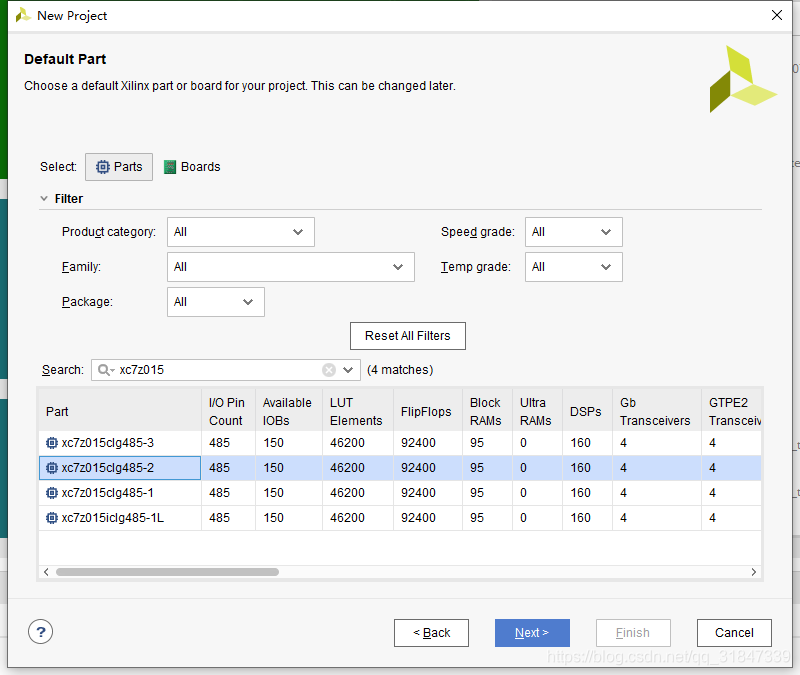

选好芯片型号,点击next后选择finish即完成工程创建

三、Block Design添加IP核

接下来在PL端搭建最基础的PCIE结构

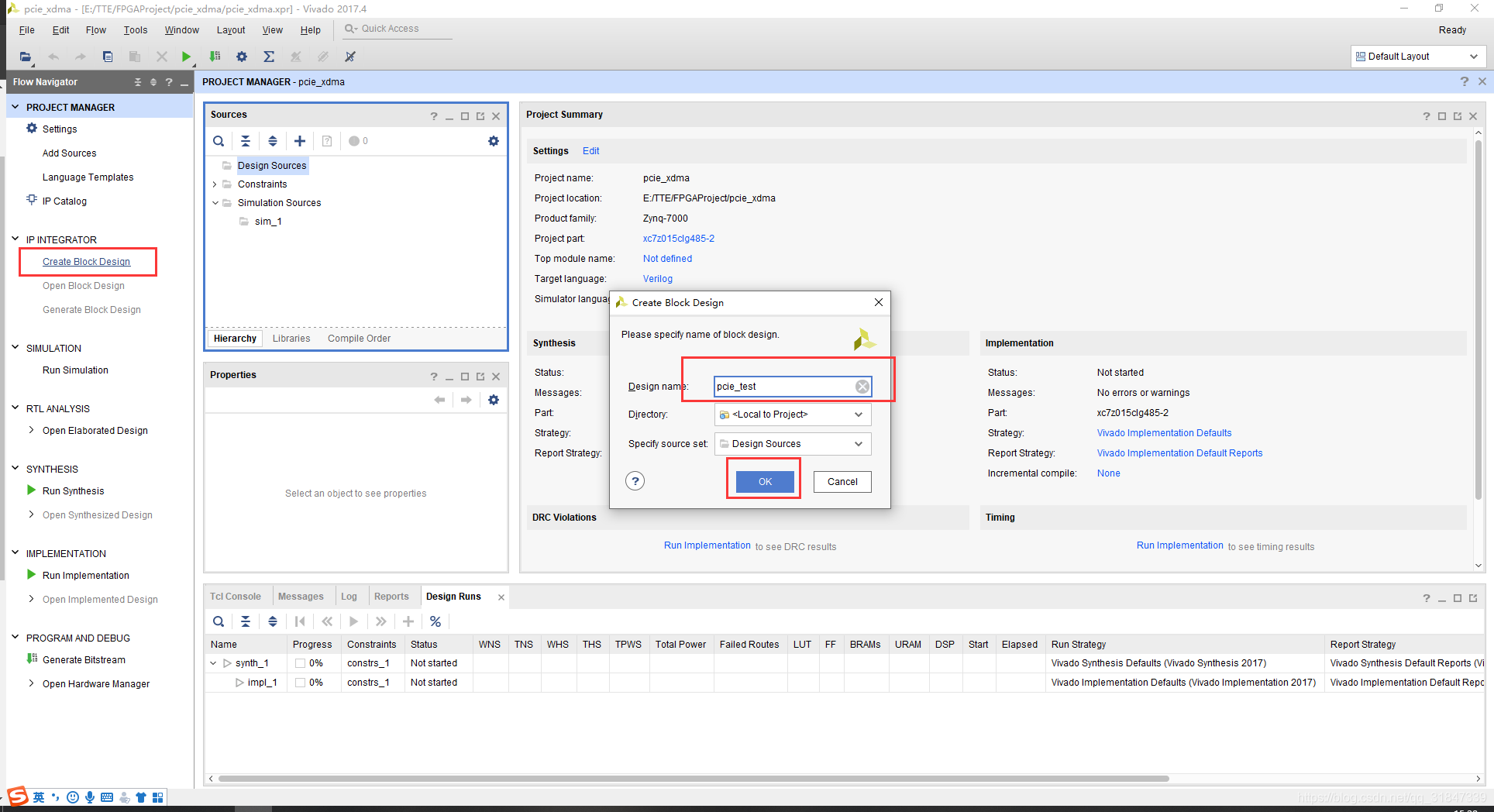

先生成空白的Block Design

2.1 xdma IP核

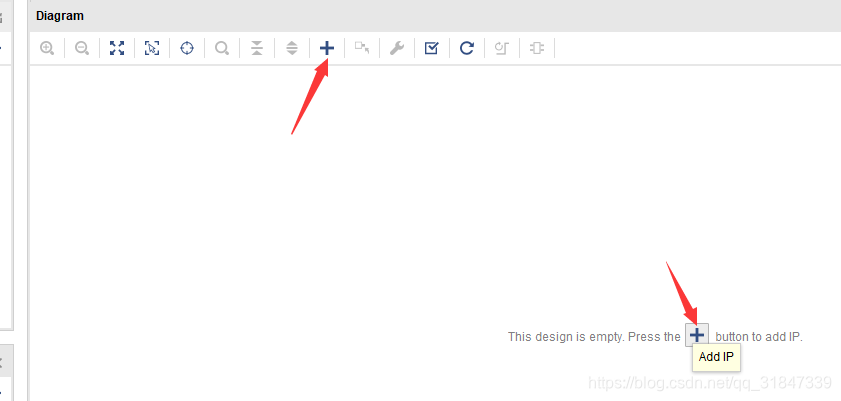

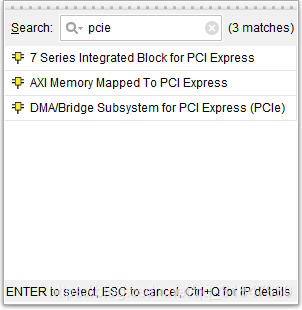

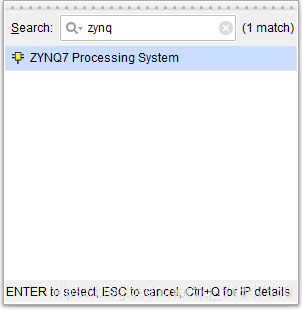

添加ip核(点击+号添加)

输入PCIE会发现有三个IP核,查了很多资料,其中XDMA(最后一个)是最简单的一个pcie IP核,不需要太多PCIE协议知识,作为小白当然选这个IP核。

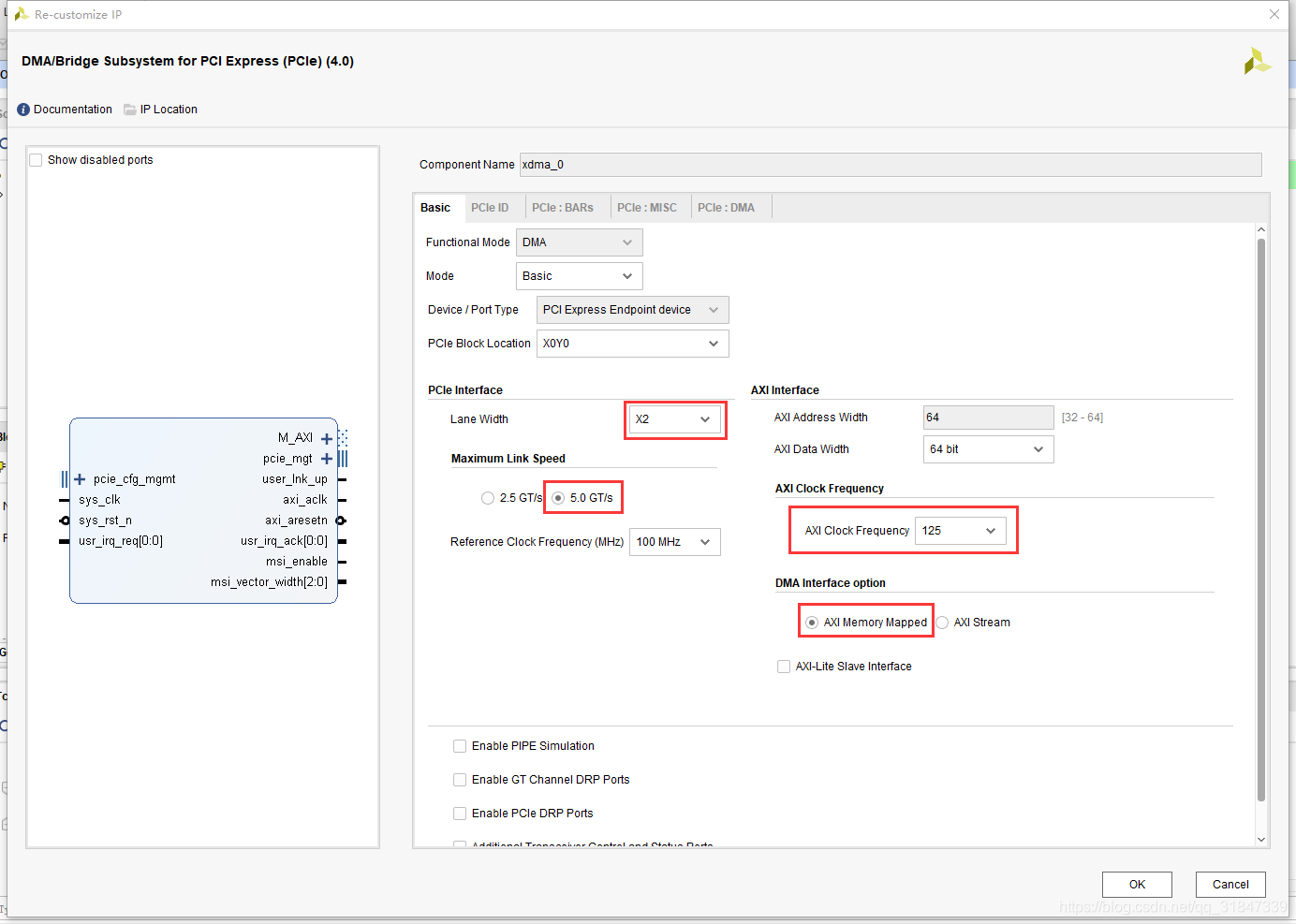

双击生成的XDMA IP核进行配置

lane width表示pcie通信并行数据宽度,我是用的这块ZYNQ FPGA最高只支持X2的;

link speed选择最大的,顺便说一句,这里的ip核都是pcie 2.0协议的;

AXI clock是AXI总线时钟频率,选125M

DMA interface是AXI Memory Mapped即地址映射,用于访问存储类的设备,另一个AXI Stream表示AXI数据流,没有地址,数据直接流入或流出,就像水管一样(可能说的不对,请大佬指出)

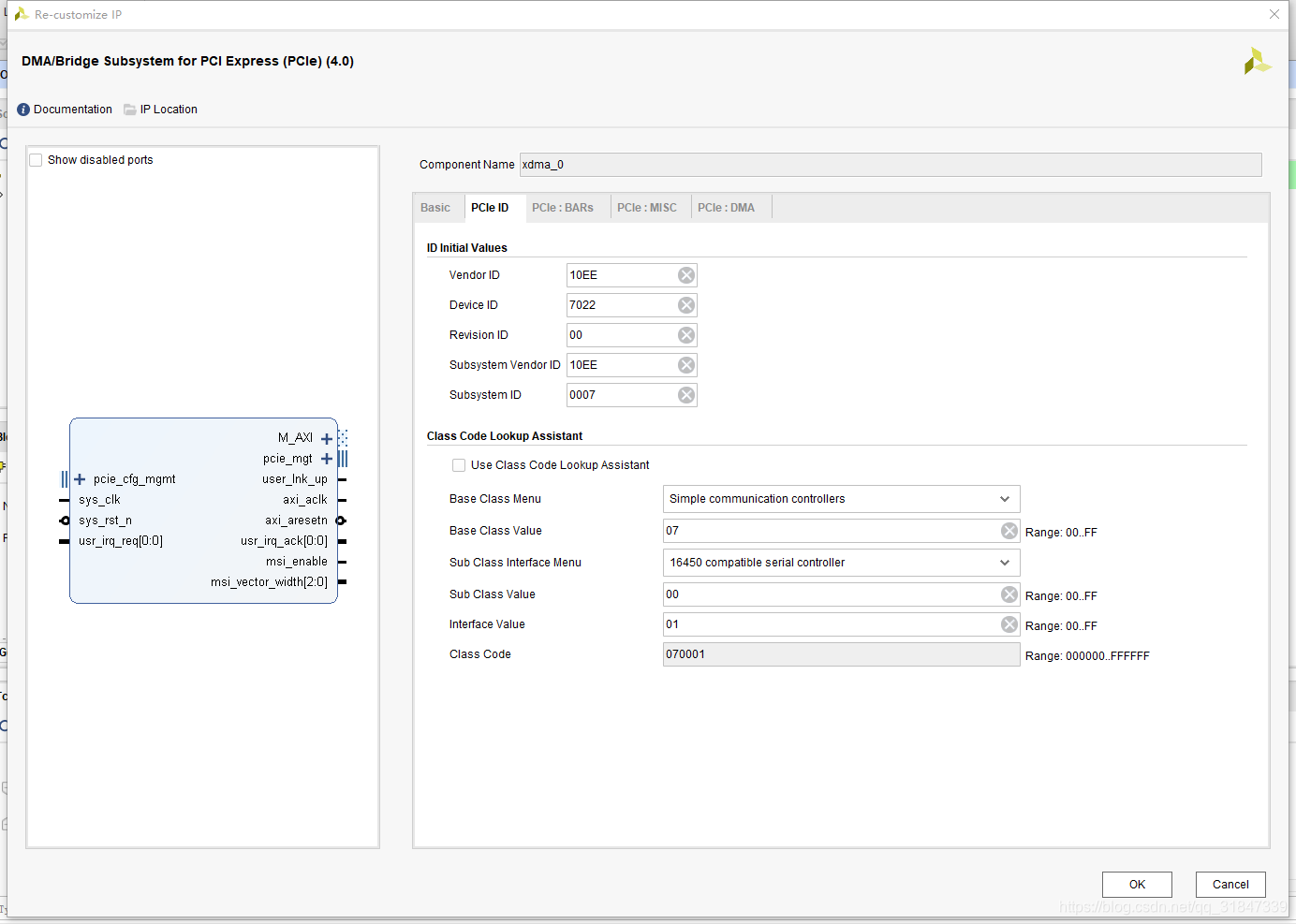

第二个标签页保持默认即可

这里是一些厂商ID、设备ID等配置

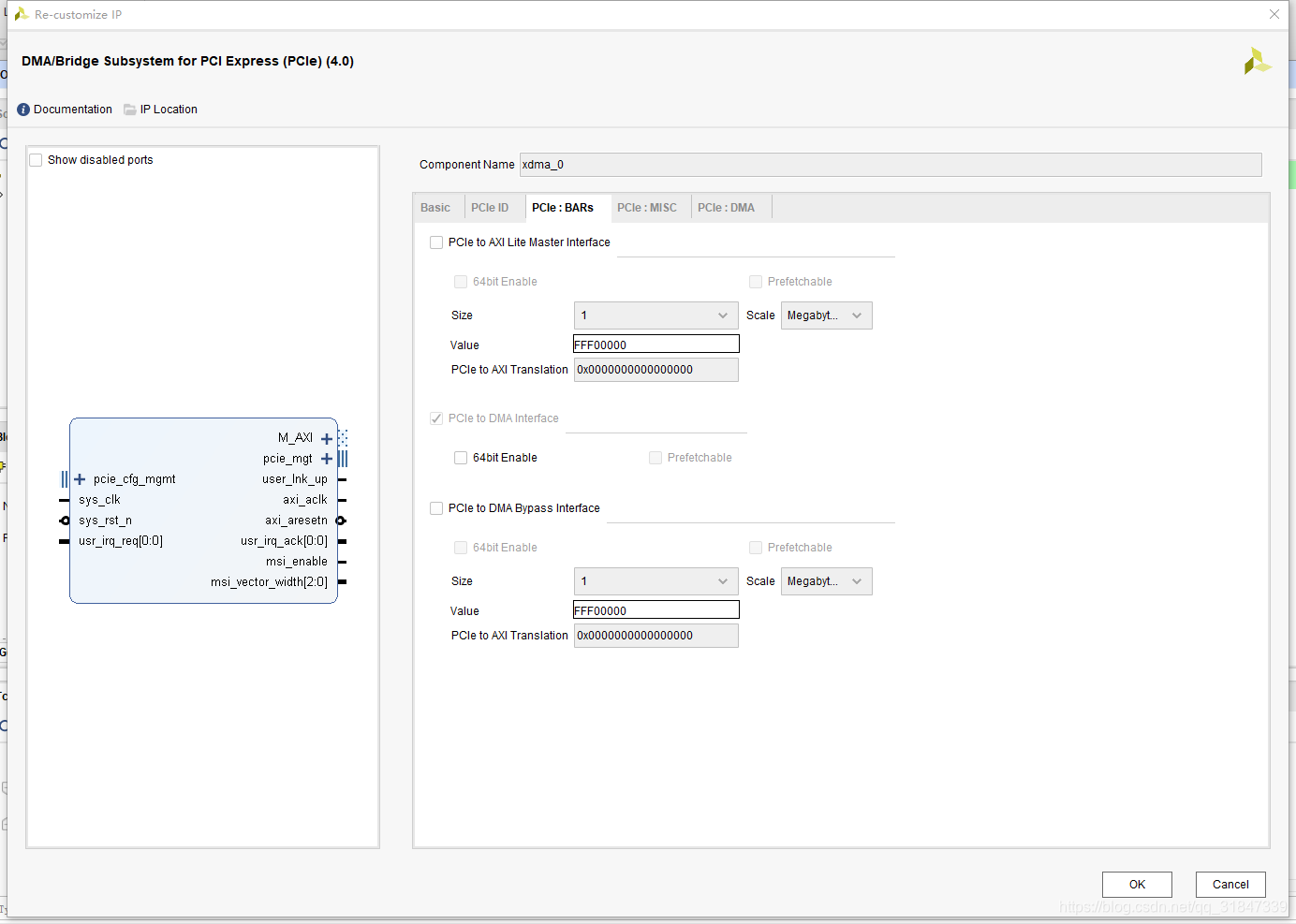

第三个标签页配置BARs(Base Address Register)

BARs往往是用来存放一些配置信息的,在主机端和板卡端都有各自相对应的BAR空间,这两个BAR空间相互关联,即一方对自己的BAR空间写入数据时,另一方也会在自己的BAR空间中收到该数据,因此也要注意避免同时读写的问题,value表示pcie端地址,pcie to axi translation就是一个从pcie地址映射到axi地址的一个偏移值,简单来说就是value+translation=axi地址,我这边概念也比较模糊,因为我没有用到BAR。

标签4和标签5不展开说了,保持默认就行

点击finish就完成配置了。

2.2 zynq IP核

添加zynq IP核

双击打开配置

我们可以看到zynq具有两个ARM Cortex-A9的处理器

再把目光聚焦

本文分享了作者在缺乏FPGA经验的情况下,如何利用Vivado2017.4和ALINX AC7015开发板,通过XDMA IP核实现Zynq与PCIE的通信过程。文章详细介绍了工程创建、IP核配置、引脚约束设定及编译流程,旨在帮助初学者快速上手。

本文分享了作者在缺乏FPGA经验的情况下,如何利用Vivado2017.4和ALINX AC7015开发板,通过XDMA IP核实现Zynq与PCIE的通信过程。文章详细介绍了工程创建、IP核配置、引脚约束设定及编译流程,旨在帮助初学者快速上手。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?