参考资料:

Zynq UltraScale+ MPSoC PS-PCIe End Point Driver - Xilinx Wiki - Confluence

PCIe Tips and Tricks - Xilinx Wiki - Confluence

1.枚举

如果硬件连接没有问题,在vivoda中配置好ping,在rc端使用lspci查找设备,就可以能看到ep节点了。

root@davinci-mini:~# lspci

80:08.0 PCI bridge: Huawei Technologies Co., Ltd. Device d103 (rev 45)

81:00.0 Memory controller: Xilinx Corporation Device a8082.ps端配置

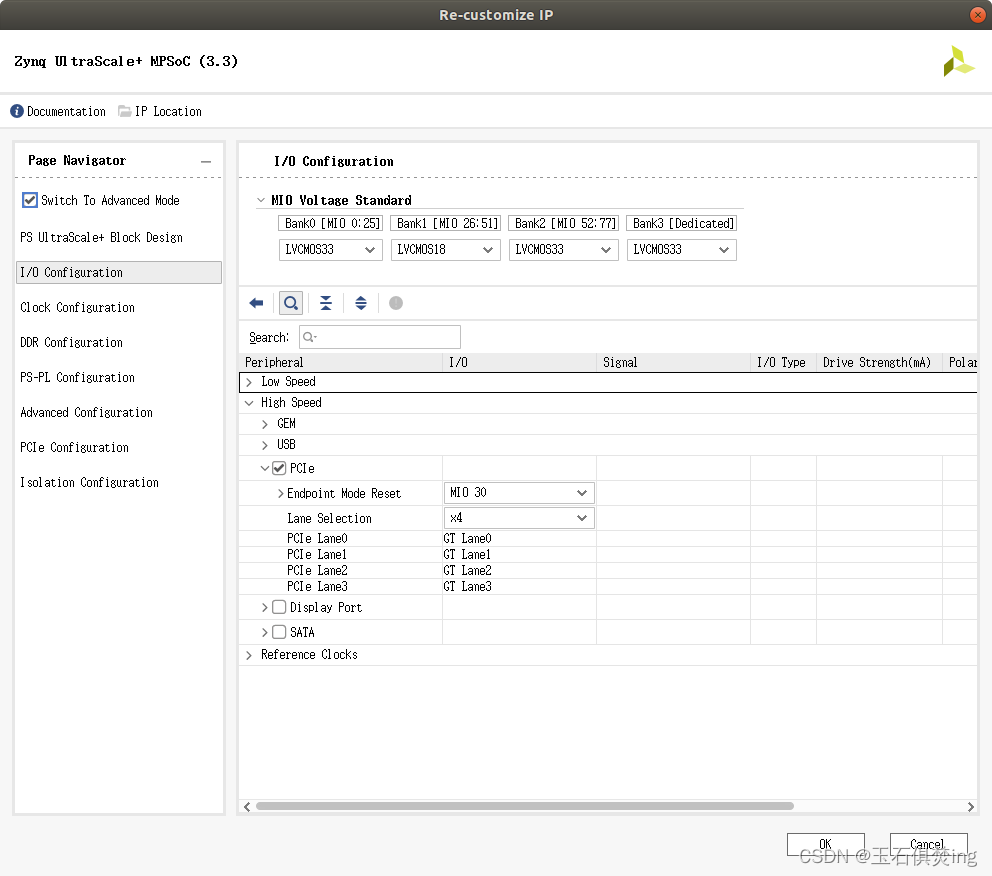

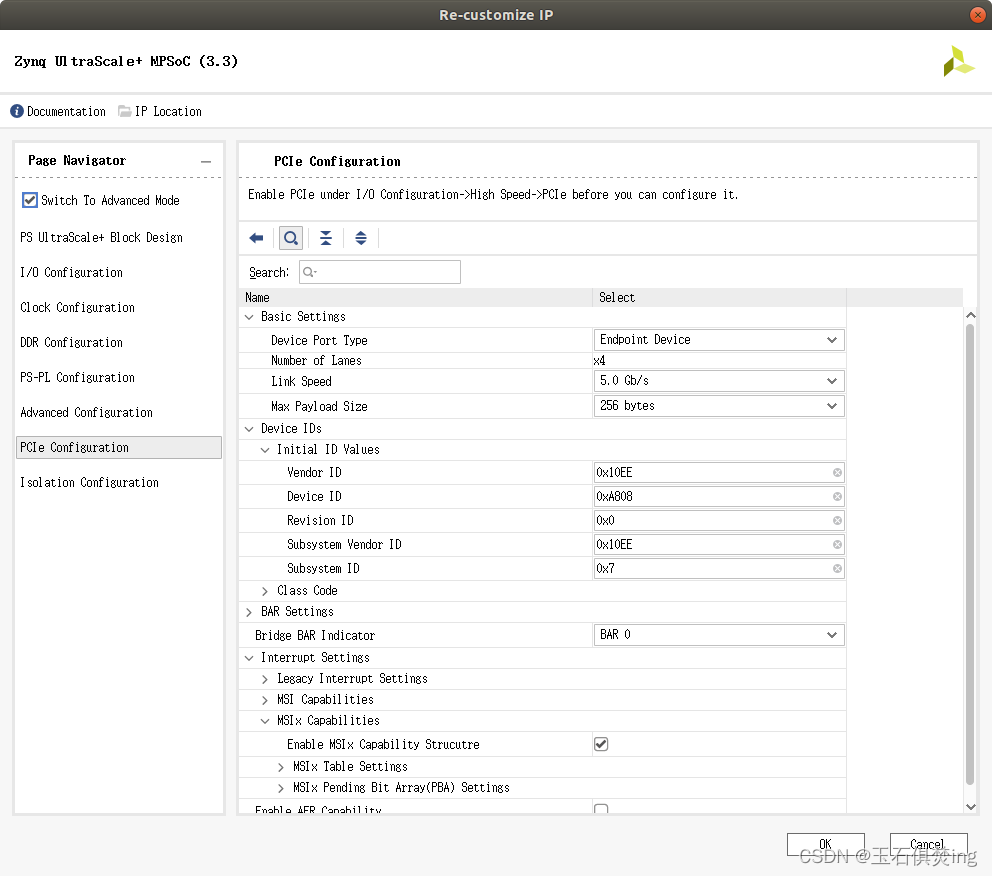

ps端配置注意device id,要和驱动中的ZYNQMP_DMA_DEVID1对应,interrupt settings中断的设置,有legacy,msi和msi-x三种,应该和rc端有关,如果加载驱动时出现错误,看错误信息排查问题。

3.编译rc端驱动

按上面的参考资料编译出ps_pcie_dma.ko并加载驱动,成功加载会出现下面5个设备文件,如果不成功查看log排查问题。

root@davinci-mini:~# ls /dev/ps_pcie_

ps_pcie_dmachan0_0 ps_pcie_dmachan2_0 ps_pcie_pio_0

ps_pcie_dmachan1_0 ps_pcie_dmachan3_0

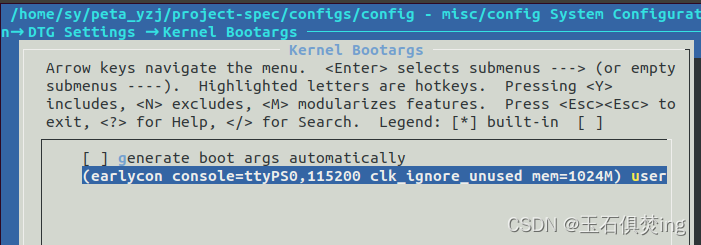

4.在kernel中预留ddr空间

因为我们要用dma方式传输数据,所以需要在ep端预留一部分内存供pcie读写使用。在petalinux-config中添加u-boot参数“mem=1024M”,表示kerenl只使用1G的内存。比如我板子上接的是2G的ddr,ddr地址空间是0~0x7fff ffff。那么这样设置后kernel只使用0~0x3fff ffff这部分的ddr。0x4000 0000~0x7fff ffff这部分的空间是空闲的。

5.测试发送数据

资料中有2个例子,simple_test和pci_pio_test,对应pcie2种传输方式。

1.DMA(Direct Memory Access)模式:直接内存访问,该模式下数据传送不是由CPU负责处理,而是由一个DMA控制器来完成,占用较少的CPU资源。

2.PIO(Programmed Input-Output)模式:可编程IO,该模式下数据传送由CPU执行I/O端口指令来处理,占用大量的CPU资源,数据传输速度也大大低于DMA模式。

dma方式rc直接将数据写入ep的ddr中,ep端口不需要运行程序配置,pio方式需要在ep端开启BAR,然后将BAR中的数据再写到ddr中。

// 运行例子

./simple_test -c 0 -a 0x40000000 -l 4194304 -d s2c

write return value is 4194304

Total time taken for transferring 4194304 bytes of data is 3300 micro seconds

可以看到rc写4MByte数据到ep,耗时3300us,所以速度达到了1212MByte每秒。

pio传输的方式还没搞明白,如果有懂的欢迎指教。

1578

1578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?