virtuoso版图问题汇总

- 简述

- 环境

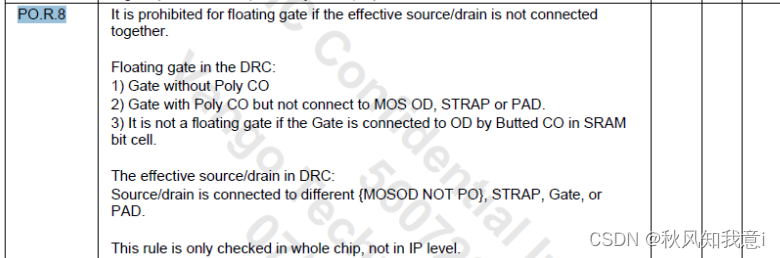

- 问题1:【PO.R.8】it is prohibited for floating gate if the effective source/drain is not connected together

- 问题2:LVS时,显示自己画的衬底没有连接

- 问题3:LVS的时候,Source netlist references but does not define 1 subckt:......

- 问题4:Calibre LVS如何区分full chip和子电路

- 问题5:pcellEvalFailed

简述

在使用TSMC65nm绘制振荡器版图时遇到问题汇总,解决问题时参考的链接也放出来了

环境

IC618

TSMC65nm

问题1:【PO.R.8】it is prohibited for floating gate if the effective source/drain is not connected together

未解决

参考

提示

我仿的IP,所以暂时忽略这个问题

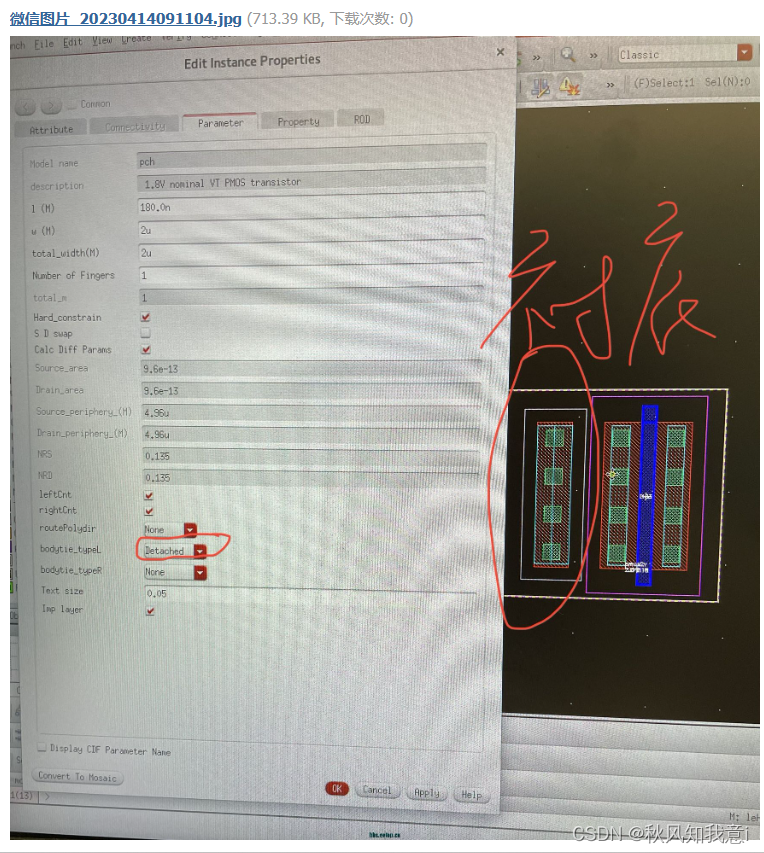

问题2:LVS时,显示自己画的衬底没有连接

Layout中衬底如何连接?

在器件里面设置,可自动生成衬底,左右两边都可以设置。

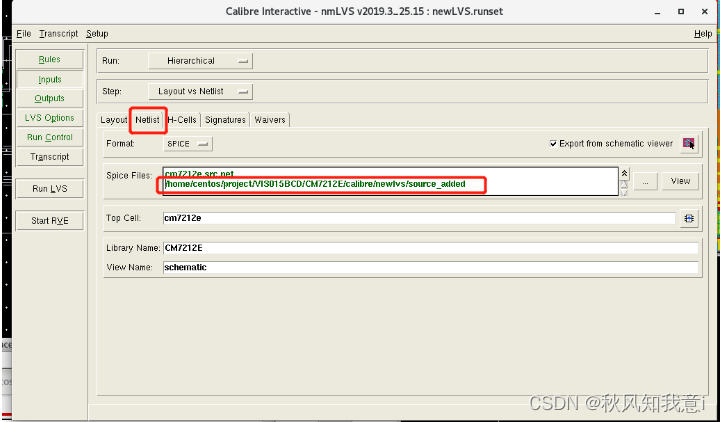

问题3:LVS的时候,Source netlist references but does not define 1 subckt:…

求助,LVS的时候Source netlist references but does not define 1 subckt:

一般在PDK里找到calibre文件里的LVS中的source.add文件在上图中添加。

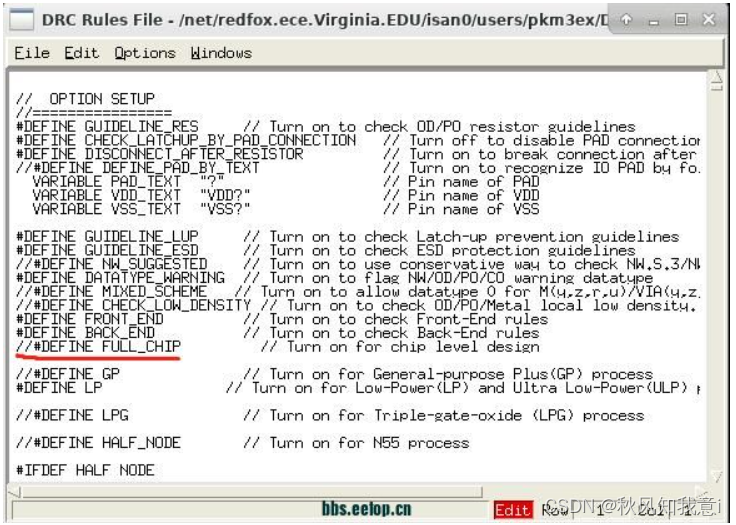

问题4:Calibre LVS如何区分full chip和子电路

问题5:pcellEvalFailed

原理图导入版图是出现pcellEvalFailed,这是因为晶体管的宽度使用了变量,使用具体的数值就不会报错了。

5442

5442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?