lisence相关

license申请 http://www.pangomicro.com 相关人员。

license安装:

需要在环境变量里面添加PDS的license,也在软件里面也添加license:

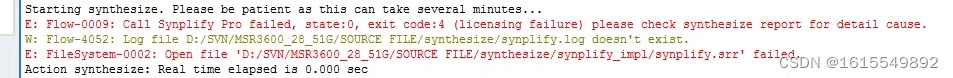

编译遇到如下报错:

Flow-0009: Call synplify pro failed,state:0,exit code 4 …

原因是编译器的bug,将synplify版本回退。

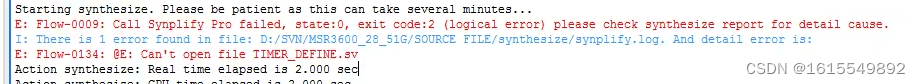

Flow-0009: Call synplify pro failed,state:0,exit code 2 …

添加include文件路径:但是软件会自动修改路径,离谱。原因是路径有两个下划线。软件不能识别

pango

源文件:

.v:编译前的文件

.vm:综合后的文件,是technology 网表

.sdc:时序约束文件

.pcf:物理约束文件

.fdc:FPGA Design 约束文件 synthesize时使用

.scf:synopsys约束文件 dev_map

.lcf:logic 约束文件 dev_map

.adf:synthsize、device map、place&route后的文件

.prr:place&route后的文件

.sbit:JTAG在线烧写文件断电消失

.sfc:对FLASH烧写文件。

.idf:IPcore文件

.fic:替换信号名称文件

example 里面的约束需要看是post(scf/lcf)还是pre(fdc),如果是(scf/lcf)可以直接使用.vm综合后的工程来移植,

不然可能会导致约束不上问题。

缩写

place&route : pnr

----------------------

synplify synthesize 产生下面文件

snr.db

xx.snr

synplify.lcf

xx.vm----给 dev_map

----------------------

device_map 产生下面文件

dmr.db

*.dmr

*_map.adf

----------------------

device_map 产生下面文件

prr.db

*.prr

*_plc.adf

*_pnr.adf

*_pnr.netlist

design editor (DE):查看芯片结构、查看布局布线结果、手动修改布局布线等。

必须的输入文件是:*_pnr.adf | _plc.adf

ip compiler :输出idf文件

physical constranint editor(PCE):对实例和IO进行布局约束、区域约束和IO设置。

必须输入输出 .pcf文件

route constranint editor (RCE):布线约束,与(DE)中手动布局布线功能类似,区别是RCE禁止布局。

必须输入*_plc.adf和.rcf,

user constranint editor(UCE):对实例和IO进行时序约束和逻辑约束。

采用ADSsynthesize有两种选择: UCE读取和编辑是 (post 输出scf文件), (pre输出fdc)

采用synplify UCE读取和编辑是 (只有pre 也是fdc,不是sdc)

不使用任何综合工具时,UCE读取的是sdc文件

timing analyzer (TA):导入pnr DB\syn DB和sdc

在这里插入代码片

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?