目标

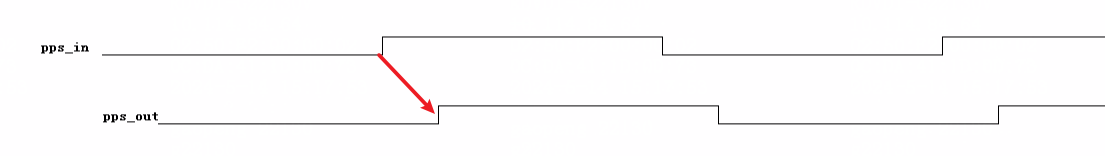

要求1:将输入的pps_in信号的上升沿延时输出,延时动态可配,延时调整范围10ms~1990ms,步进1ns。下降沿不管。

要求2:输入信号pps_in是低速周期信号,周期1s。

可见为了实现能细调到1ns,最少采用1GHz的采样频率。

恰好iserdes可以实现过采样。

实现思路

上述目标可以转化为:

何时输出下降沿?上升沿之后固定的时间后输出下降沿,下降沿不用严格跟踪。–可单独搞个计时。

何时输出上升沿?—计数到固定时间

采样乒乓计数器实现即可。

iserdes用高速时钟用500M双沿采样,可达到1GHz采样,最后出来的并行数据8bit是125M。

计数含本拍距离上升沿过了多少个UI,达到设定的个数,就输出高或者低。

3294

3294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?