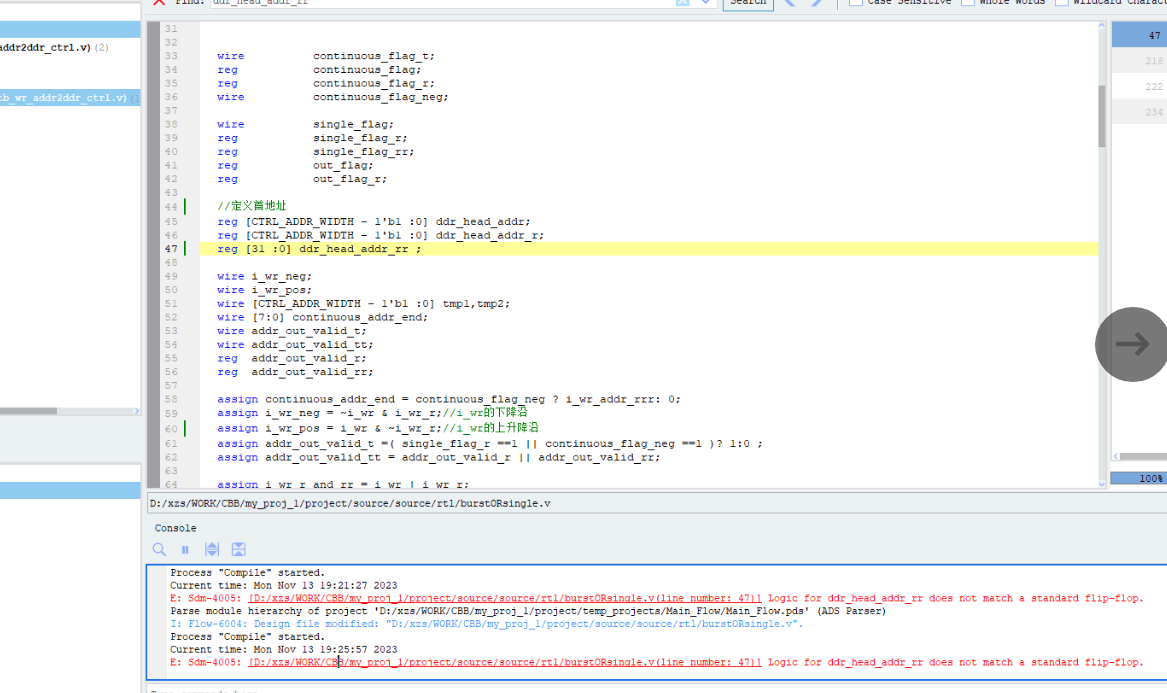

紫光pango design suite报错:

一、4005: [D:/**/rtl/burstORsingle.v(line number: 47)] Logic for ddr_head_addr_rr does not match a standard flip-flop.

看来看去都没有发现这个定义没有问题呀,检查发现:

原来代码:

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

begin

ddr_head_addr_r <= 'd0;

ddr_head_addr_rr <= 'd0;

end

else

ddr_head_addr_r <= ddr_head_addr;

ddr_head_addr_rr <= ddr_head_addr_r;

end

注意看第8和第9行,少了一个begin end的,修改后的代码

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

begin

ddr_head_addr_r <= 'd0;

ddr_head_addr_rr <= 'd0;

end

else

begin

ddr_head_addr_r <= ddr_head_addr;

ddr_head_addr_rr <= ddr_head_addr_r;

end

end

修改之后完美解决。

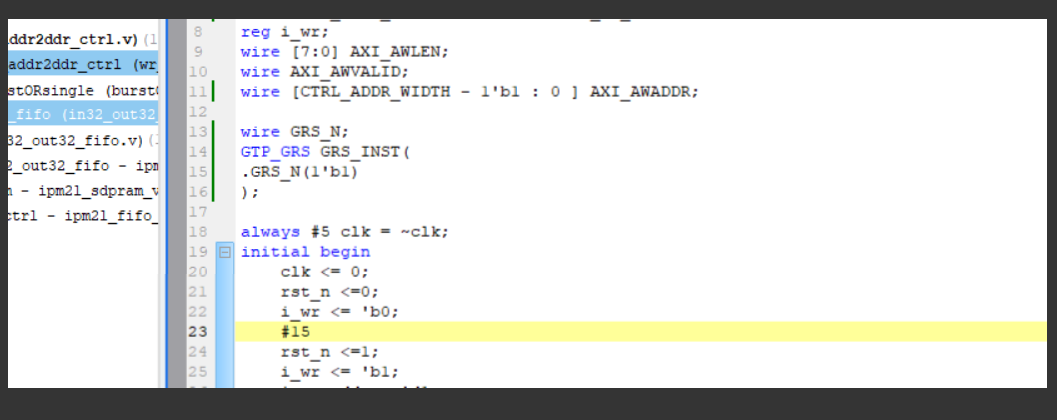

二、利用紫光PDS和Modelsim联合仿真时,出现这样的错误:

Error: (vsim-3043) D:/pango/PDS_2022.2-SP4/arch/vendor/pango/verilog/simulation/GTP_DRM36K_E1.v(1426): Unresolved reference to 'GRS_INST'.

解决方法:test_bench中添加语句

wire GRS_N;

GTP_GRS GRS_INST (

.GRS_N(1'b1)

);

原因:紫光自带的系统复位模块

参考:

https://blog.csdn.net/weixin_44282512/article/details/125028659

---晓凡 2023年12月18日于武汉书

3083

3083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?