GPIO(General Purpose I/O)

参考文档 ug1085

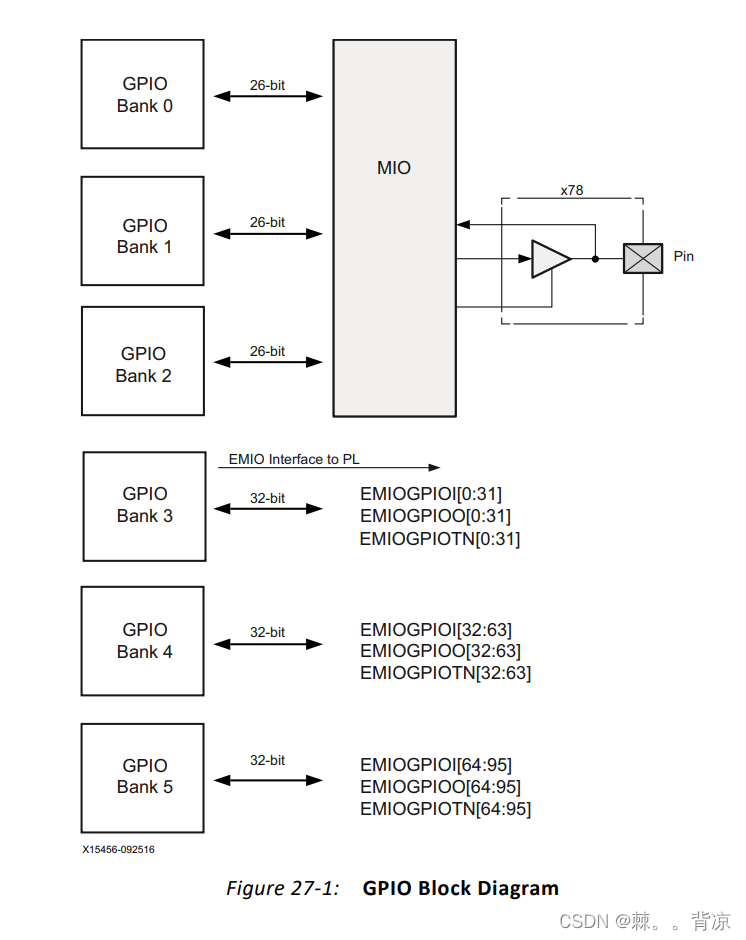

GPIO即通用I/O,使用过树莓派和单片机的同学们肯定非常熟悉。是ARM芯片用于连接外设的I/O口。在SOC Ultrascale+ 里的ARM芯片的GPIO连接到MIO(复用IO,与GPIO不是一一对应的);当MIO不够用时,可以使用EMIO来扩展,从而使用FPGA上的引脚,EMIO是PS和PL的连接的接口。

所有的GPIO都可以配置为输入,输出和中断模式。

zynq Ultrascale+系列的FPGA的GPIO被分为6个bank,其中bank0,bank1,bank2连接到MIO;banl3,bank4,bank5连接到EMIO。

MIO

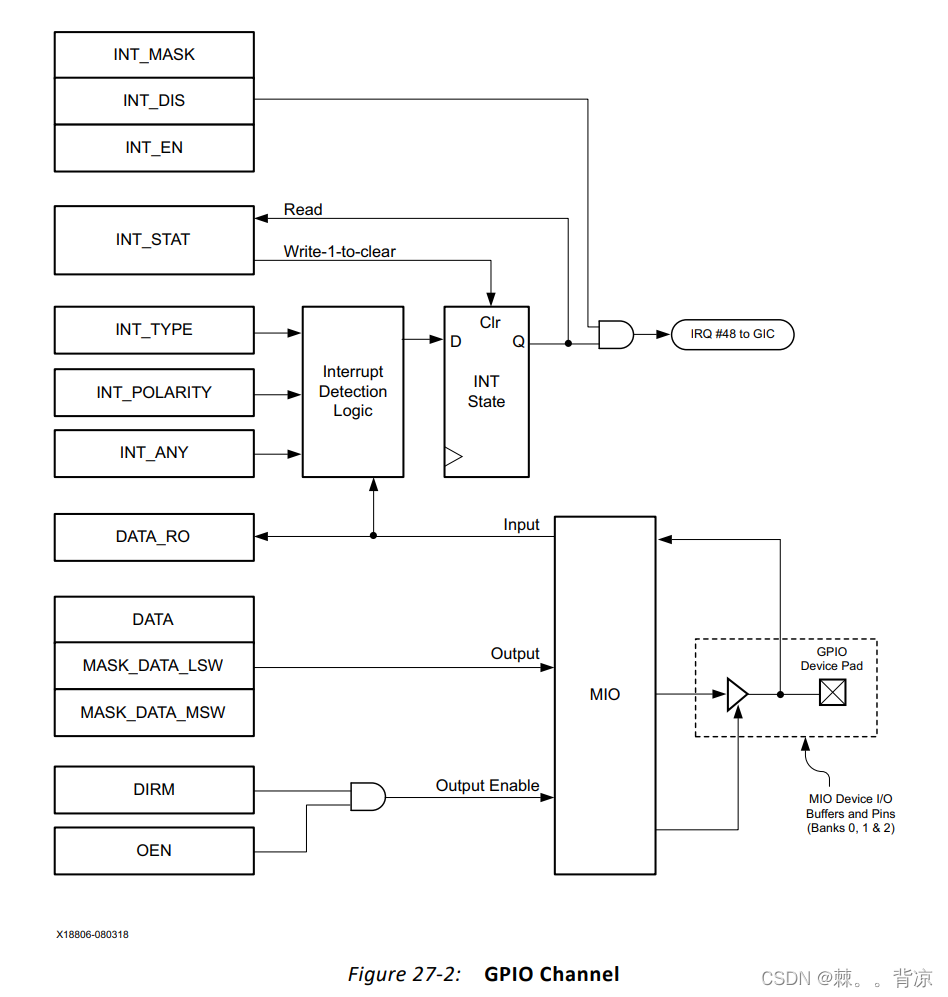

软件通过一系列的寄存器来控制GPIO,对于MIO,其寄存器配置如下

| 寄存器 | 功能 |

|---|---|

| DATA_RO | 读出器件引脚状态 |

| DATA | 32bit寄存器,在GPIO被配置成输出时,该寄存器可以控制其初值 |

| MASK_DATA_LSW | 16bit寄存器,用于选择DATA寄存器的低16位,或者是屏蔽DATA低16位 |

| MASK_DATA_MSW | 16bit寄存器,用于选择DATA寄存器的高16位,或者是屏蔽DATA的高16位 |

| DIRM | 方向模式,用于控制I/O是输入或者输出;为0为使能输入,为1输出使能 |

| OEN | 输出使能,当I/O被配置成输出时,用于使能输出,0为关闭输出使能 |

EMIO

EMIO的GPIO为banl3,bank4,bank5,与MIO相似。EMIO和MIO有些不同

| 输入来自与PL,输入与输出值和OEN寄存器无关 |

|---|

| 输出没有三态,与OEN寄存器无关。EMIO中的OEN被接出,作为EMIOGPIOTN,在程序中,仍然可以通过OEN和输出信号来构成三态 |

| DIRM寄存器必须设置为1 |

中断

GPIO的输入信号能够被PS的中断探测逻辑给检测。中断的触发包括:上升沿触发,下降沿触发,下降沿和上升沿触发,低电平触发和高电平触发。这些触发模式使用寄存器来设置,见GPIO CHANNEL图

寄存器介绍

| 寄存器 | 功能 |

|---|---|

| INT_MASK | 只读,显示当前那个位被掩盖或者没有掩盖 |

| INT_EN | 写1使能或者解除屏蔽每个中断信号 |

| INT_DIS | 写1屏蔽掉中断信号 |

| INT_STAT | 该寄存器显示中断是否发生。写1清除INT State寄存器值。 |

| INT_TYPE | 中断类型,中断时边沿还是电平 |

| INT_POLARITY | 中断极性,中断时低电平触发还是高电平(为1),或中断是上升沿触发(为1)还是下降沿 |

| INT_ON_ANY | 如果中断时边沿触发,1为上升沿和下降沿触发 |

所有的GPIO中断都连接到中断控制器中(GIC),中断号为:IRQ ID#48。 使用INT_MASK和INT_STAT可以判断是那个GPIO产生的中断。即INT_STAT=1和INT_MASK=0,来判断中断产生的GPIO。

本文详细介绍了Zynq Ultrascale+系列FPGA的GPIO接口,包括MIO和EMIO的工作原理及寄存器配置。MIO通过一系列寄存器控制输入输出,而EMIO直接与PL相连,其特性略有不同。所有GPIO均可配置为输入、输出或中断模式。

本文详细介绍了Zynq Ultrascale+系列FPGA的GPIO接口,包括MIO和EMIO的工作原理及寄存器配置。MIO通过一系列寄存器控制输入输出,而EMIO直接与PL相连,其特性略有不同。所有GPIO均可配置为输入、输出或中断模式。

1760

1760

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?