1.今天做一个秒表实例,介绍用Vivado制作FPGA工程

2.使用两个按键key0(秒表驱动、暂停)、key1

下面演示Vivado操作过程

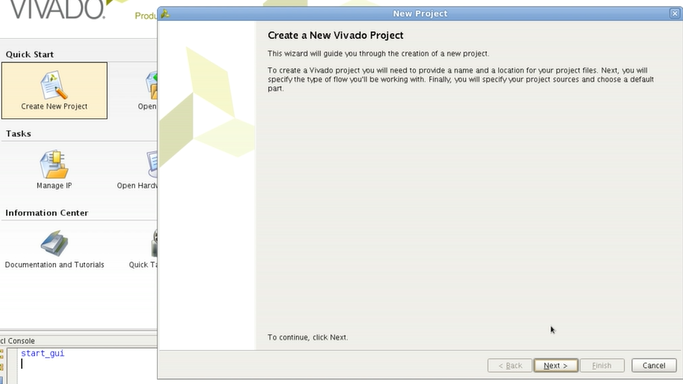

1.create project(图)

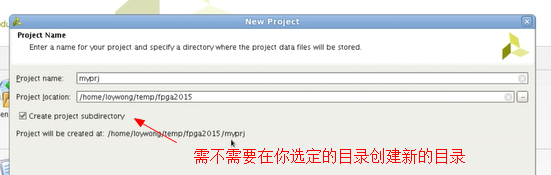

2. 一般来说都会选择它(图)

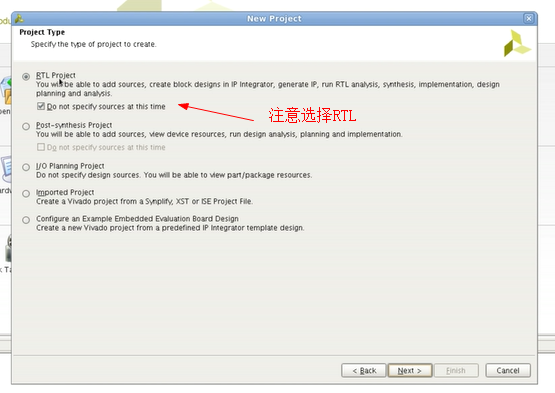

3.不选择源文件(图)

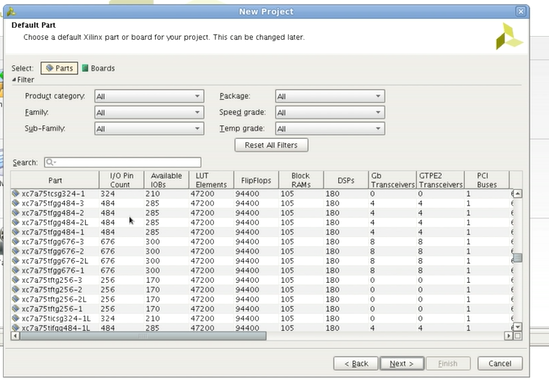

4.选择芯片(我们用的是xc7a35tftg256-1)也可以用过滤器选择芯片(图)

5.单击完成,我们的工程就创建完了,但是一片空白,我们最后要产生bit文件(图)

我们可以看到信息窗口,summary窗口etc.

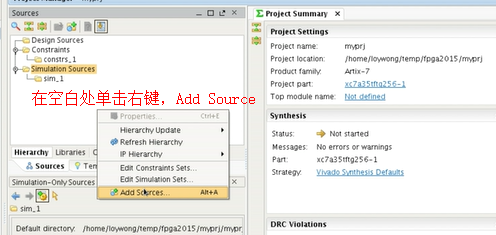

6.Add Source(图)

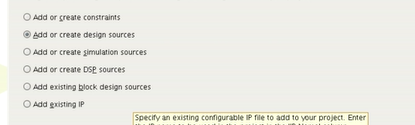

7.先添加设计源文件(图)

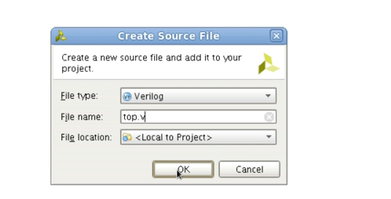

8.我们要的文件已经写好了,有top.v , keys.v , cnt.v

Cnt是一个计数器,keys是去抖(用定时采样实现)(图)

依次添加3个源文件,直接单击ok

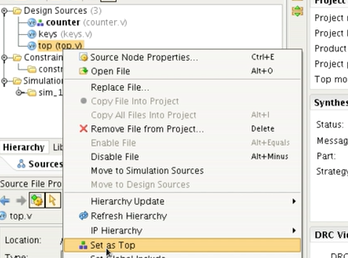

9.设置为顶层文件(图)

10.把已有的源代码copy进来

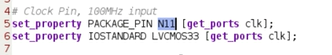

11.我们还需要约束文件,一方面要有时序约束,还要引脚分配Z

空白处Add Source->Add or creat constraints->name(master一般取这个名字)

以后大家一直用老师提供的.xdc文件就好了(下图为引脚分配 )

(图)

但是注意,ddr的引脚分配不在这个.xdc文件的

如何把注释掉的引脚释放呢?Ctrl+’?/’

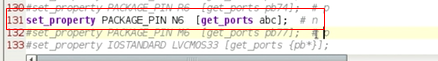

12.重要!!!假设有个output abc,你想把abc放在某个地方(扩展I/O口)

你可以把对饮注释拿出来,把这个get_port后面改成‘abc’

(图)

相当于你把abc放在那个I/O上了

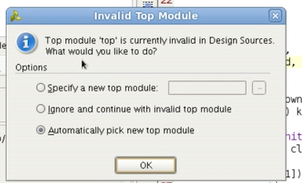

当我们想保存时,vivado检查到语法错误,ignore:

(图)

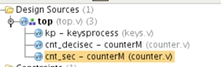

13.vivado简单分析了.v的结构

(图)

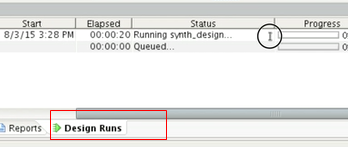

14.我们单击generate bitstream(图)

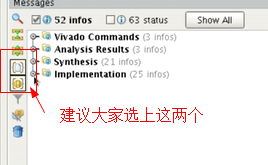

我们还可以关注message窗口(图)

编译完成,我们可以看Implementation里面各种报告

下载到板子,我们应该直接打开Hardware Manager,把开发板上电

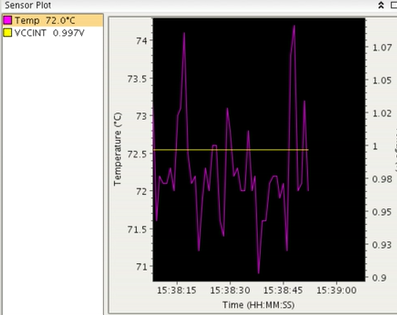

Open New target->next->可以看里面的监视(图)

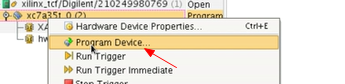

1.下载bit文件(图)

(图)

一定注意是.runs/impl_1/top.v

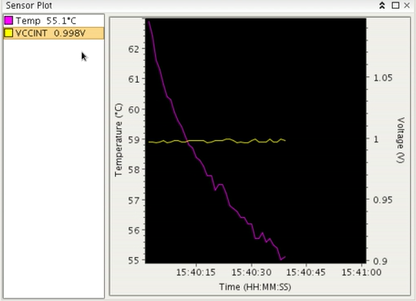

下载进去后,温度急剧下降(.v文件比较简单)(图)

注意:掉电之后再上电,工程又会恢复原来样子!因为没有固化工程!

下节我将描述如何完成Vivado固化至SPI Flash

732

732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?