异步桥异步桥梁的作用就是在不同时钟域的模块之间进行通信。它们可以充当一个中介,确保来自一个时钟域的数据能够被正确地传输到另一个时钟域,并在传输过程中保持正确的同步和时序关系。换句话说,异步桥梁帮助解决了不同时钟域之间的数据传输问题,确保了系统的正常运行和数据的正确性。

1. 如何通信

通信过程通常包括以下步骤:

- 数据准备:在发送端(位于一个时钟域)准备要传输的数据。这可能涉及到将数据从逻辑层面转换为电气信号,或者对数据进行缓冲或格式化等操作。

- 确认和反馈:在需要时,可以在通信双方之间建立一种确认机制,以确保数据的完整性和正确性。这可以通过发送确认信号或者周期性地进行数据校验等方式来实现。

- 数据处理:在接收端,对接收到的数据进行进一步的处理。这可能涉及到解码、解析、存储或者其他操作,根据具体的应用需求来确定。

- 时钟域恢复:在接收端,通过异步桥梁,将传输过来的数据重新与接收端的时钟同步。这包括恢复正确的时序关系,以确保数据能够被正确地解释和处理。

- 数据传输:将数据从发送端传输到接收端。在异步桥梁的控制下,数据被正确地缓冲、转换和传输,以适应接收端的时钟域。

- 时钟域转换:因为发送端和接收端位于不同的时钟域,因此需要在异步桥梁处执行时钟域转换。这可以通过特殊的电路设计来实现,使得异步桥能够接受来自发送端的数据,并使用本地的时钟来控制数据的传输和接收。

通过这些步骤,异步桥梁可以有效地在不同的时钟域之间实现数据通信,并确保正确的同步和数据传输处理,从而满足系统的时序要求。

2. 不同时钟域

不同时钟域指的是在数字电路中由不同时钟信号驱动的逻辑块或模块。在一个系统中,可能存在多个时钟信号,每个时钟信号都对应着一个时钟域。这些时钟域之间可能拥有不同的时钟频率、相位和时钟来源。当两个模块处于不同的时钟域中时,它们的时序关系就会受到影响,可能会导致数据传输的问题,如时序不一致、数据丢失或错误等。

3. spec中的描述:

1)ASYNC_BRIDGE:

For each core, asynchronous bridge on core to L3 coherent interface. For each core present, starting with core 0, set the value to TRUE or FALSE. TRUE:Include an asynchronous bridge for the main bus between core and L3. FALSE :Do not include an asynchronous bridge. 对于每个核心,核心到 L3 一致性接口上的异步桥。对每个存在的核心,从core0 开始,将值设置为 TRUE 或 FALSE。TRUE:在核心与 L3 之间的主总线上包括一个异步桥。FALSE:不包括异步桥。

Note:

The choice affects the internal interface that is used for instruction and data fetch, evictions, and snoops. It does not affect the other interfaces such as debug, trace, and GIC which are always asynchronous.此选择会影响用于指令和数据获取、驱逐和监视的内部接口。它不会影响其他接口,如调试、跟踪和 GIC,这些接口始终是异步的。

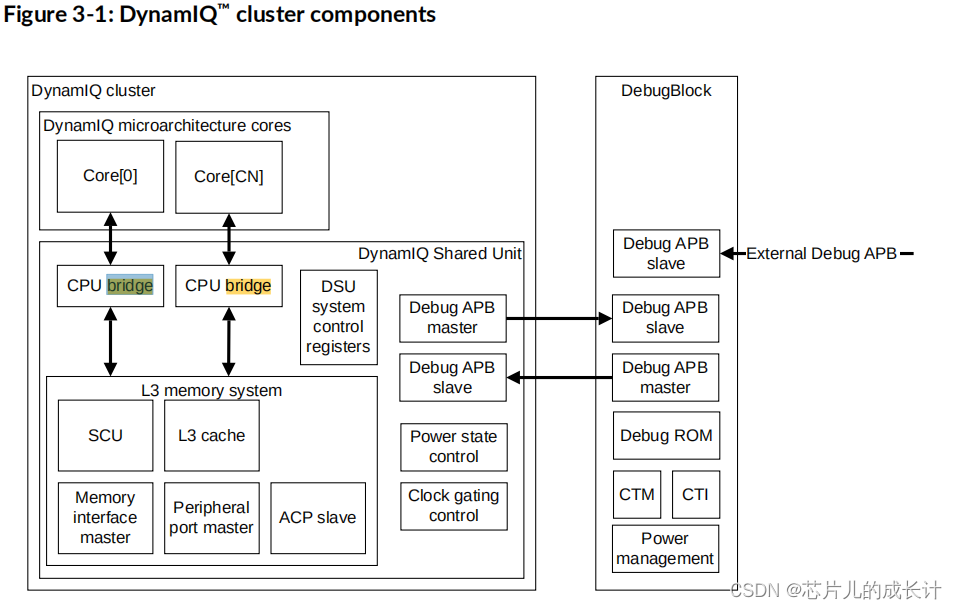

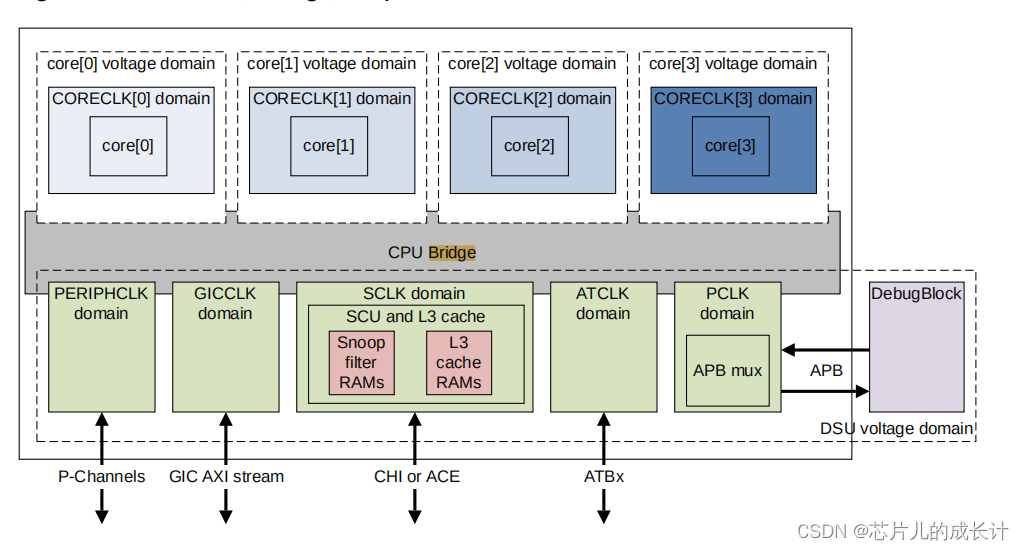

2)CPU bridges

The CPU bridges control buffering and synchronization between the cores and DSU. The CPU bridge RTL is included with the DSU deliverables, but is instantiated in the hierarchy of processor cores.CPU桥控制核心和DSU之间的缓冲和同步。CPU bridge RTL 包含在DSU deliverables中,但在处理器核心的层次结构中被实例化。

3)PCLK

The DebugBlock and cluster both have PCLK inputs. You might choose to connect these to the same clock. Alternatively, you might choose to place an asynchronous bridge between the two clock inputs, in which case they might be different clocks.DebugBlock和集群都有PCLK输入。可以选择将它们连接到相同的时钟。或者可以选择在两个时钟输入之间放置一个异步桥,这样它们可以是不同的时钟。

d. SCLK can run at synchronous 1:1 or 2:1 frequencies with the external interconnect, avoiding the need for an asynchronous bridge between them. SCLK可以以同步1:1或2:1的频率与外部互联运行,从而避免了它们之间需要异步桥的情况。

e. DebugBlock

The CPU Bridge contains all asynchronous bridges for crossing clock domains, and is split with one half of each bridge in the core clock domain and the other half in the relevant cluster domain. Each core can be implemented with or without an asynchronous bridge. If the asynchronous bridge is not implemented, the core is in the SCLK clock domain. CPU桥包含所有用于跨时钟域的异步桥,其中每个异步桥的一半位于core时钟域,另一半位于相关的dsu集群时钟域。每个core都可以选择是否实现异步桥。如果不实现异步桥,则核心处于SCLK时钟域。

The DebugBlock can be implemented in the PCLK domain. However, the DebugBlock might be implemented in a different domain. In this case, asynchronous bridges must be implemented on the APB interfaces between the DebugBlock and the cluster. DebugBlock 可以在PCLK时钟域中实现。然而,DebugBlock 也可能在不同的时钟域中实现。在这种情况下,必须在调试块和集群之间的APB接口上实现异步桥。

本文介绍了异步桥在不同时钟域间的数据通信中的作用,涉及数据准备、确认、时钟同步恢复、时钟转换等步骤,以及在CPU桥、PCLK、SCLK等接口中的应用。

本文介绍了异步桥在不同时钟域间的数据通信中的作用,涉及数据准备、确认、时钟同步恢复、时钟转换等步骤,以及在CPU桥、PCLK、SCLK等接口中的应用。

7763

7763

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?