一、时钟体系结构

CPU-FCLK:400MHZ

AHB总线-HCLK:136MHZ

APB总线-PCLK:68MHZ

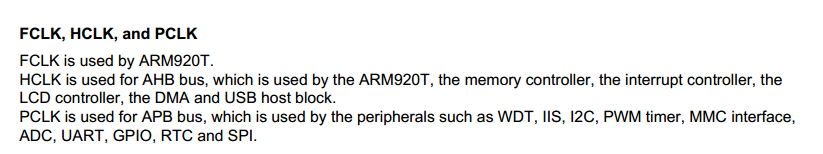

文档解释:

中文翻译:FCLK、HCLK和PCLK,FCLK由ARM920T使用。HCLK用于AHB总线,由ARM920T、内存控制器、中断控制器、LCD控制器、DMA和USB主机块。PCLK用于APB总线,用于WDT、IIS、I2C、PWM定时器、MMC接口等外围设备,ADC、UART、GPIO、RTC和SPI。

问题:如何得到FCLK,HCLK,PCLK和MPLL、HDIV、PDIV?

(假设我们要使用FCLK=400MHZ,HCLK=100MHZ,PCLK=50MHZ——>1:4:8)

第一步:先设置lock time

、

、

/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

第二步:设置CLKDIVN

讲解:

设置CLKDIV的HDIVN[2:1]=10且CAMDIVN[9]=0(默认为0,如果没使用可以不修改):HCLK=FCLK/4

设置CLKDIV的[0]为1:PCLK=HCLK/2

所以设置完后CLKDIV=0x101

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]第三步:设置MPLLCON

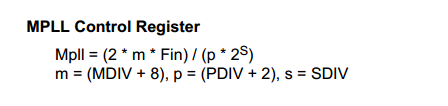

讲解:设置MPLLCON:FCLK=400M→MDIV=92,PDIV=1 ,SDIV=1

m=MDIV+8=92+8=100,p=PDIV+2=1+2=3,s=SDIV=1+2=3

mpll=2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M=FCLK

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

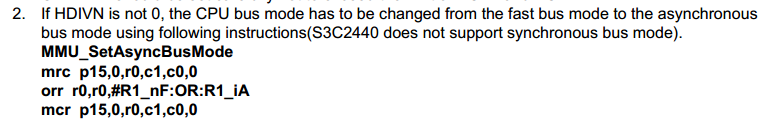

第四步:设置CPU工作于异步模式

所以我们还需要将这段代码拷贝到我们的start.S中去,让CPU处于异步模式

MMU_SetAsyncBusMode

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

二、编写代码(start.S)

.text

.global _start

_start:

/* 关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 设置内存: sp 栈 */

/* 分辨是nor/nand启动

* 写0到0地址, 再读出来

* 如果得到0, 表示0地址上的内容被修改了, 它对应ram, 这就是nand启动

* 否则就是nor启动

*/

mov r1, #0

ldr r0, [r1] /* 读出原来的值备份 */

str r1, [r1] /* 0->[0] */

ldr r2, [r1] /* r2=[0] */

cmp r1, r2 /* r1==r2? 如果相等表示是NAND启动 */

ldr sp, =0x40000000+4096 /* 先假设是nor启动 */

moveq sp, #4096 /* nand启动 */

streq r0, [r1] /* 恢复原来的值 */

bl main

halt:

b halt备注:实例为上一节的led.c

1886

1886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?