vivado MicroBlaze 软核学习

一、学习MicroBlaze软核的一些关键步骤和概念

1、了解MicroBlaze架构:

MicroBlaze是一种RISC(精简指令集计算机)架构,专为Xilinx FPGA和SoC设计。

它是一个轻量级的处理器,具有较小的硅片占用和较低的功耗。

2、启动Vivado项目:

打开Vivado IDE并创建一个新的项目,选择合适的FPGA系列和器件。

3、使用Block Design:

使用Vivado的Block Design功能来可视化地构建系统。

在Block Design中,可以添加MicroBlaze处理器以及所需的外设和内存。

4、配置MicroBlaze:

在Block Design中双击MicroBlaze模块,根据需要配置处理器参数,如时钟频率、中断、缓存等。

5、添加外设:

根据设计需求添加外设,如UART、AXI接口、定时器等。

配置外设与MicroBlaze的连接,设置正确的地址映射。

6、设计AXI互联:

学习AXI(高级扩展接口)协议,理解如何设计AXI互联网络连接处理器、内存和外设。

7、、生成HDL代码:

使用Block Design生成HDL代码,包括Verilog或VHDL文件。

8、实现和综合设计:

在Vivado中实现设计,运行综合和优化。

检查资源使用情况和性能指标。

9、生成比特流:

生成FPGA的比特流文件,准备下载到FPGA硬件中。

10、编写软件程序:

使用Xilinx提供的软件开发工具链,如GCC for MicroBlaze,编写和编译软件程序。

学习MicroBlaze的指令集和编程模型。

11、调试软件:

使用Vivado的调试功能,如ILA(集成逻辑分析器)和Vitis Analyzer,来调试硬件和软件。

12、硬件测试:

下载比特流到FPGA并测试硬件功能。

验证处理器和外设的交互是否符合预期。

13、性能优化:

学习如何优化设计以提高性能,包括流水线、缓存配置和内存访问优化。

14、高级特性:

探索MicroBlaze的高级特性,如中断处理、异常处理和调试支持。

15、查看文档和资源:

阅读Xilinx官方文档,包括用户指南、技术手册和应用笔记。

加入Xilinx社区和论坛,与其他开发者交流经验。

16、实际项目应用:

将MicroBlaze应用于实际项目,解决具体问题,加深理解。

二、原理图输入的方式

1.原理图输入直接调用的IP与逻辑模块代码输入调用的IP是不一致的

两者存在差异,不是同一个IP库,是单独分开的。

原理图输入IP

(1) Slice

作用:可以取位,例:将32位取24位输出。

(2)axi_emc

作用:将axi接口转换为emc接口

(3)Block Memory Generator(BRAM)

BRAM IP 数据存储

(4)Local Memory Bus (LMB)

Local Memory Bus 总线

(5)LMB BRAM Control

Local Memory Bus (LMB) Block RAM (BRAM) Interface Controller 是一个连接 LMB 的模块。 它支持 LMB 总线协议和 字节启用架构。 允许任何不超过 LMB 数据总线宽度的访问量。LMB BRAM 接口控制器是 LMB 和 BRAM 模块外设之间的 接口。一个 BRAM 内存子系统由控制器和实际 BRAM 组件组成,这些组件随 BRAM 模块外设提供。 配合BRAM IP 使用

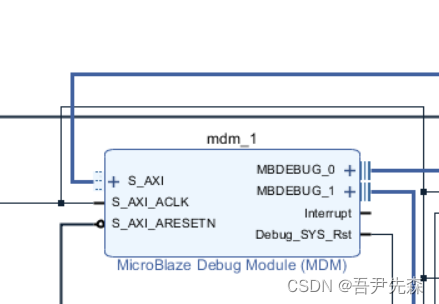

(6)MDM

如下MDM的IP 作用是给软核 Debug时进行使用

2.需要了解的地方

原理图的axi总线的分布与 地址编辑器里的地址分配是一一对应的

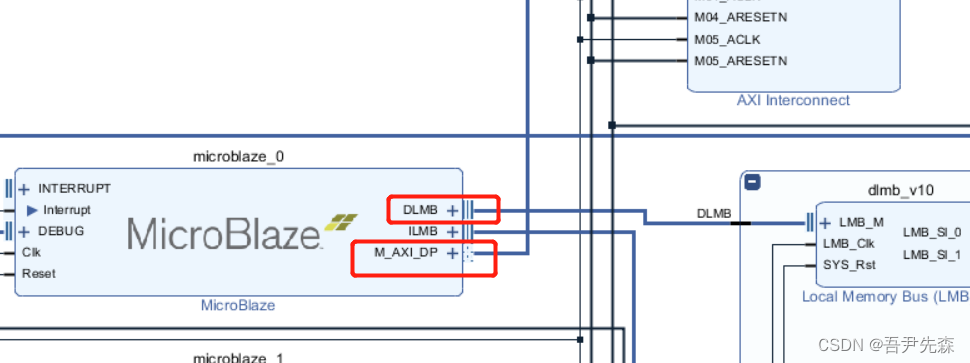

同一个axi的总线上,地址是不能重复的,需要分段分配,不同的axi总线上,地址是不想相关的。如下所示,axi总线与DLMB总线划分到了同一大地址,还不太清楚为什么?

1319

1319

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?