一、MIPI简介?

不需要

各种资料上一大堆对物理层MIPI传输协议的讲解,实话说,我也不是特别能吃透其中的时序,所以不多研究;所有的FGPA如果带MIPI ,那就只研究控制器就行了 ,没必要舍近求远;

二、硬件设计

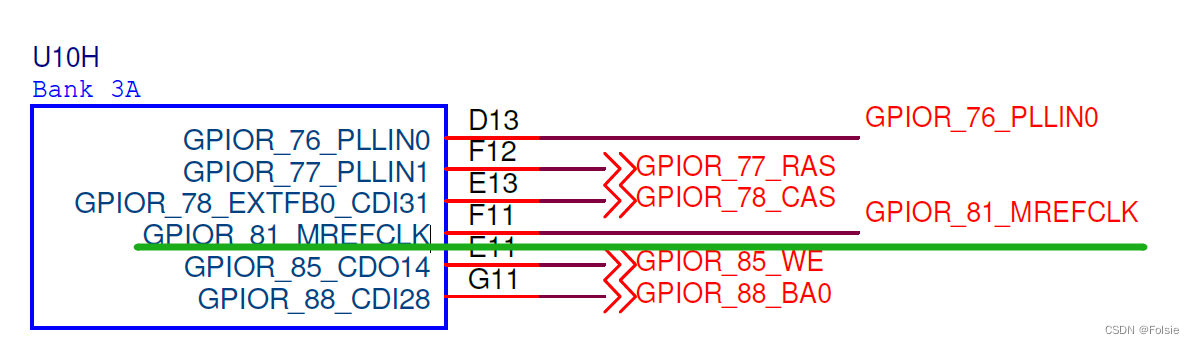

MIPI TX硬核需要外部时钟来做参考,参考时钟频率只能从6M,12M,19.2M,25M,26M,27M,38.4M,52M中选择;

而且,仅MIPI TX 硬核需要使用 MREFCLK,

如果设计中只用到 RX模块 ,该管脚可以不用或者用作普通 GPIO;

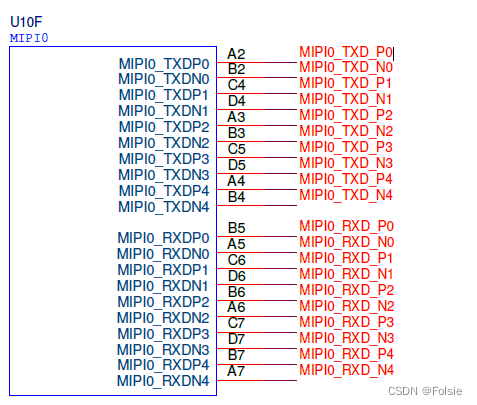

所有的信号线做好差分线该有的处理就行

三.Interface Designer 设计

TX

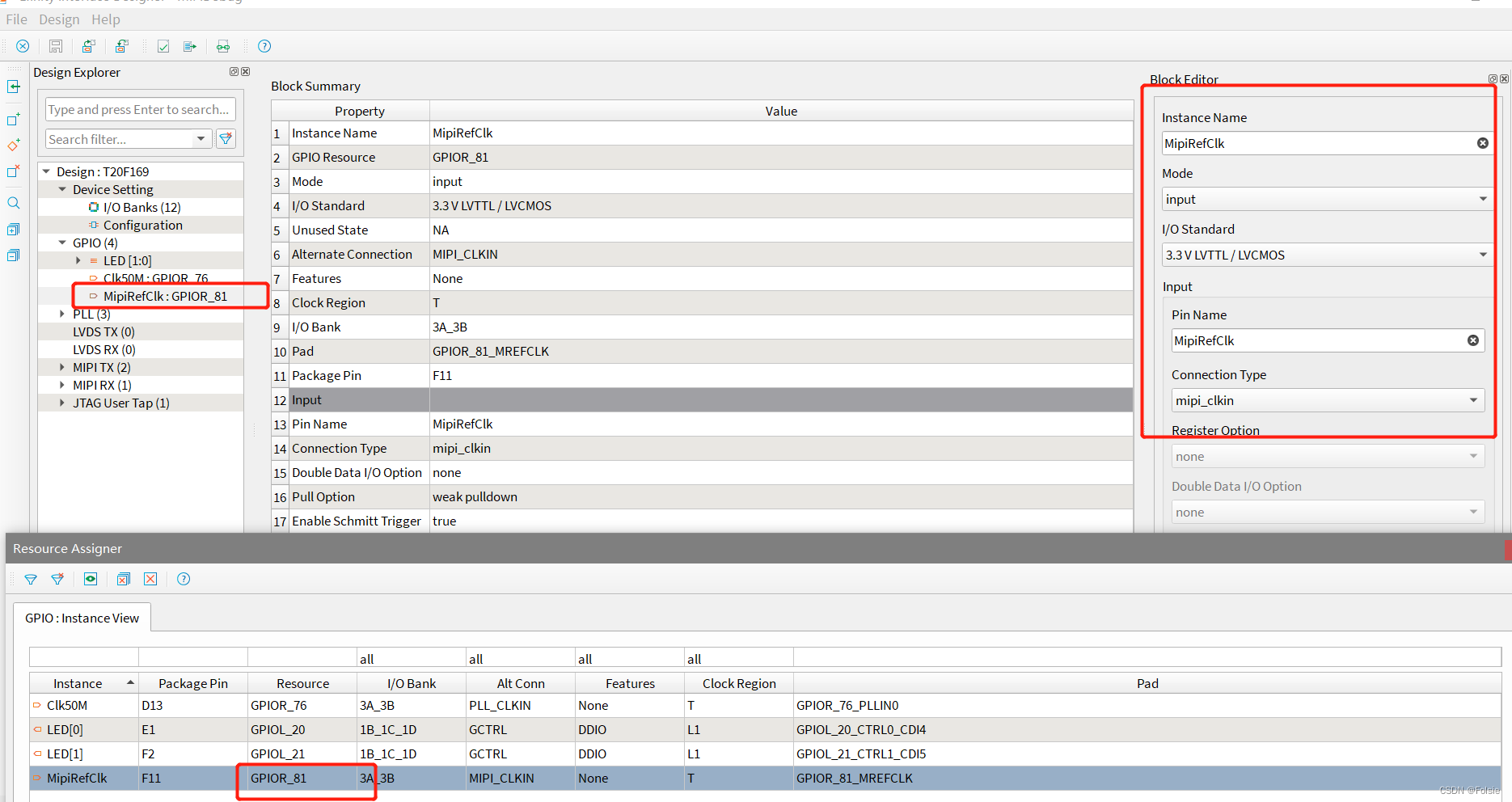

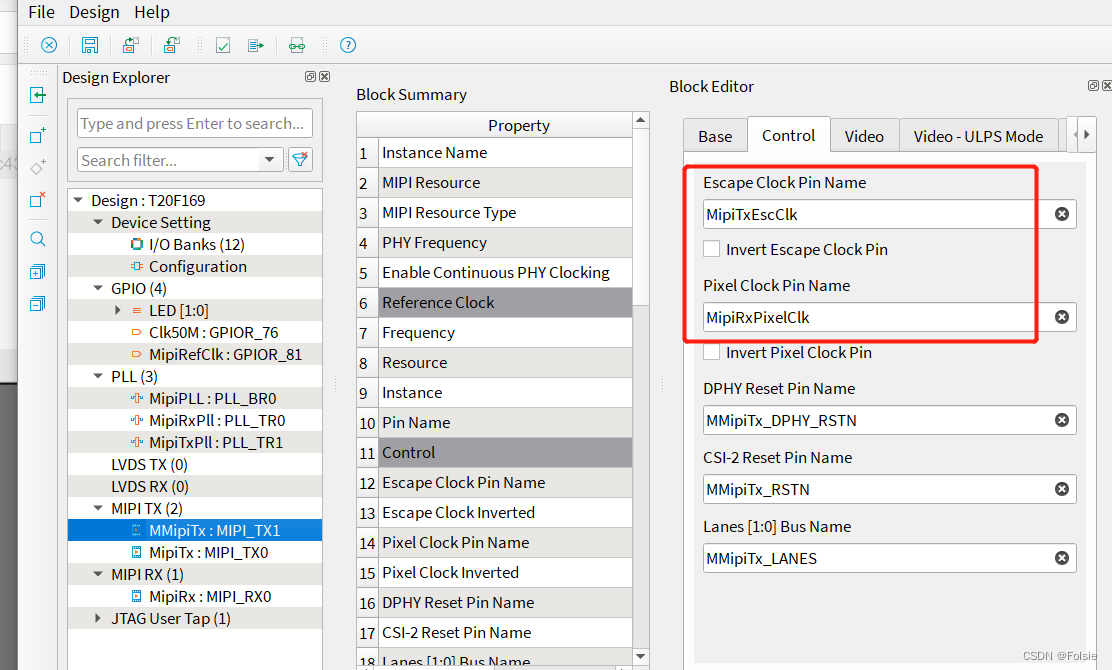

在 GPIO模块里面,创建的参考时钟 MREFCLK 管脚 ,并锁定引脚;

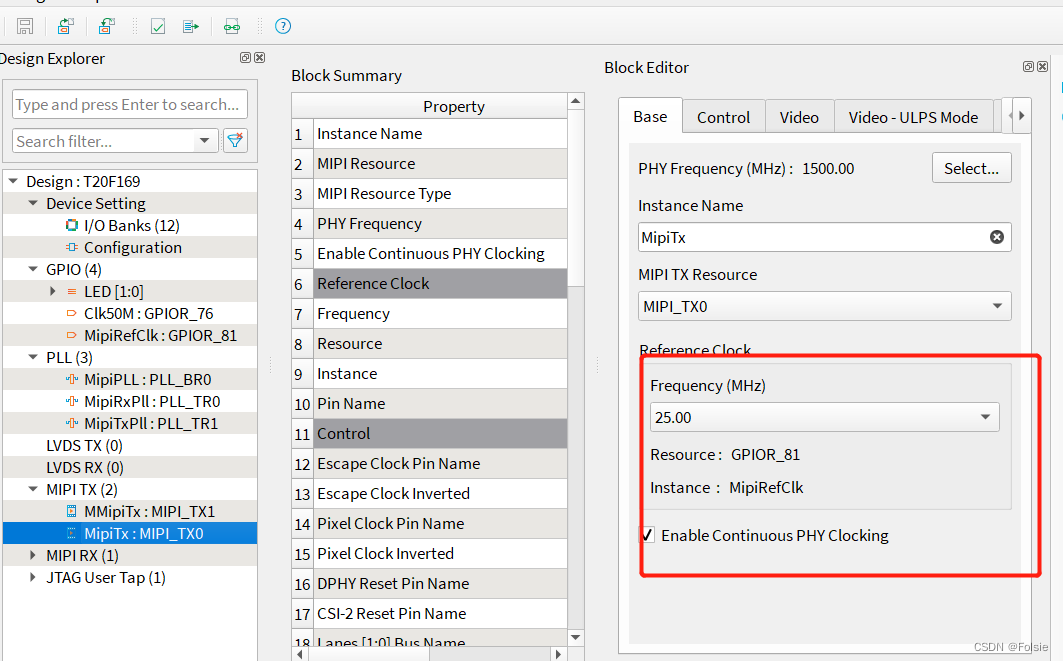

并在TX模块里面匹配板载的频率即可;

TX硬核的Escape 频率 ,11-20M之间 ;

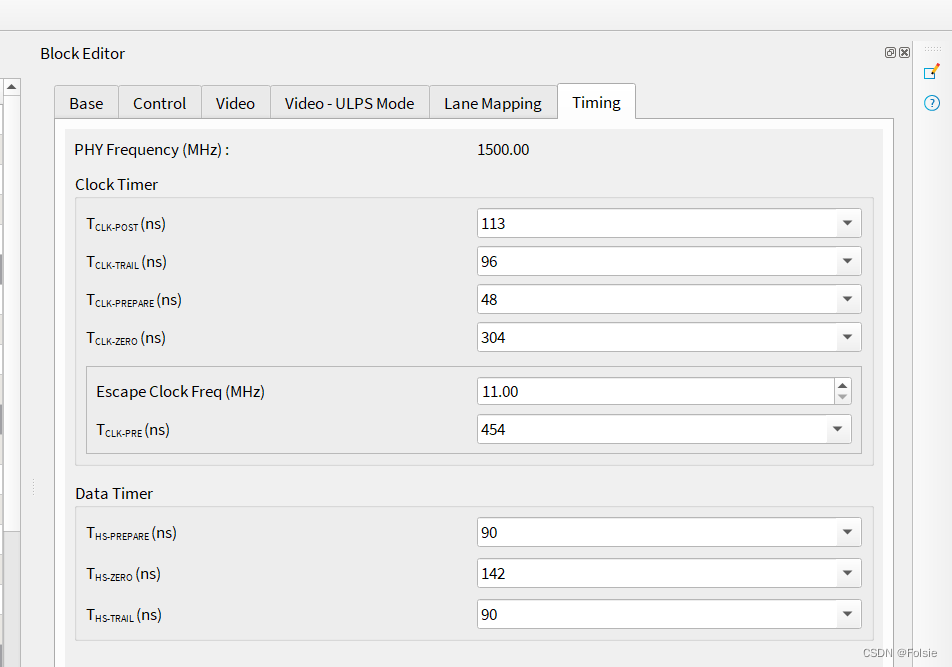

TX 模块 唯一需要注意的

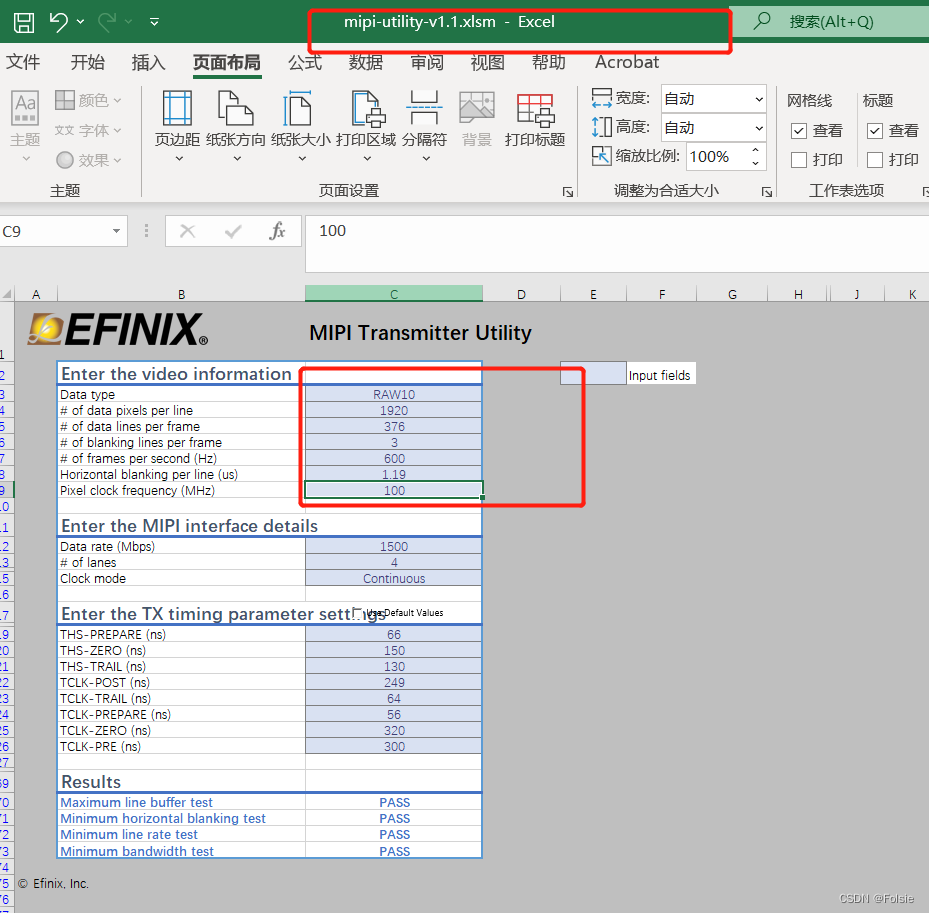

根据原厂提供的MIPI参数配置表 ,完成红框内用户自定义的数据类型和格式,就可以实现上面这些参数可配置的数据;

RX

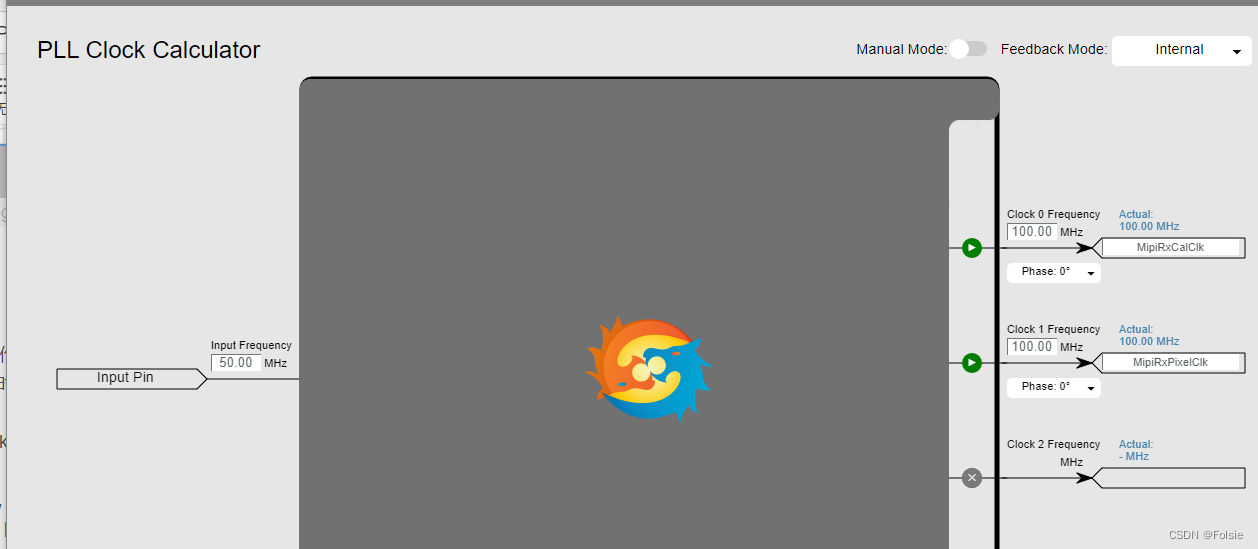

任意一个Gclk 或者 pll-in 接入到 pll的时钟 ,

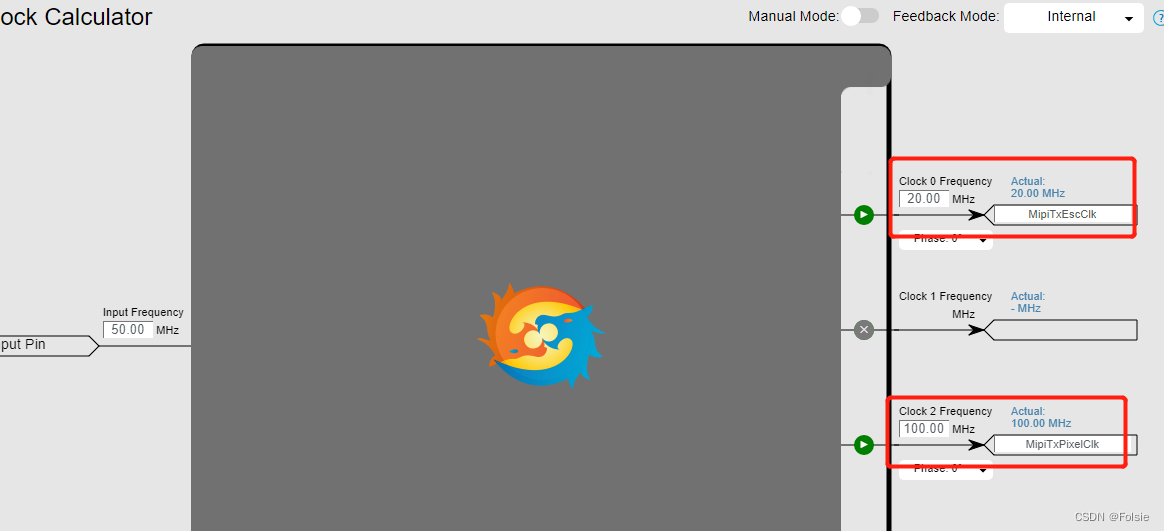

对于 RX 硬核 PLL 输出 两个频率

MipiRxCalClk(80-120M) ,

MipiRxPixelClk(一般给个100M 戳戳有些)

四、代码定义

MIPI硬核链接到逻辑的接口如下 :

//MIPI Tx Signal

input MipiTxEscClk ; //PLL给MIPI phy的 (理论上是可以不接到逻辑的)11-20M

input MipiTxPixelClk ; //PLL给MIPI phy和逻辑的 一般 100-120M

output MipiTx_DPHY_RSTN ; //低有效 拉高最少350us 后才能传数据 建议先复位 笔者习惯等个10ms

output MipiTx_RSTN ; //低有效 拉高最少1个时钟周期 后才能传数据 笔者习惯等个10ms

output [1:0] MipiTx_LANES ; //0 1 2 3 就是 lane 0 ,lanes 0 and 1 ,无 ,lane 4

output MipiTx_FRAME_MODE ; //只要在复位期间才能改;0是一般模式 1是准确模式 默认给0就行

output [15:0] MipiTx_HRES ; //水平分辨率。只能在VSYNC为低时更改 不过一般默认都是给个定值,看你自己应用

output MipiTx_HSYNC ; //行同步

output MipiTx_VSYNC ; //场同步

output MipiTx_VALID ; //数据有效信号

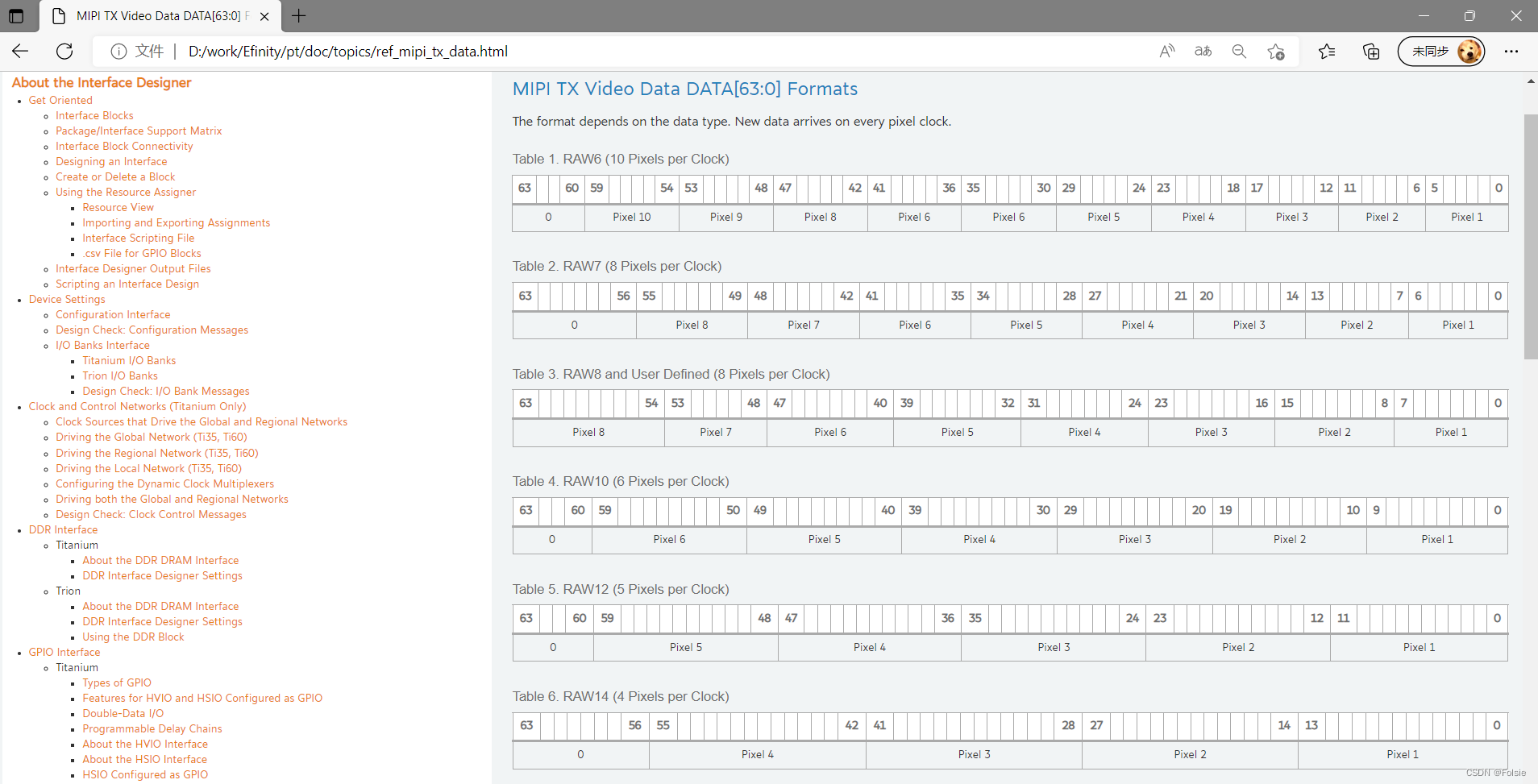

output [5:0] MipiTx_TYPE ; //视频数据类型

output [63:0] MipiTx_DATA ; //具体像素的组合

/

output [1:0] MipiTx_VC ; // 虚拟通道个数 笔者一般不用 给0

output [3:0] MipiTx_ULPS_ENTER ; // ULPS模式是low power 低功耗模式 初学者不用的 赋值0

output [3:0] MipiTx_ULPS_EXIT ; //常量赋值给0

output MipiTx_ULPS_CLK_ENTER; //常量赋值给0

output MipiTx_ULPS_CLK_EXIT ; //常量赋值给0

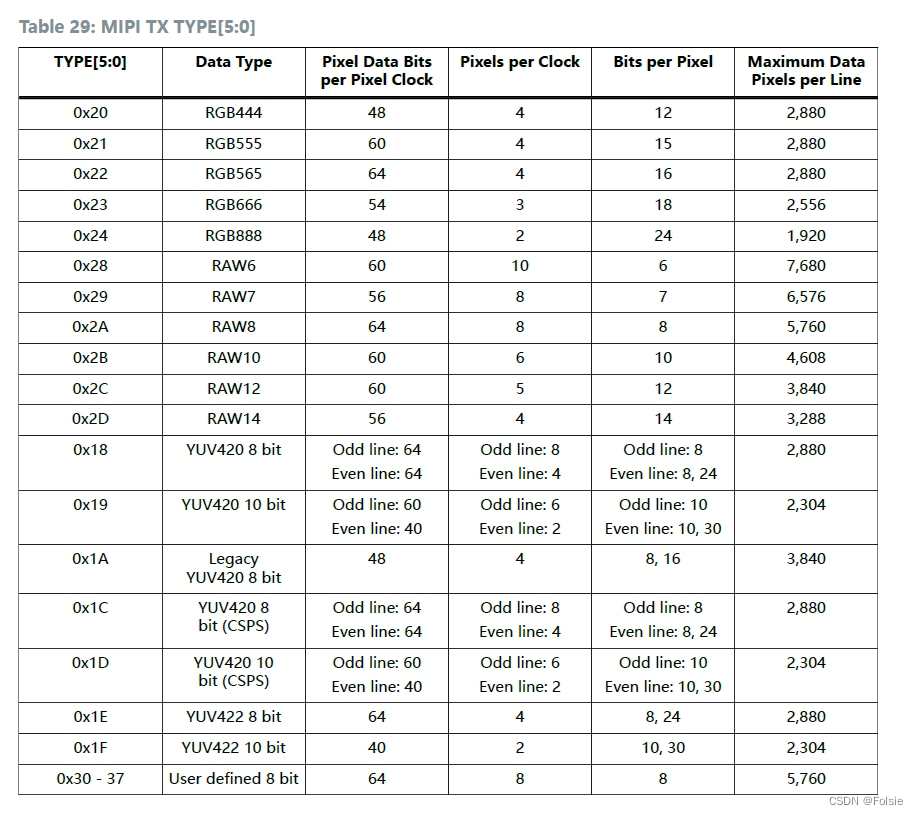

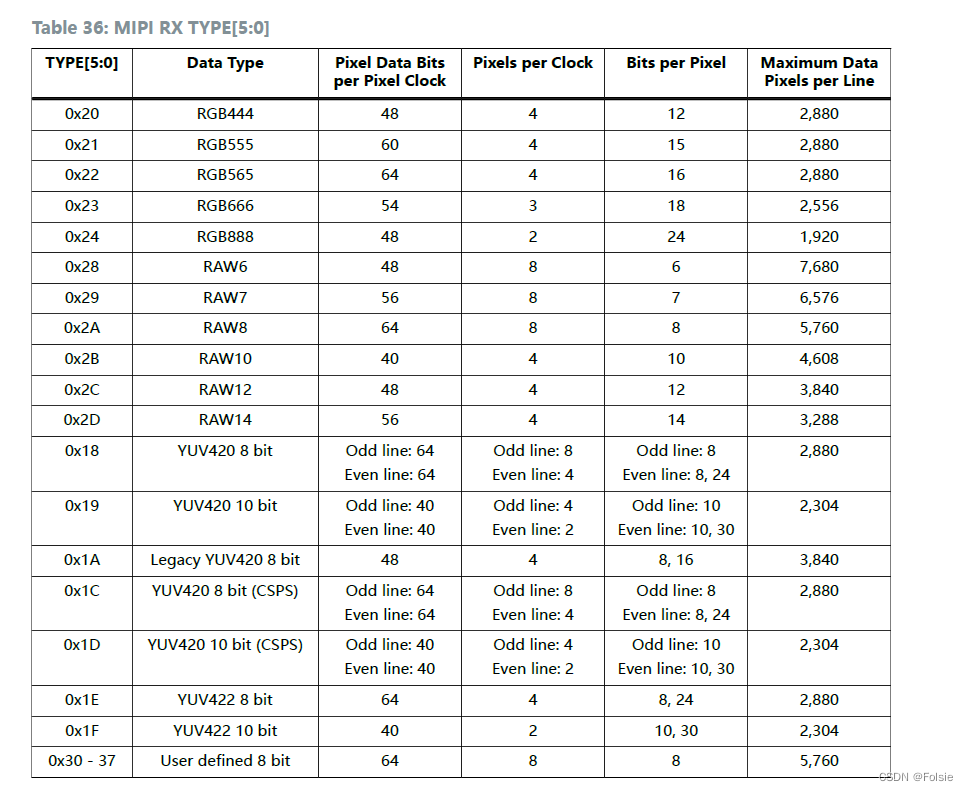

MIPI TX 的 TYPE类型需要用户自定义,定义格式如下图 并把date按照下对应的type类型组合起来

//MIPI Rx Signal

input MipiRxCalClk ; //PLL给MIPI phy的 (理论上是可以不接到逻辑的)80-120M

input MipiRxPixelClk ; //PLL给MIPI phy和逻辑的 一般 100-120M

output MipiRx_DPHY_RSTN ; //低有效 拉高最少350us 后才能传数据 建议先复位 笔者习惯等个10ms

output MipiRx_RSTN ; //低有效 拉高最少350us 后才能传数据 笔者习惯等个10ms

output [ 1:0] MipiRx_LANES ; //0 1 2 3 就是 lane 0 ,lanes 0 and 1 ,无 ,lane 4

input [ 3:0] MipiRx_HSYNC ; //行同步

input [ 3:0] MipiRx_VSYNC ; //场同步

input [ 3:0] MipiRx_CNT ; //(I)[Video] MIPI Rx Valid Pixel Count

input MipiRx_VALID ; //接收数据使能信号

input [ 5:0] MipiRx_TYPE ; //接收的数据类型

input [63:0] MipiRx_DATA ; //接收的数据

output [ 3:0] MipiRx_VC_ENA ; //使能VC通道 不用的赋值0

input [ 1:0] MipiRx_VC ; //VC 通道个数

output MipiRx_CLEAR ; //清除error使能

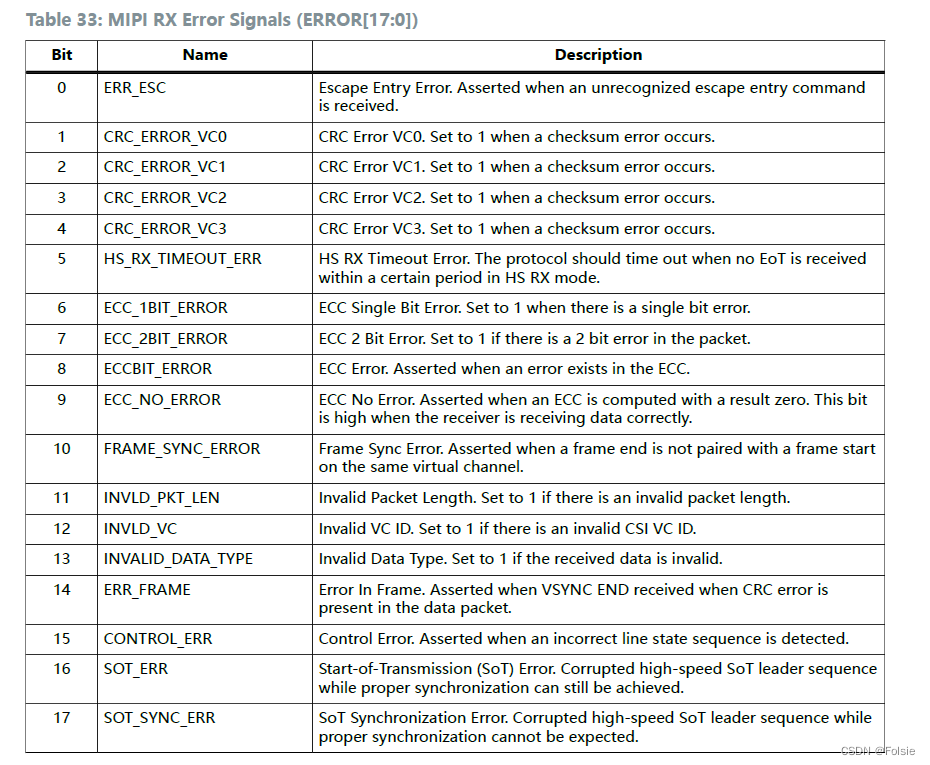

input [17:0] MipiRx_ERROR ; //18根线 每根线指代一个error 手册上有具体描述

input MipiRx_ULPS_CLK ; //如果你没用ULPS 这个就没用 不需要管

input [ 3:0] MipiRx_ULPS ; //如果你没用ULPS 这个就没用 不需要管

RX的TYPE对于逻辑是输入信号,也是按照对应的格式解码就行;

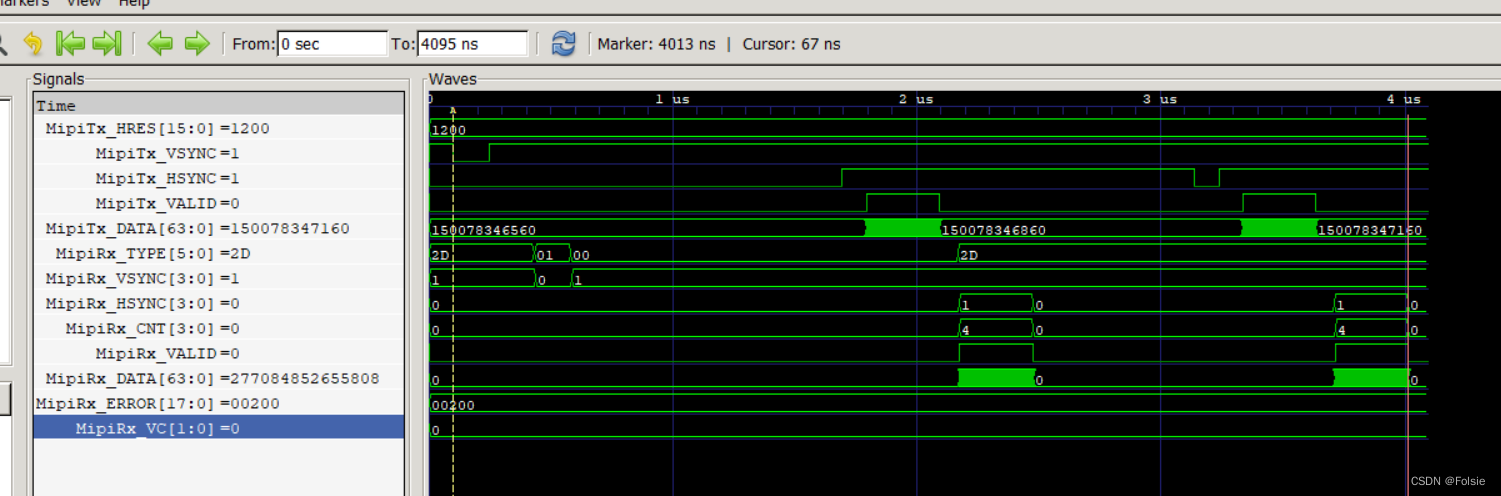

利用官方的Loop-demo 实际回环测验控制器的数据流 就很容易上手;

总结

- MIPI 硬核相当于1个外设 ,隔绝了MIPI的所有复杂协议,用于只需要关注VS,HS ,Valid ,type和64bit data即可;

- 对于RX ,TX pixel 频率的设置 : 举例 MIPI 通道每lane 跑 1.2G ,那总共带宽就是4.8G ,内部MIPI_data 是64bit的 所以4.8G/64=75M ,只要像素时钟大于75M 就行;

1566

1566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?