易灵思FPGA之PLL简介

一.PLL简介

1–PLL 是什么

PLL是一种反馈控制电路,Phase-Locked Loop,简称锁相环。

其特点是,利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2–工作原理

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator) 三部分组成。

简单的PLL由频率基准、相位检波器、电荷泵、环路滤波器和压控振荡器(VCO)组成。

其过程是输入信号-> 鉴相器 -> 低通滤波器 -> 压控振荡器-> 输出信号;

鉴相器有两个输入,分别是输入信号和压控振荡器的输出信号,在二者相位差和频率差不是很大的情况下,鉴相器的输出与两输入信号之差成正比,鉴相器的输出为模拟信号,其通过低通滤波器虑除高频杂波,后进入压控振荡器,压控振荡器的输出频率随其输入电压的改变而改变;

从原理图上看,PLL实际上是一负反馈系统,只要输入信号在正常范围内,输出信号在“一定时间内”都能跟上;

输入信号发生变化后,输出信号跟踪输入信号的过程称之为捕获;

输出信号跟踪完毕时称之为锁定;输入信号变化过快导致输出信号无法跟踪时称为失锁。

二.常见FPGA器件PLL资源概况

1–Xilinx

赛灵思的CMT(clock management tile),CMT由1个MMCM(mixed-mode clock manager)和1个或者2个PLL(phase-locked loop)组成。

MMCM可以有2个时钟输入,2选1,输入时钟经过PFD,CP,LF后产生一定幅度的电压输入到VCO,VCO产生频率与输入电压幅度成比例的高频时钟,再被除以M倍并反馈到PFD。

PLL和MMCM的区别是没有反相输出、动态相位调整等。

这是X家CMT单元的手册

2–Altera

A家器件系列较多,会告诉你有多少个全局时钟和局部时钟资源。

拿C10系列看,有32个全局资源;拿A10器件来看,有32分全局和8~16个局部;而S10直接说有上百个时钟树,足够使用。

这是A10小数分频的架构

这是A10小数分频的架构

这是A10 8路选择的PLL

Altera的每个datesheet里面都有完整的架构说明,和计算参数;详见官网DS。

3–Lattice

L家的就比较简单了,ECP5系列不同型号的PLL资源从2~4个不等。

2路clk输入选择,4路VCO结果的输出,一目了然。

ECP5-DS

三.易灵思内部PLL资源概况

1–PLL资源简介

易灵思第一代产品Trion从4K到120K资源不等,无论大小,内部有都有16个全局时钟资源;而PLL的个数取决于不同的器件和封装,下面是对应型号的最大PLL个数。

| 型号 | T4 | T8 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|

| PLL个数 | 1 | 5 | 5 | 7 | 7 | 8 | 8 |

易灵思第二代产品Titanium内部有有32个全局时钟资源;

而且PLL是做成了硬核,以保证高速倍频下的稳定性。拿做常见的T20F256和T35F324举例。

T20F256-PLL引脚分布

T35F324-PLL引脚分布

Ti60F225-PLL引脚分布

每个PLL都是硬核,对应的的都是固定的引脚(T35F324时钟参考源)。

| PLL | REFCLK0 | REFCLK1 |

|---|---|---|

| PLL_BL0 | GPIOL_15_PLLIN0 | N/A |

| PLL_BR0(6) | GPIOR_138_PLLIN0 | Single-ended: GPIOB_TXP09_CLK0 |

| PLL_BR1 | GPIOR_139_PLLIN1 | Single-ended: GPIOB_TXP15_CLK1_CDI15 |

| PLL_BR2 | GPIOR_140_PLLIN2 | Single-ended: GPIOB_TXP19_CLK2 |

| PLL_TR0 | GPIOR_118_PLLIN0 | Differential: GPIOT_RXP08_CLKP0, GPIOT_RXN08_CLKN0Single-ended: GPIOT_RXP08_CLKP0 |

| PLL_TR1 | GPIOR_119_PLLIN0 | Differential: GPIOT_RXP17_CLKP1, GPOT_RXN17_CLKN1,Single-ended: GPIOT_RXP17_CLKP1 |

| PLL_TR2 | GPIOR_120_PLLIN0 | Differential: GPIOT_RXP25_CLKP2, GPIOT_RXN25_CLKN2,Single-ended: GPIOT_RXP25_CLKP2 |

2–PLL结构

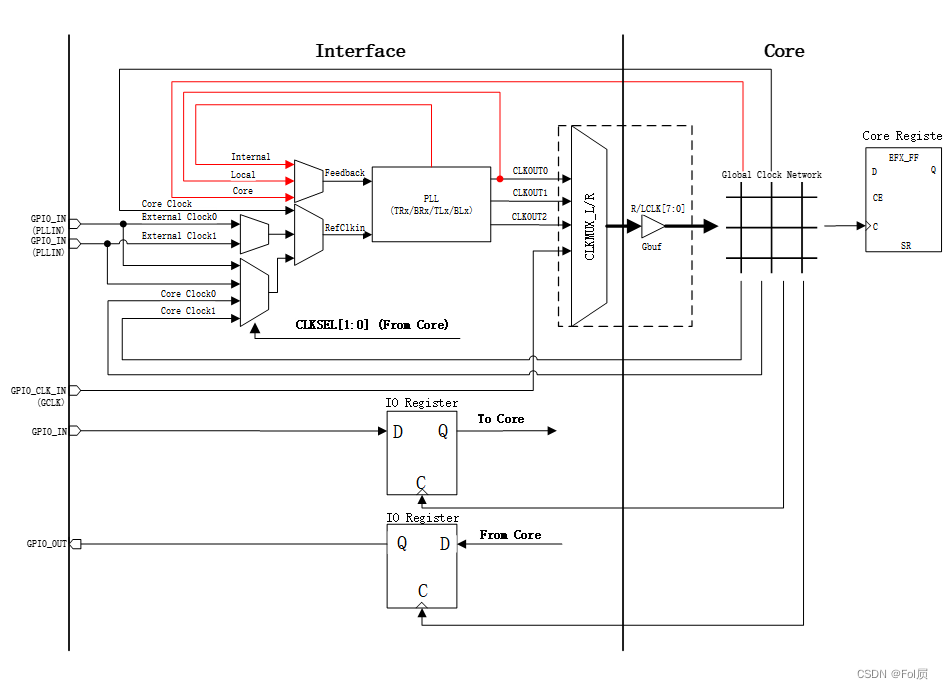

Trion的PLL结构

Titanium的PLL结构

PLL由一个预分频器计数器(N计数器),一个反馈乘法器计数器(M计数器),一个后分频器计数器(O计数器)和输出分频器( C )组成。

note

| 定义 | 定义 | Trion范围 | Titanium范围 |

|---|---|---|---|

| N | 前分频器 | 1-15(整数) | 1,2,4 |

| M | 乘法单元 | 1-255(整数) | 1,2,4 |

| O | 后分频器 | 1,2,4,8 | 1, 2, 4, 8, 16, 32, 64, 128 |

| C | 输出分频 | 2, 4, 8, 16, 32, 64, 128, 256 | 1 - 128 (整数) |

计数器设置定义PLL输出频率:

在计算PLL的过程中,注意的问题 参考时钟(给PLL资源的),PFD ,VCO ,Trion和Titanium都会有不同的范围 ,超过范围软件会报错,届时修改即可;

3–PLL的实际使用

易灵思的PLL资源放在 Interface Deisgner里面,在PLL 下 Create Block 就能新建一个PLL资源;

我们把interface 里面的LVDS,MIPI,PLL,JTAG资源理解为 对逻辑Core (即代码) 的外设 ,只需要管理对逻辑端的设置就好;

我们用T35F324举例(20.2软件版本)

由 GPIO-Block(s) 输入时钟频率,经过PLL硬核模块,计算分频倍频得出所需 VCO ,连线到代码模块,并接受反馈。

1. 如图所示,新建一个PLL资源,初始界面如下,

block_summary 罗列出此PLL基本信息,输入输出频率,放大倍数,相位,vco个数等等。

2. 在PLL Resource 里面选择我们调用的PLL资源,T35F400有7个,如图。

在clock source 里面,有三个选项core模式,external模式,dynamic模式。

2.1

我们在选择Clock Resource为外部连线的同时,已经确定了使用固定的PLL的资源,软件会自动识别并告知这是pad上哪一个管脚。

external模式代表PLL的输入是从引脚上直接给进来的

如图所示 ,在external模式下,使用PLL_TR0时,占用GPIOR_118资源;在使用PLL_TR1时,占用GPIOR_119资源。

2.2

在使用core模式时候,意味着使用接到全局时钟输入作为参考时钟,有两种情况:

这个时钟管脚可以是任意带有CLKx后缀的输入管脚,x必须是数字,先在interface designer里面建立GPIO并命名,锁定硬件上连接的CLKx管脚;

也可以是任意其他PLL资源的输出时钟频率;

将对应的信号填到下图的 Pin name 回车保存。

2.3

本身dynamic模式使用的比较少,意味可以动态选择以上两种模式,不多赘述。

3 VCO与PLL配置

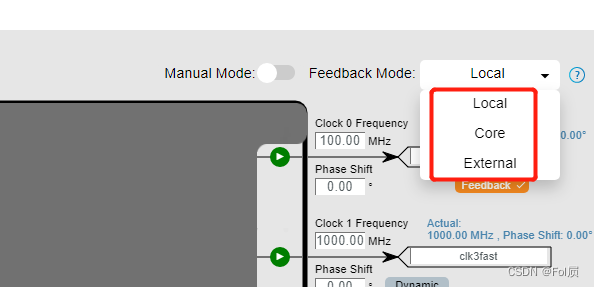

在此界面,我们可输入对应reset信号,输出locked信号,以及选择反馈模式。

3.1

易灵思的每个数据手册上都有说明,Trion其PLL时钟树 是左边8个,右边8个

每一个从Gclk 和 Pll-in 进入的时钟都会占用一个对应列数的全局时钟资源 ,当某一列的clk资源被使用后,EDA工具会自动识别并分配其他的资源,所以在设计的时候需要注意软件报的warnings和error。

一代Trion PLL支持以下模式:

Internal– PLL反馈在PLL内部。不用自己定义反馈时钟;反馈信号不经过clkmux+Gbuf ,数据和时钟之间会有一个Clkmux+Gbuf的延迟;

local–PLL使用clkout0。反馈信号不经过clkmux+Gbuf ,数据和时钟之间会有一个Clkmux+Gbuf的延迟;

core– PLL反馈来自FPGA内核。反馈时钟可以自己选;反馈时钟和参考时钟相位对齐,数据和时钟之间没有延迟,不需要计算。

当PLL输入时钟的来源不一样的时候,时钟和数据的延迟路径也不一样,需要具体分析;

二代 Titanium PLL支持以下模式:

External– PLL反馈在PLL内部。反馈时钟可以自己选;反馈信号不经过clkmux+Gbuf ,数据和时钟之间会有一个Clkmux+Gbuf的延迟;

3.2 输出PLL

一代Trion每个PLL资源最多可以输出3路时钟;

二代Titanium每个PLL资源最多可以输出5路时钟,并简化了以上的手动配置界面,直接输入想要的频率即可;

4 代码参考 : 上文有说 把PLL资源看做成对逻辑的外设

举例:

我们逻辑内需要50M(sclk_50) 100M(sclk_100)125M(sclk_125)

4.1 输入时钟是50M(clock) PLL-IN管脚 进入

// 逻辑内代码 , 不要把板上的50M输入进来,50,100和125M 由PLL-external模式生成

input sclk_50,

input sclk_100,

input sclk_125,

4.2 输入时钟是50M(clock) GCLK管脚 进入

// 逻辑内代码 , 可以直接把50M输入到逻辑内,100和125M 由PLL-core模式生成

input clock,

input sclk_100,

input sclk_125,

4.3 输出需要150M

- PLL Output clock 输出一个150M (sclk_150)

- 在GPIO资源内新建一个管脚 ,选clkout ,在Pin name 里面输入sclk_150 回车保存即可;

5 分配具体引脚

如上所示,分配引脚并锁定,点击save,check,最后生成Constraint Files,完成配置。

5 注意事项

5.1 在使用DDR控制器的时候,PLL_BR0只能从对应的PLLIN管脚输入,不能用GCLK管脚输入,也不能用上一级的锁相环的输出作为参考时钟。

5.2 PLL达到锁定时变高;当检测到锁丢失时,它变为低电平。在您的设计中连接此信号以监视锁定状态。该信号是模拟异步信号。

5.3 在相移过程中,

相移CLKOUT 0、45、90、135、180或270度。

180和270要求C分频器为2。

45和135要求C分频器为4。

90要求C分频器为2或4。

要相移225度,请选择45并反转目的时钟。

要相移315度,请选择135并反转目的时钟。

5.3 差分信号的话,只能选择PLL进入,选对外部clock来源即可;

四.总结

在实际工程的移植和操作过程中会遇到各种问题,需要灵活去解决。

例如在原始工程中,PLL是四输出的,而EFinix的3输出的,我们可以使用两个PLL资源去替换。

1, 外部参考时钟如果从GCLK管脚输入,两个PLL的Clock source都用core模式,feedback mode选择local或者core。这样两个锁相环输出的时钟都是对齐的。,

2, 外部参考时钟如果从PLLIN管脚输入,PLL_1的Clock source用external模式,feedback mode用local或者core。PLL_2的 clock source用core模式,参考时钟使用PLL_1的其中一个输出时钟,feedback mode用local或者core。

3, 一代Trion不支持动态切换输出频率,所以得用一些取巧的办法,单端信号可以用DDIO做,差分信号可以用Lvds输出做;

本文详细介绍了锁相环(PLL)的工作原理、常见FPGA器件如Xilinx、Altera和Lattice的PLL资源概况,以及易灵思(Efinix)FPGA内部PLL的资源和使用方法。PLL作为一种关键的时钟管理技术,常用于频率合成和相位同步。在易灵思的器件中,PLL资源配置和使用涉及预分频器、乘法器、后分频器和输出分频器等组件,并提供了多种配置模式以适应不同的设计需求。

本文详细介绍了锁相环(PLL)的工作原理、常见FPGA器件如Xilinx、Altera和Lattice的PLL资源概况,以及易灵思(Efinix)FPGA内部PLL的资源和使用方法。PLL作为一种关键的时钟管理技术,常用于频率合成和相位同步。在易灵思的器件中,PLL资源配置和使用涉及预分频器、乘法器、后分频器和输出分频器等组件,并提供了多种配置模式以适应不同的设计需求。

3747

3747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?