一、MIPI DSI简介

如何解MIPI包 这是控制器的活,一般模式下 ,我们能用Command和vedio模式就行

二、IP核 学习思路

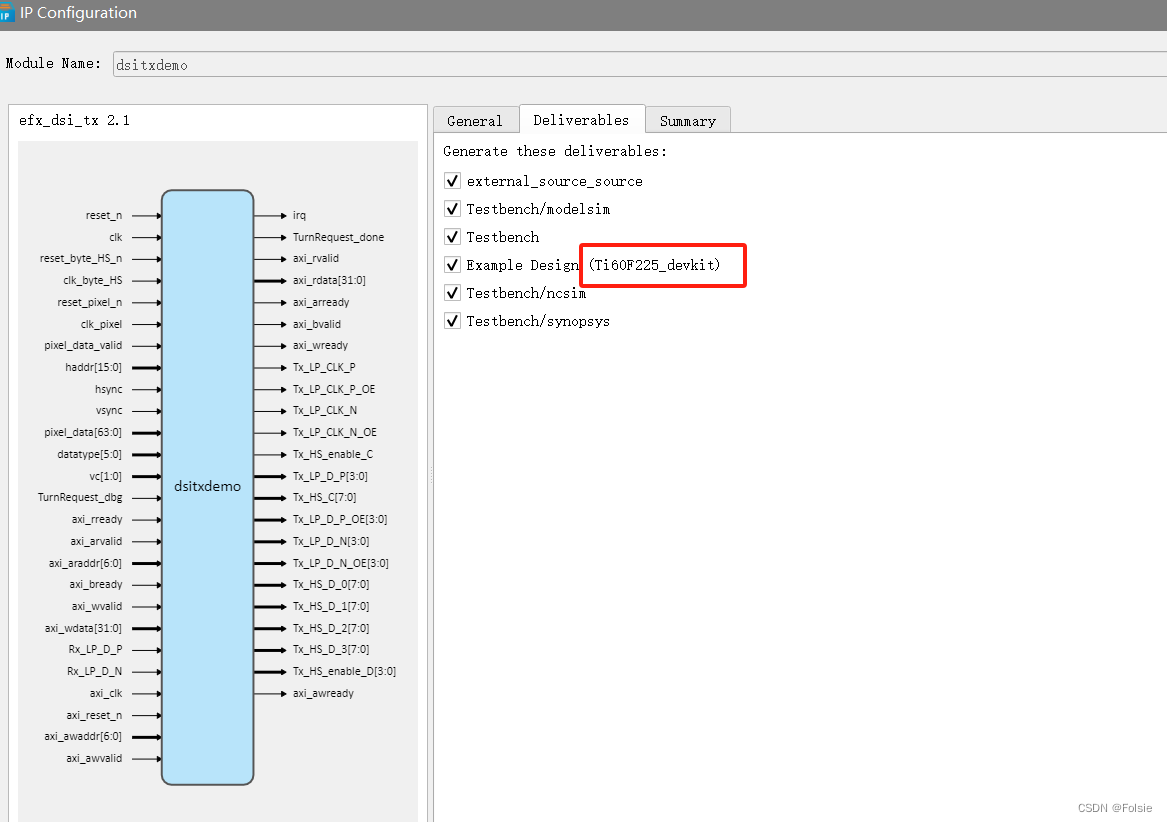

使用IP 生成 对应的 Example Design

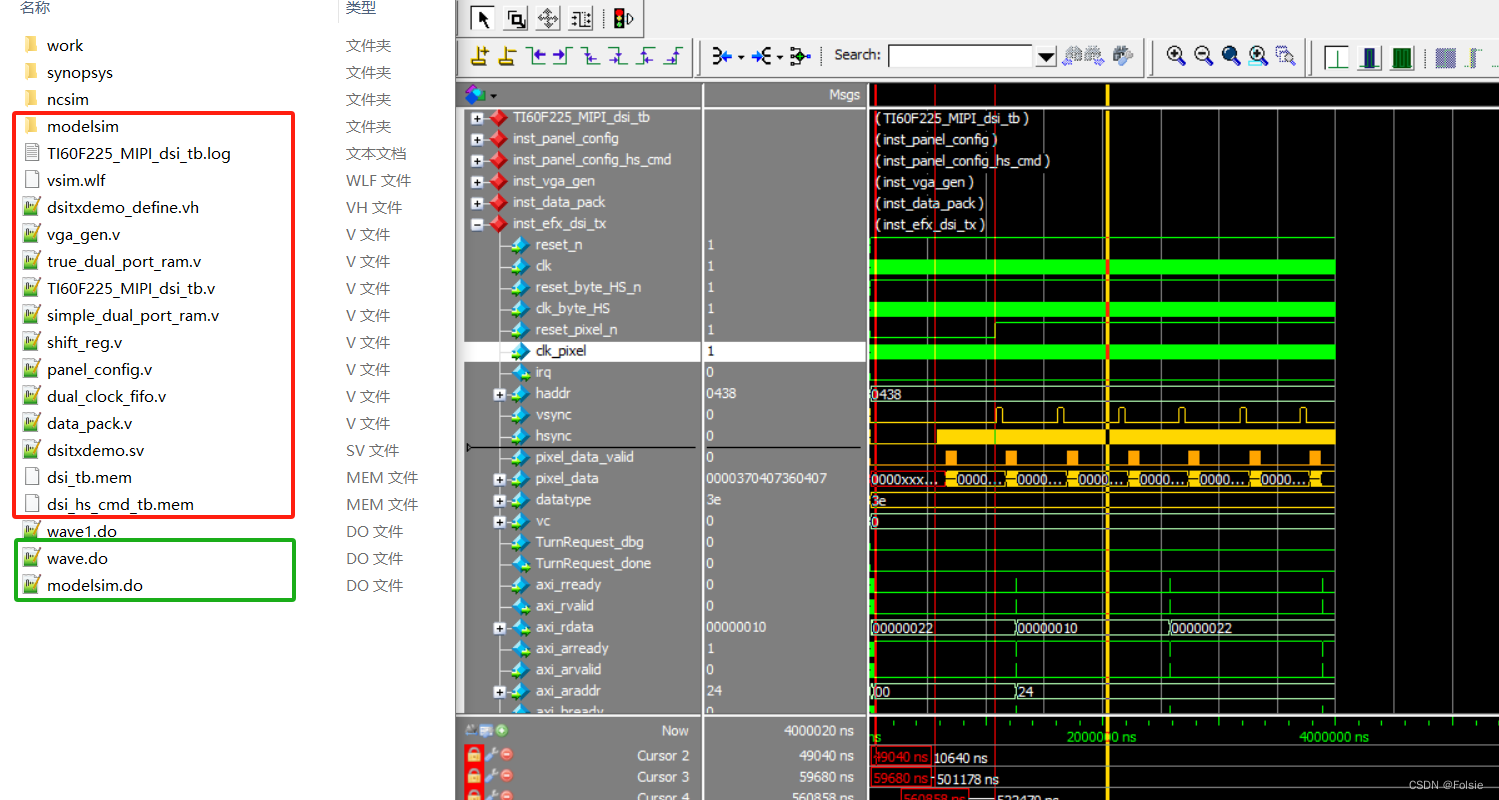

找到IP底下的Testbench 文件夹 ,如图,红色是他提供的文件,和example工程一致,绿色的仿真脚本自己完善,强烈建议 先仿真,然后学时序:

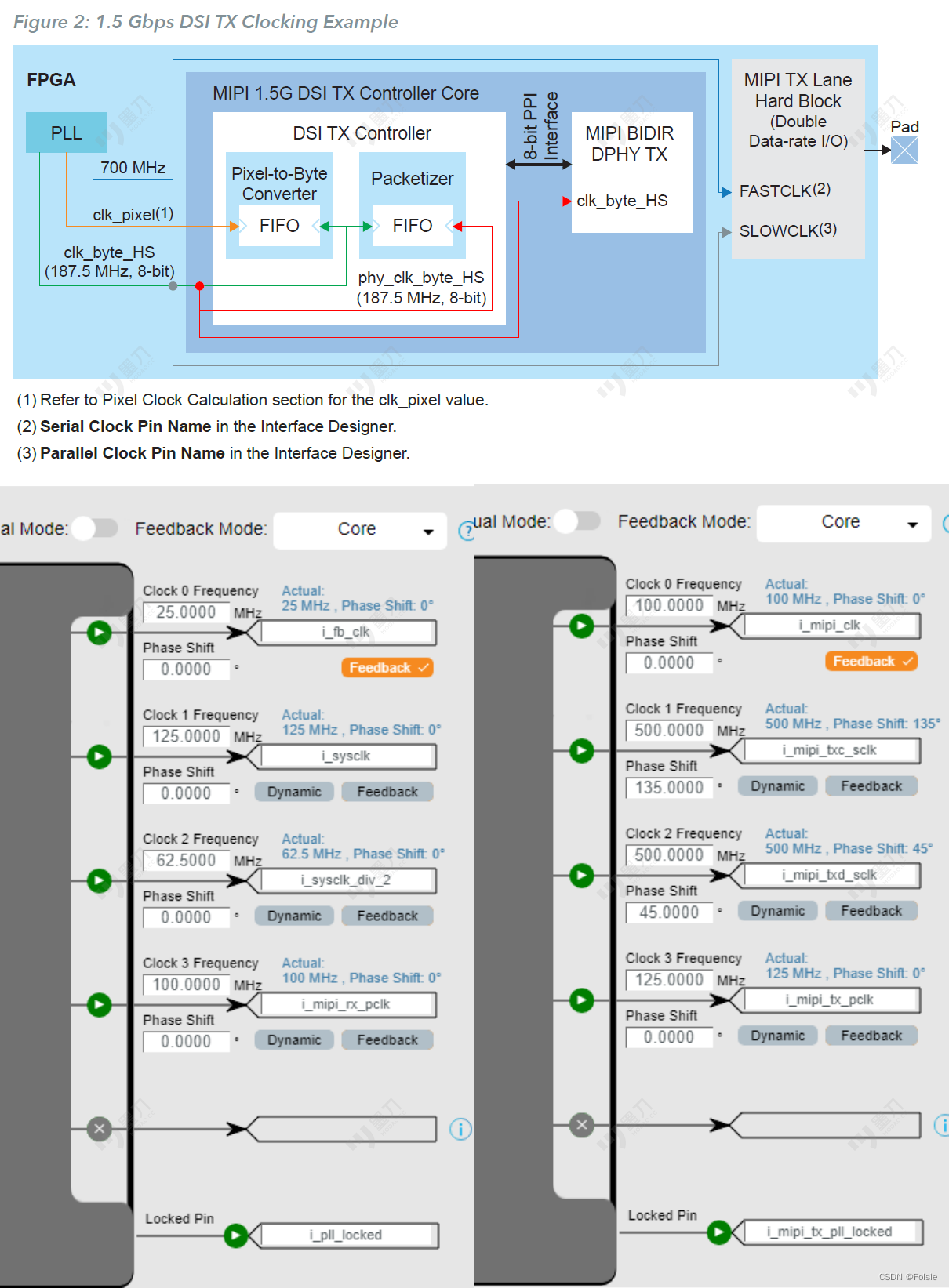

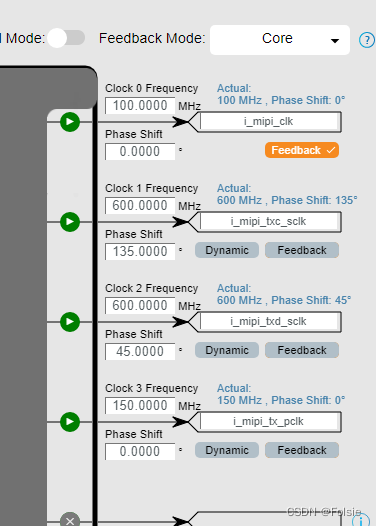

研究时钟树

整个 DSI TX controller的时钟共有4个 :

i_mipi_clk 是IP 控制器 运行的速度 ,和 数据没有任何关系,默认给100M即可;

i_mipi_tx_pclk 是字节时钟 ,是线上速度的 八分之一;

i_sysclk_div_2 是像素时钟,RGB888 一次传两个像素 ,所以是字节时钟的一半;

i_fb_clk 是 AXI4 配置dphy 寄存器时钟 ,默认25M即可;

这几个时钟互相没有相位关系;

// MIPI DSI TX Channel

.reset_n (w_sys_dp_arstn ),

.clk (i_mipi_clk ), // 100

.reset_byte_HS_n (w_sys_dp_arstn ),

.clk_byte_HS (i_mipi_tx_pclk ), // 125

.reset_pixel_n (r_rstn_video ),

.clk_pixel (i_sysclk_div_2 ), // 62.5

//AXI4-Lite Interface

.axi_clk (i_fb_clk ),

官方的demo 工程是

像素时钟是 62.5M ,数据是1080*1920@50@24bit == 2.488 Gbps ;

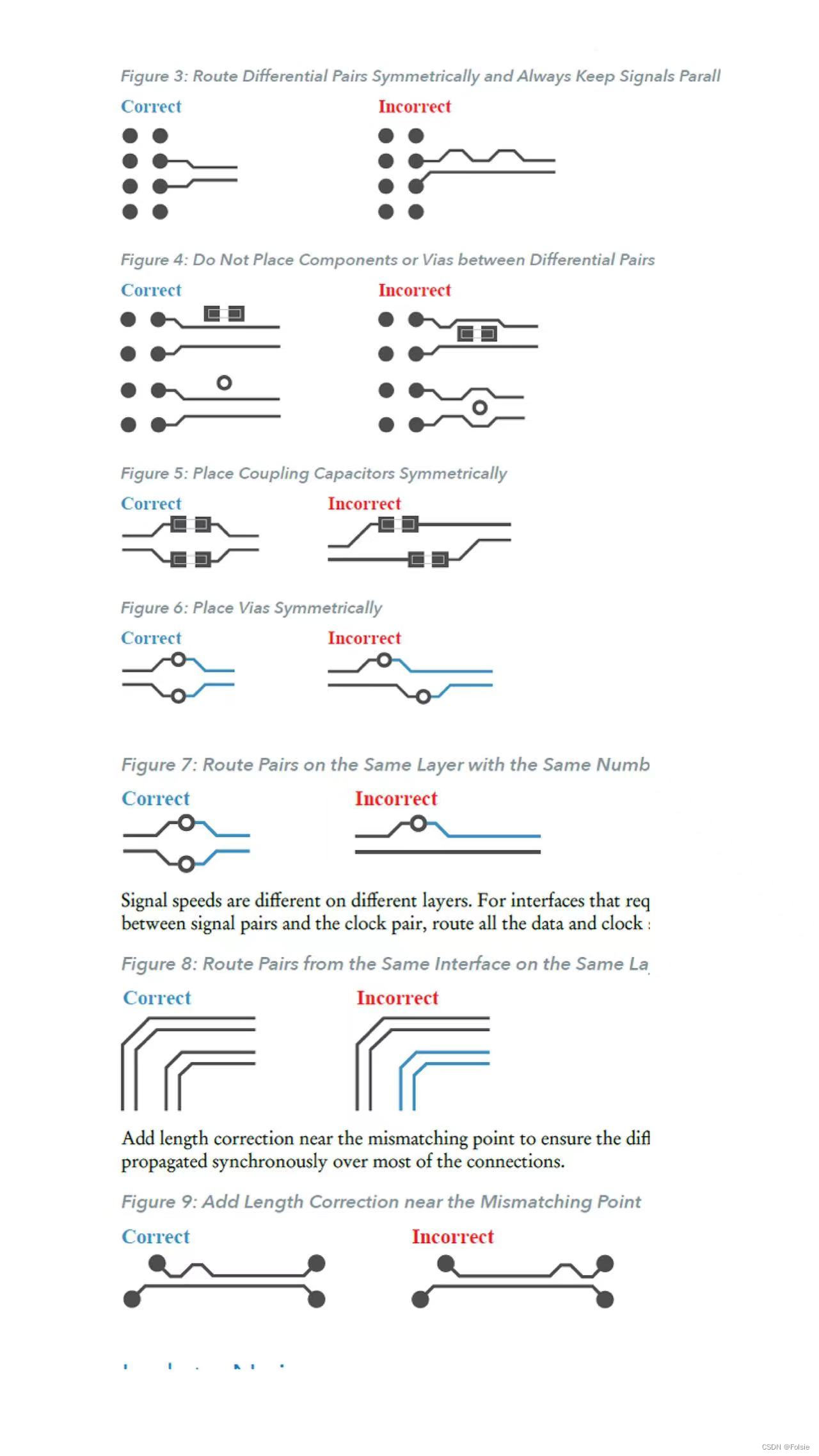

三、硬件设计

差分阻抗 标准100欧姆;其他就是等长处理;

四.移植指南

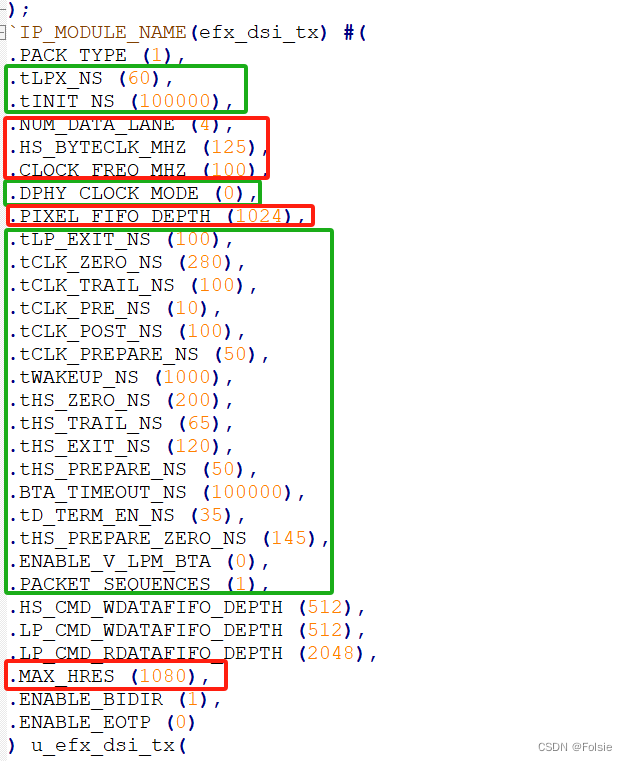

demo工程是基于F225开发板点亮手机屏幕,屏幕参数为1080*1920@50@24bit ,工程参数 MIPI跑4lane ,每lane 跑1Gbps ,字节时钟是125M,

所以 移植起来

-

修改interface designer 里面 dphy快速时钟,字节时钟,像素时钟;

-

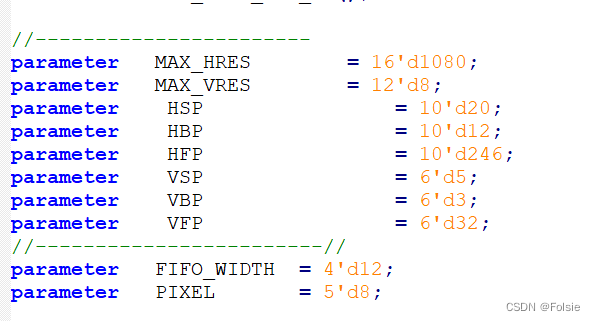

修改 顶层文件中 行场的前沿后沿参数;

-

修改 dphy_IP 里面 时钟 ,FIFO 等参数;

-

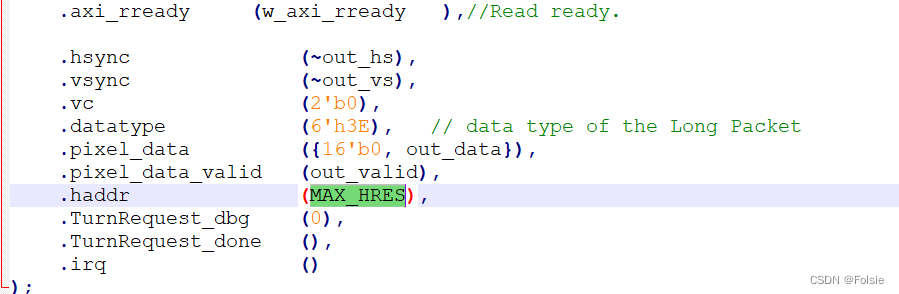

修改 dphy_IP 里面 数据类型,一行像素个数,虚拟通道等参数;

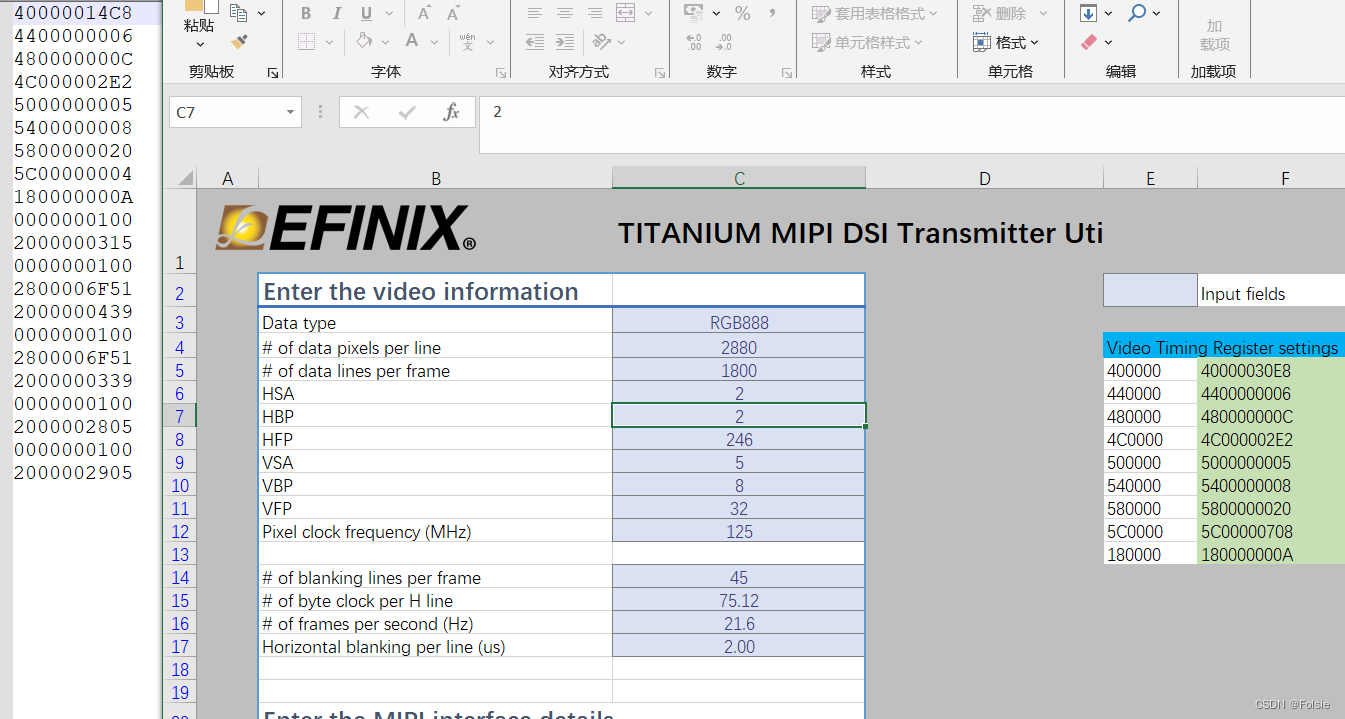

- 根据 Titanium-mipi-utility-v1.3.xlsm 表格 ,填写正确的屏幕寄存器参数 ,更改寄存器配置;

692

692

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?