记录一下来青软之后做的第一个项目:D触发器,DFRB1C。

平台:IC617

1. 绘制原理图

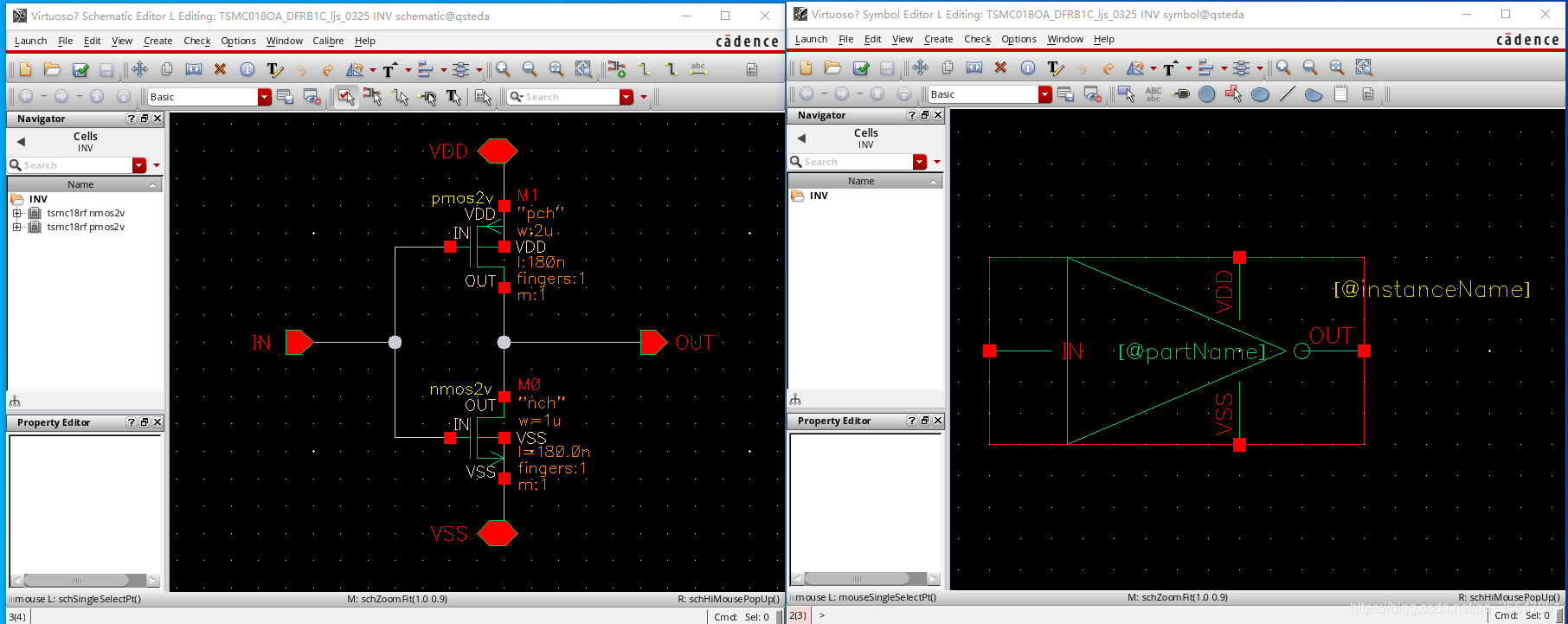

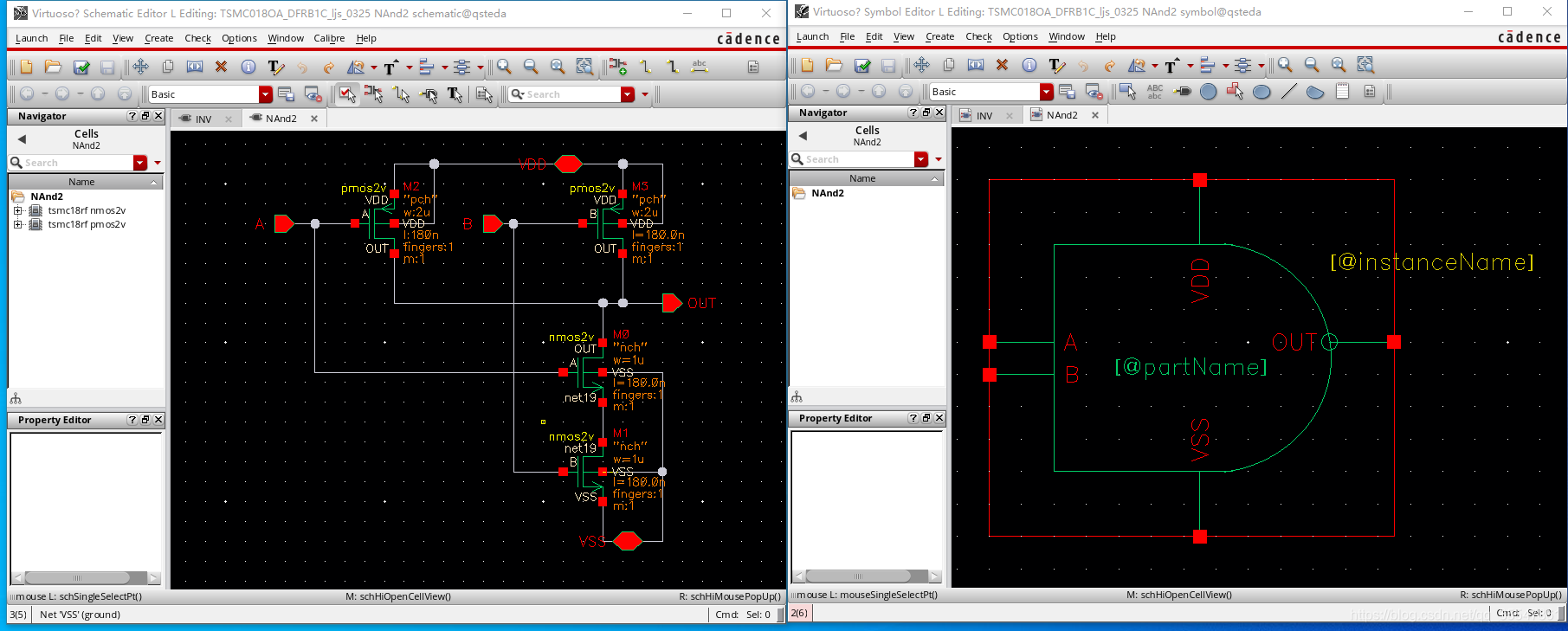

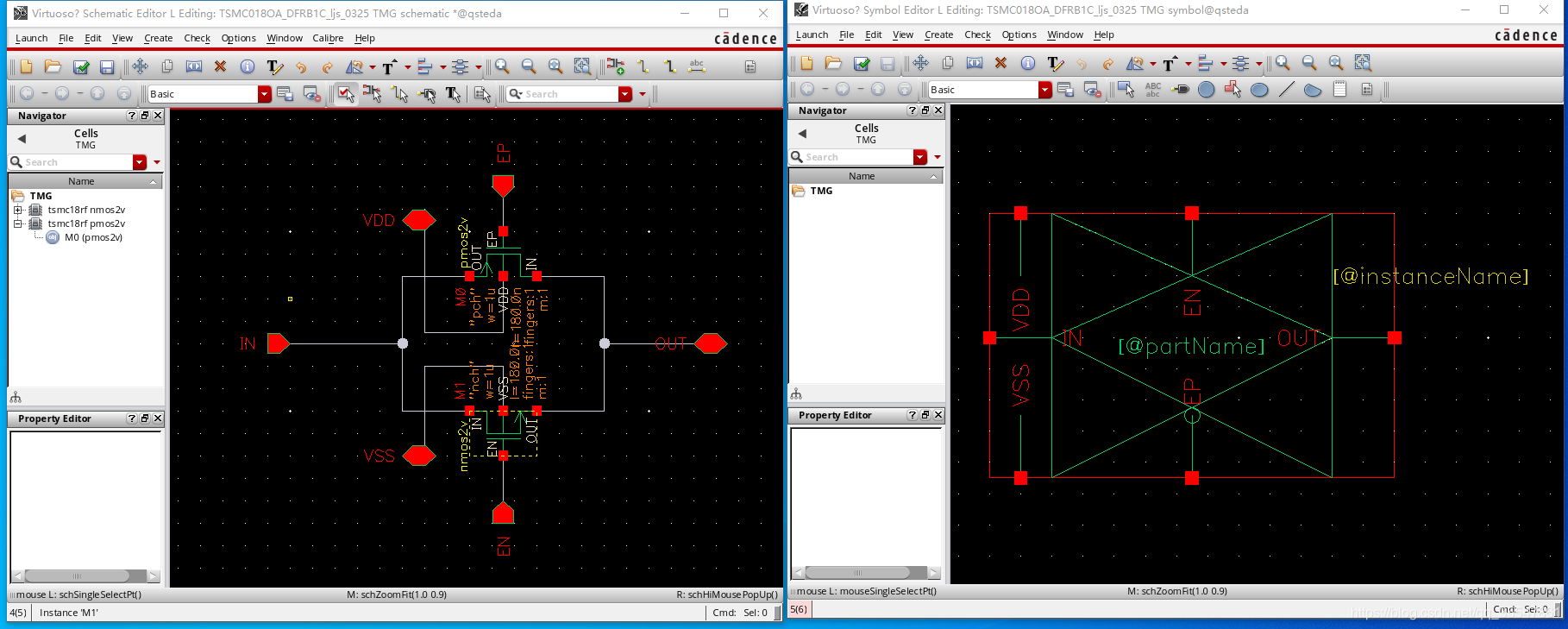

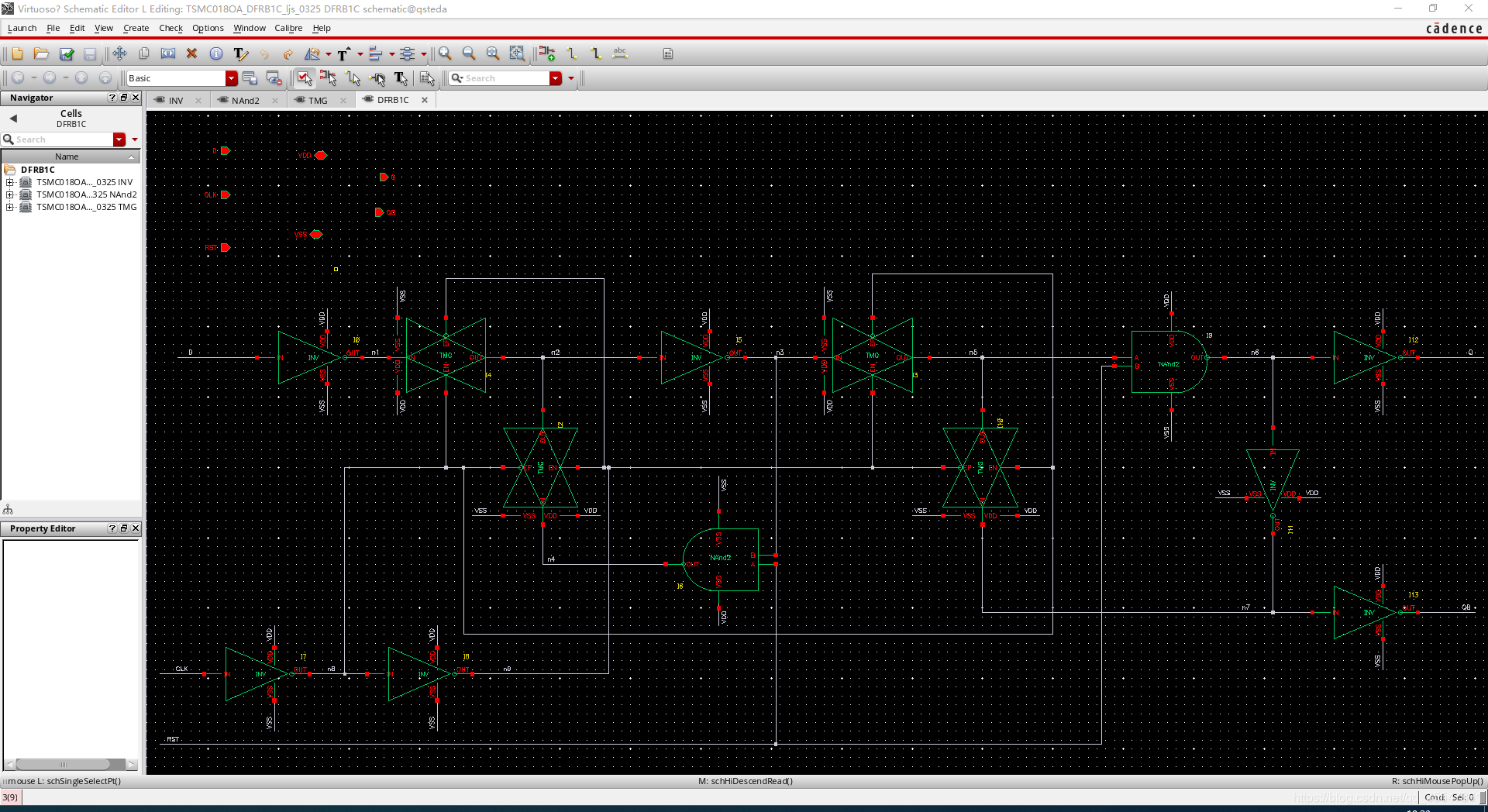

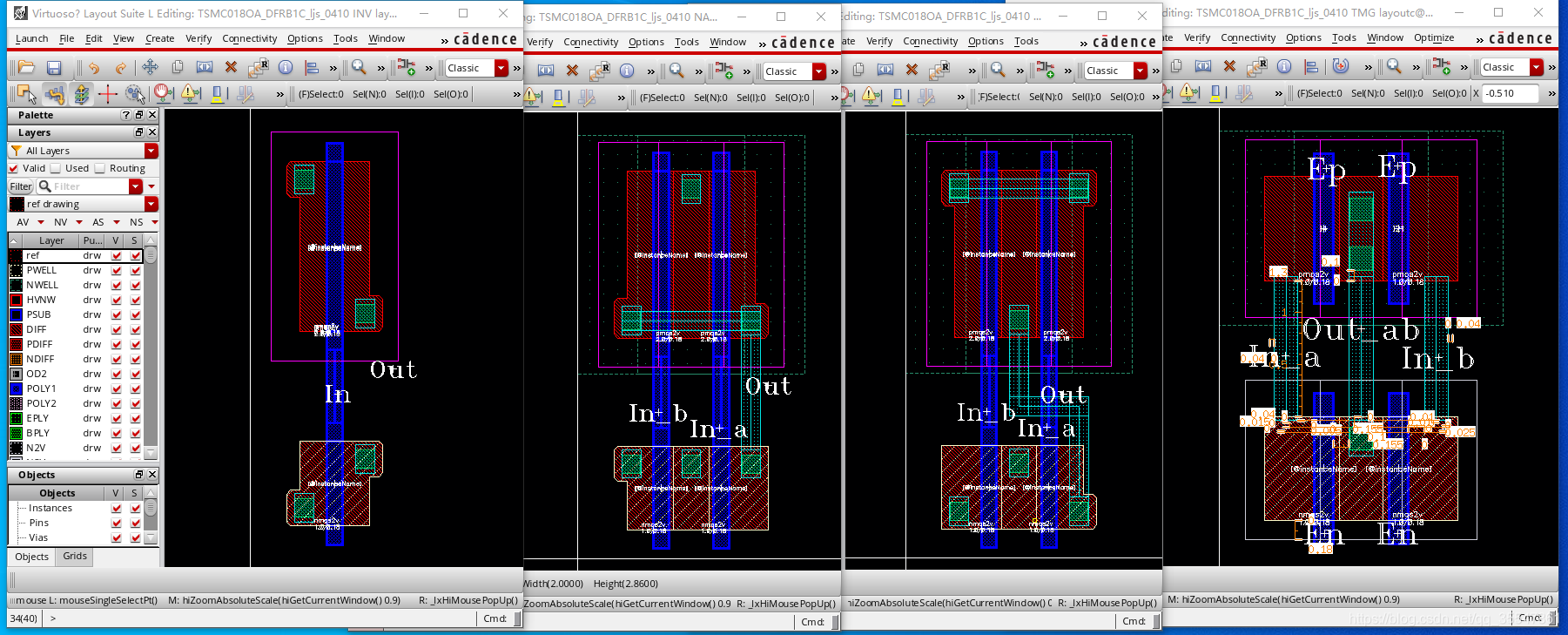

建立schematic类型的view,并进行绘制,其中绘制了若干子模块的电路图,例如与非门、反相器以及传输门,然后将他们生成symbol,经由顶层原理图的调用,形成D触发器。

反相器schematic及symbol(上图)

与非门schematic及symbol(上图)

传输门schematic及symbol(上图)

D触发器schematic(上图)

2. 绘制版图

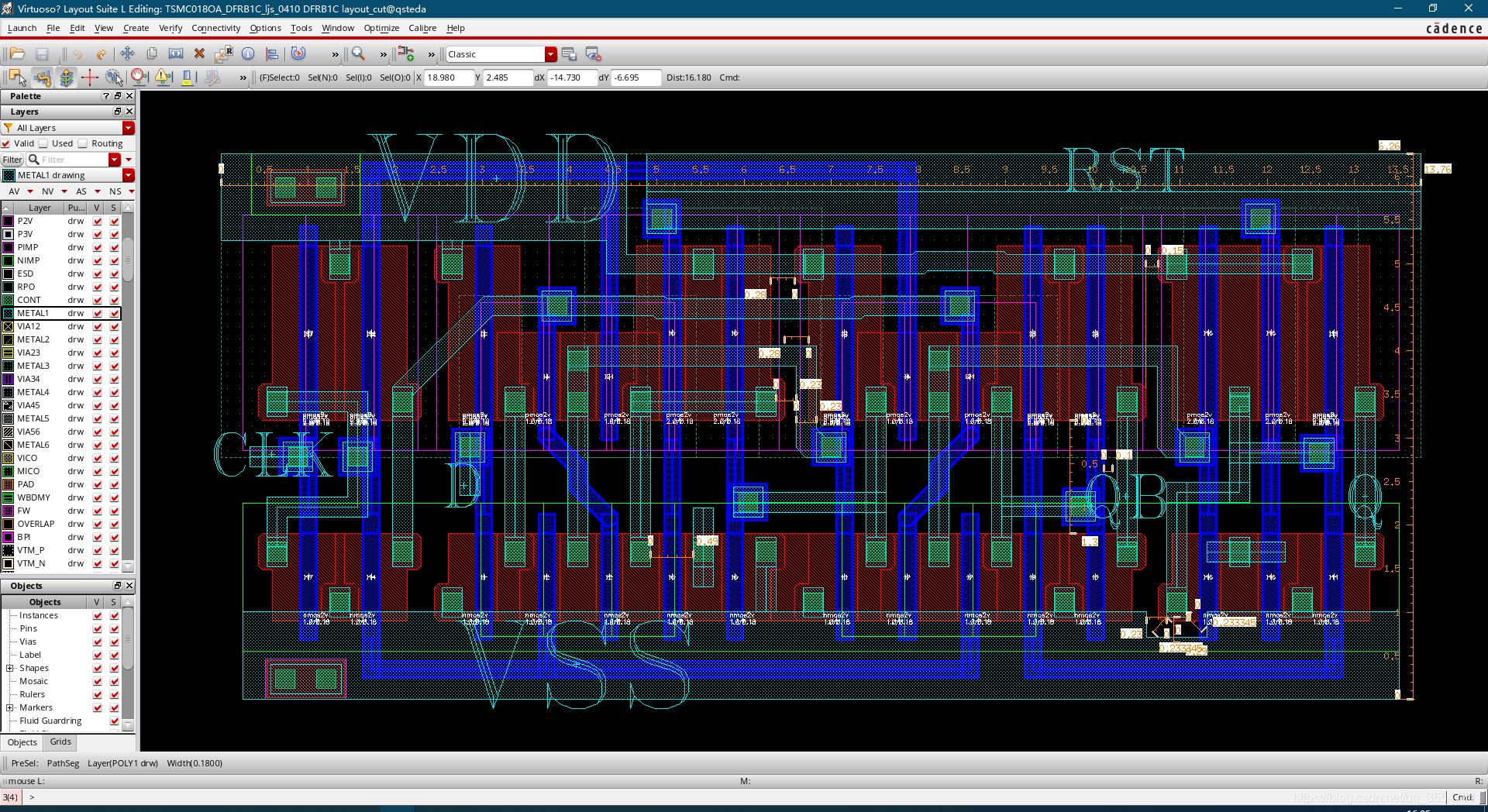

和绘制原理图相似,先是绘制几个子模块电路,再经由拼装组合,形成最终的顶层视图。

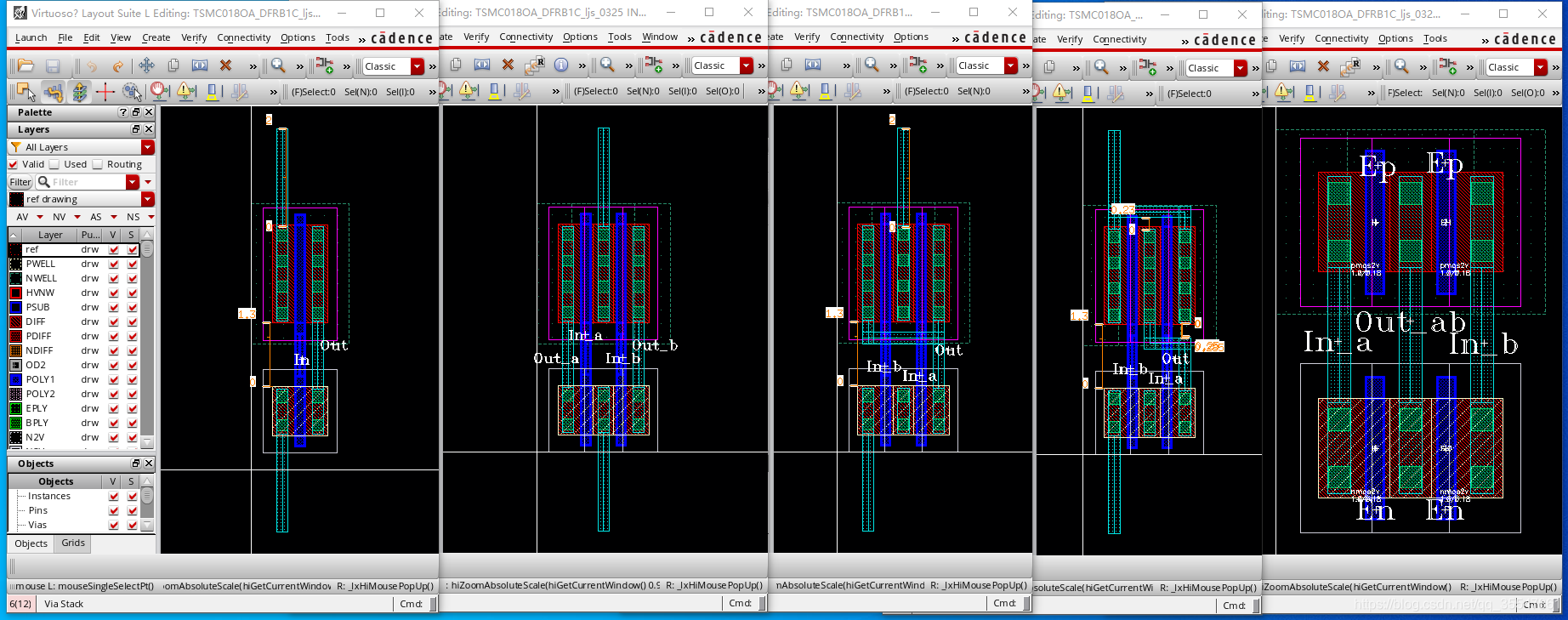

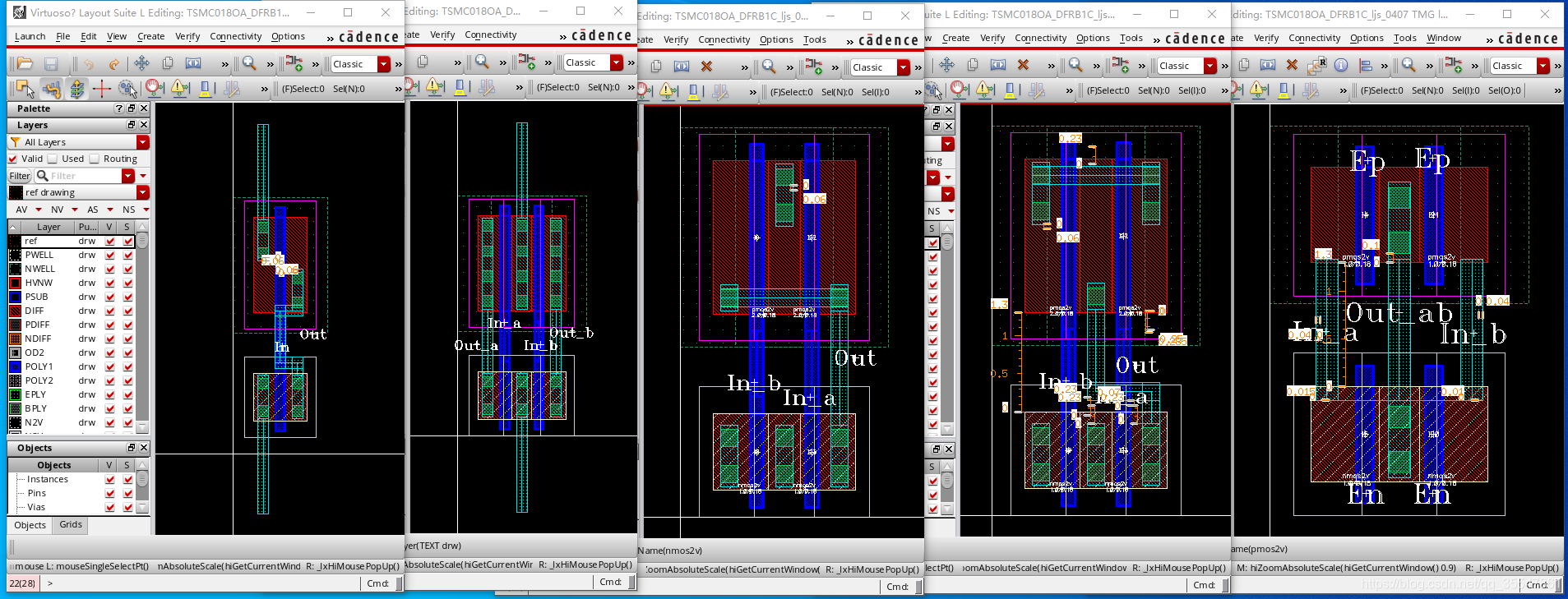

下图分别是单个反相器的版图、两个反相器有源区共用的版图、与非门的第一种版图、与非门的第二种版图以及两个传输门有源区共用的版图。

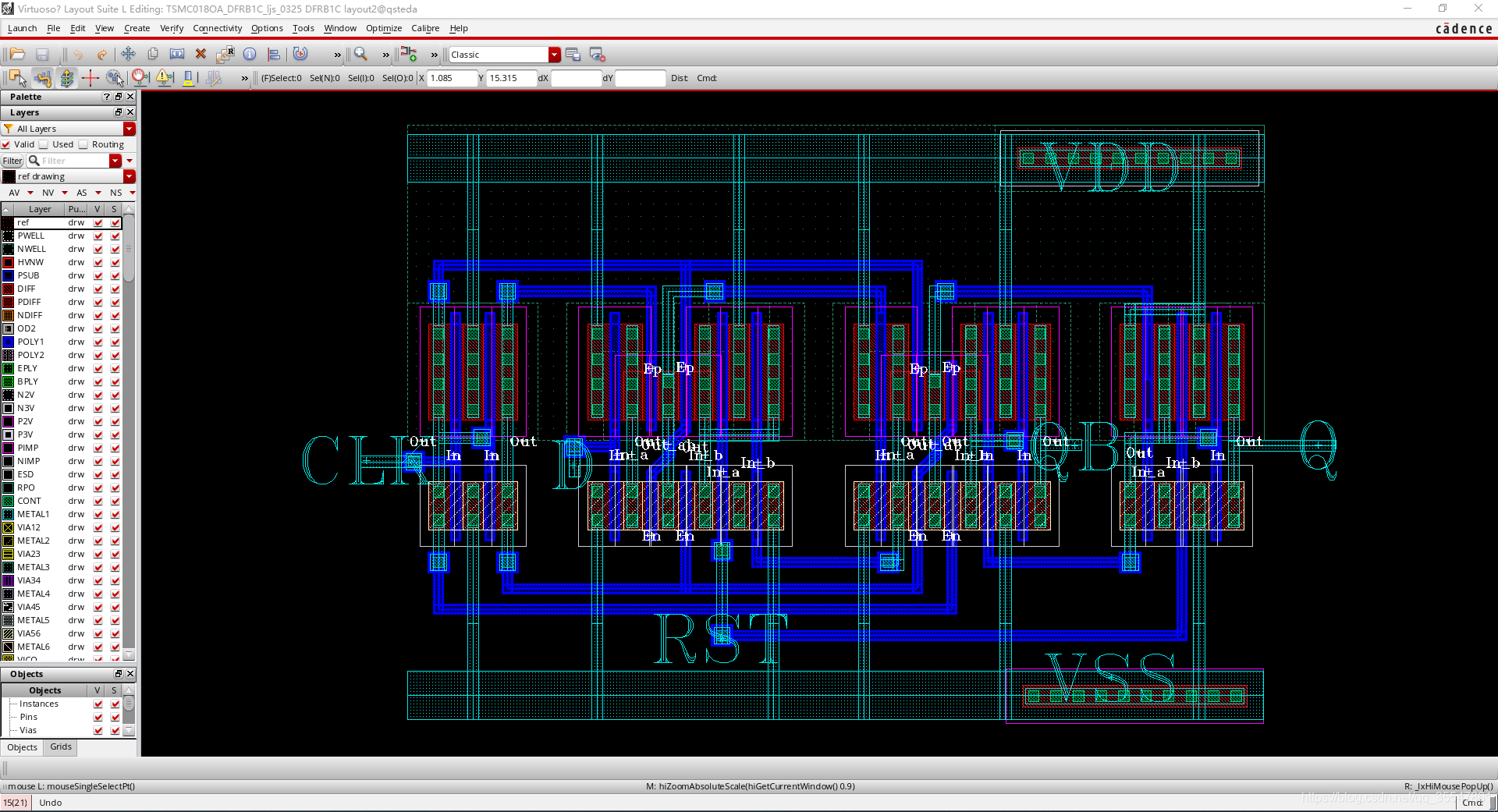

第一版的顶层layout。画完时还是略有成就感,并觉得画的还蛮不错。(DRC,LVS均通过)

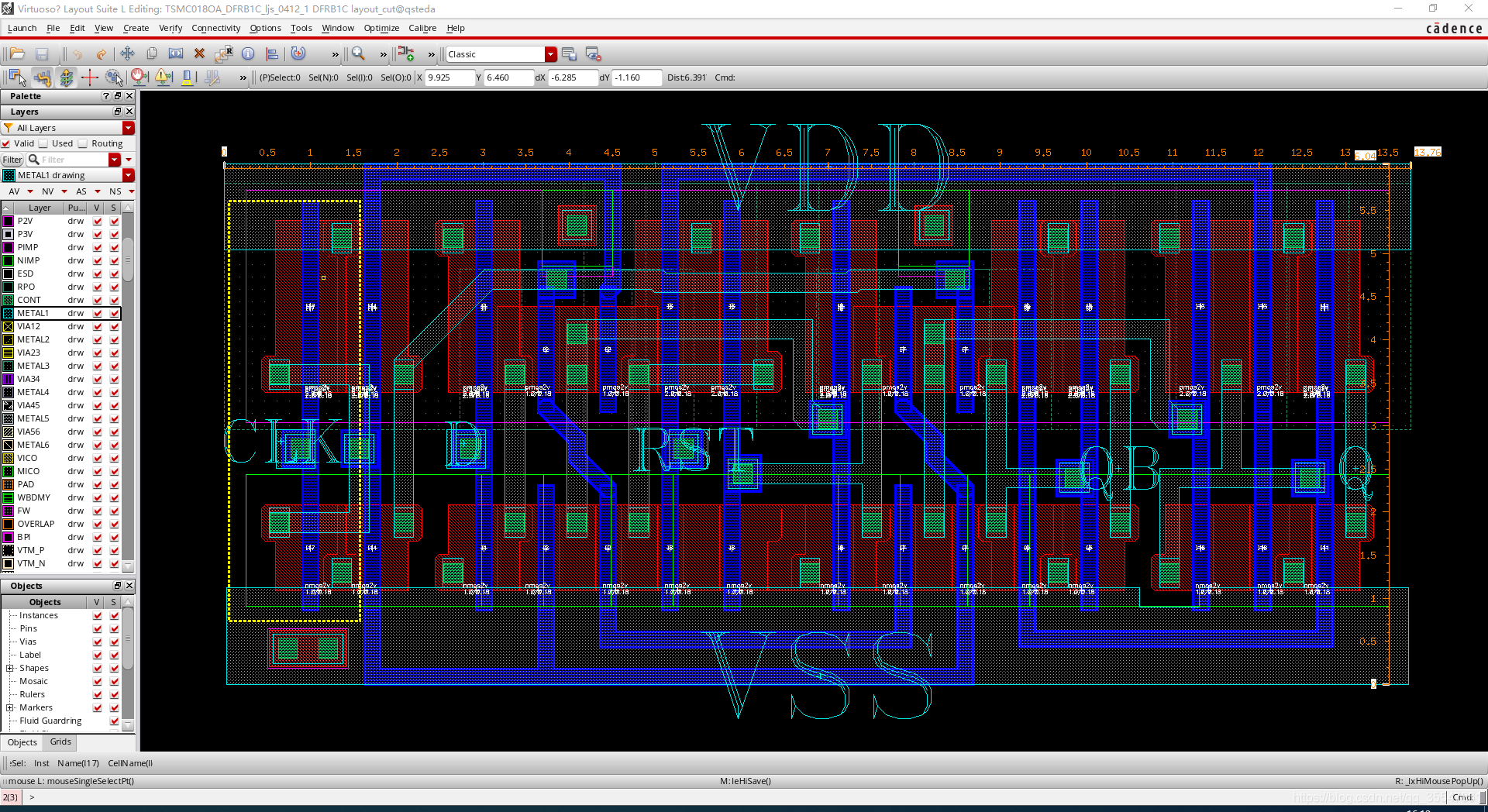

在之后,老师说可以删掉几个有源区的contact,便再经由了打散、删孔,优化走线,开始了第二版的绘制。

与上面相似,分别是单个反相器的版图、两个反相器有源区共用的版图、与非门的第一种版图、与非门的第二种版图以及两个传输门有源区共用的版图。不过基本都是删过孔的。(有点丑)

第二版的顶层layout。画到最后终于忍不住了,太丑了。(DRC,LVS均通过)

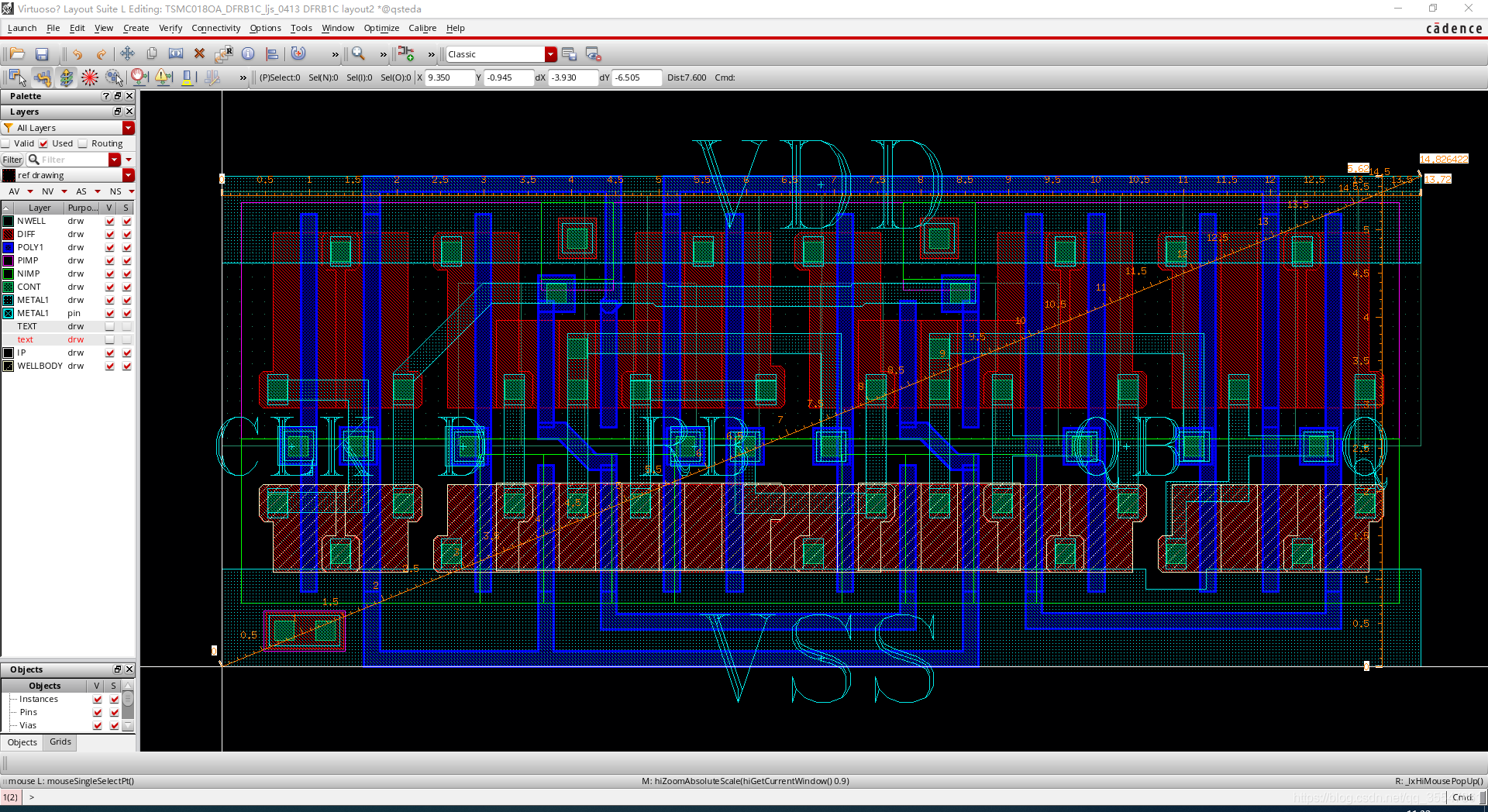

无法忍受的情况下,再经由老师提示,可以将有源区切割,又开始了第三版的绘制。

与上面还是差不多,只不过将两个反相器有源区共用的版图去掉了,然后剩下的分别是单个反相器的版图、与非门的第一种版图、与非门的第二种版图以及两个传输门有源区共用的版图。基本都是删过contact并切割过有源区的。

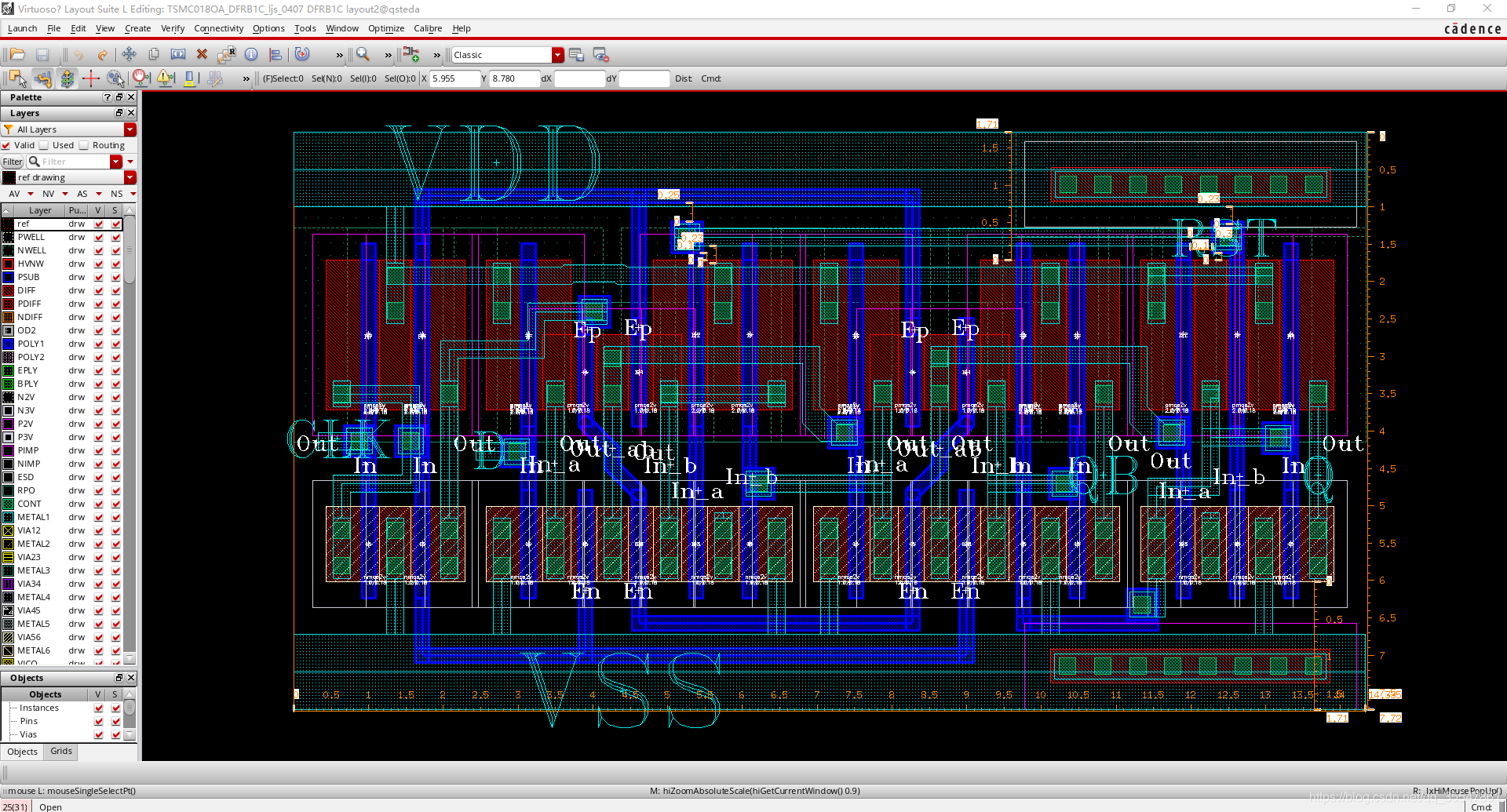

第三版也是最后一版的顶层layout。不可能再改了,太累人了。(DRC,LVS均通过)

最终还是改了一版,第四版了,让VSS和VDD有了充分的金属面积并进一步压缩了整体面积。

唔,又改了,小改动,将PMOS与NMOS的距离缩减了一下,主要得看N阱到P+OD以及N+OD的距离。

唔,在保证上版布局不改动的基础上,将走线的直角弯尽量走的圆润。(最最最后一版)

(还是蛮漂亮的)

走到最后,无论是走线还是布局,还是蛮紧凑的,虽然不知道会不会产生什么乱七八糟的效应,这些留给以后再说吧,这次的也是第一次的实训项目也算是马马虎虎的完成了,不管怎样,通过这次项目也算是是锻炼并熟悉了一下对virtuoso的使用。

3. 总结

体会也是蛮多的吧,虽然重复性劳动较多,不断在drc、lvs,对design rule文档从最开始的全靠有道翻译,到最后能靠自己猜出部分意思,也算是种进步吧。从原理图的绘制、symbol的生成、layout的绘制到netlist以及GDS文件的导出、drc以及lvs验证的设置,也都算是走过了一遍,不像是之前啥也不懂的状态。

本文记录了一个基于IC617平台的D触发器项目过程,包括原理图与版图绘制等步骤,通过多次迭代优化版图设计,最终完成了一个紧凑且符合规范的设计。

本文记录了一个基于IC617平台的D触发器项目过程,包括原理图与版图绘制等步骤,通过多次迭代优化版图设计,最终完成了一个紧凑且符合规范的设计。

7022

7022

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?