前言:

软件环境:VCS2018、Verdi2018、Ubuntu2022

实验步骤:

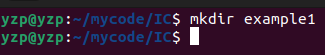

1)建立一个文件夹,mkdir example1

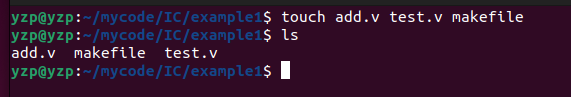

2)在文件夹example1建立三个文件,touch add.v test.v makefile

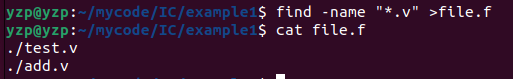

3)生成用于存放verilog文件地址的.f文件,find -name “*.v” >file.f

4)编写add.v test.v makefile这三个文件的代码

add.v

module add (

input [20:0] A ,

input signed [17:0] B ,

output signed [22:0] C);

wire signed [21:0] A_signed;

assign A_signed = {1'b0,A};

assign C = A_signed + B;

endmodule

test.v

`timescale 1ns/1ns

module test;

reg clk;

reg rst_n;

reg [20:0] A;

reg signed [17:0] B;

wire signed [22:0] C;

initial begin

clk = 0;

rst_n = 0;

A = 21'b0;

B = 18'b0;

#10;

rst_n = 1;

repeat(80) @(posedge clk) begin

A = A + 21'b1;

B = B + 18'd2;

end

#2000;

$finish;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("./rtl.fsdb");

$fsdbDumpvars("+all");

end

add add_inst(

.A(A),

.B(B),

.C(C));

endmodule

makefile

VCS = vcs -full64 -sverilog -timescale=1ns/1ns \

+v2k \

-debug_access+all -kdb -lca\

-f file.f

comp:

$(VCS)

verdi:

verdi -ssf rtl.fsdb

clean:

rm -rf csrc simv* *.lib *.lib++ nLint*

rm -rf *.log *.vpd *.fsdb* *.key *log rtl.fsdb*

rm -rf DVEfiles novas.* verdiLog

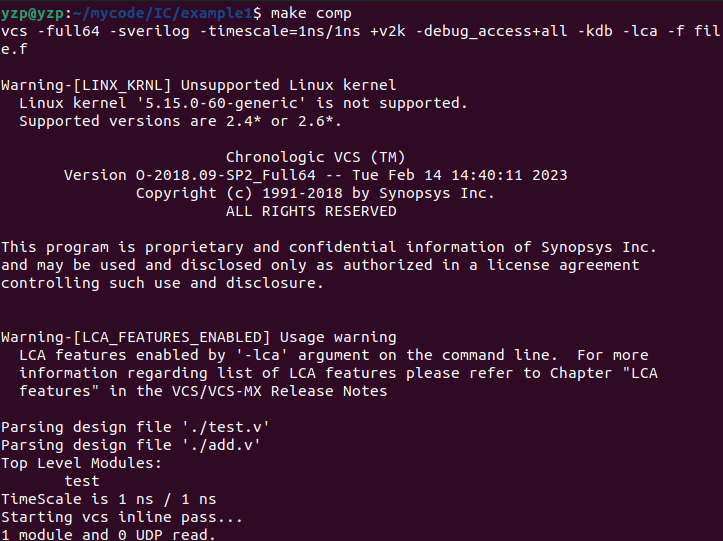

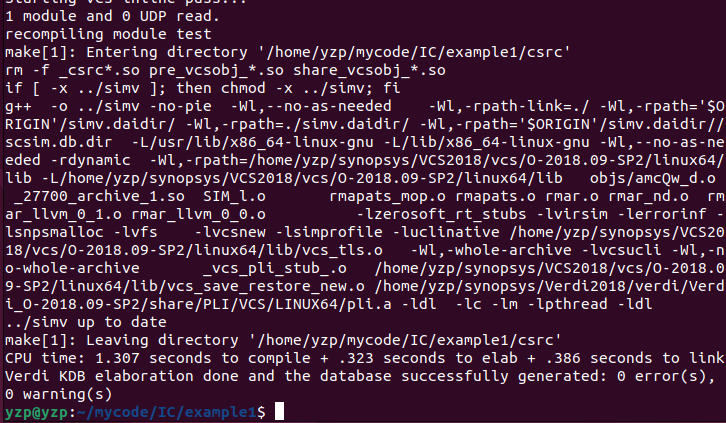

5)用VCS进行编译,make comp

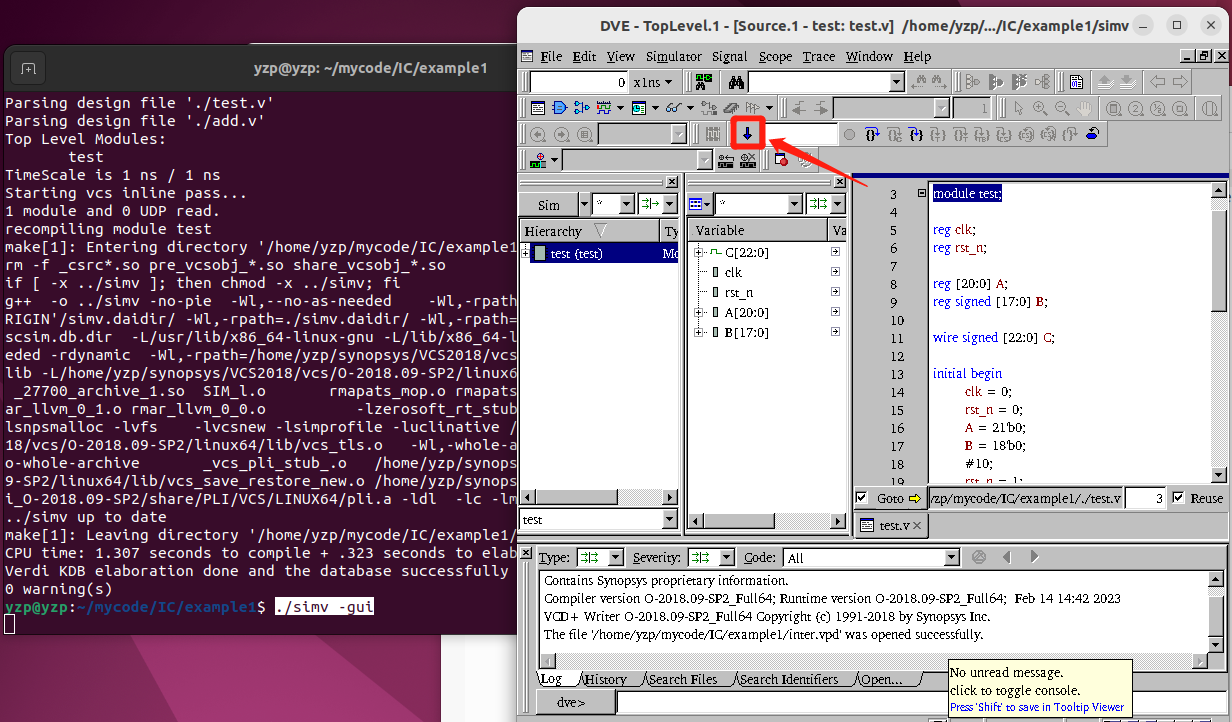

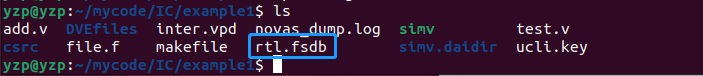

6)打开DVE,./simv -gui;然后点击DVE中的Start按钮(下图红框),便会生成Verdi仿真所需的.fsdb文件

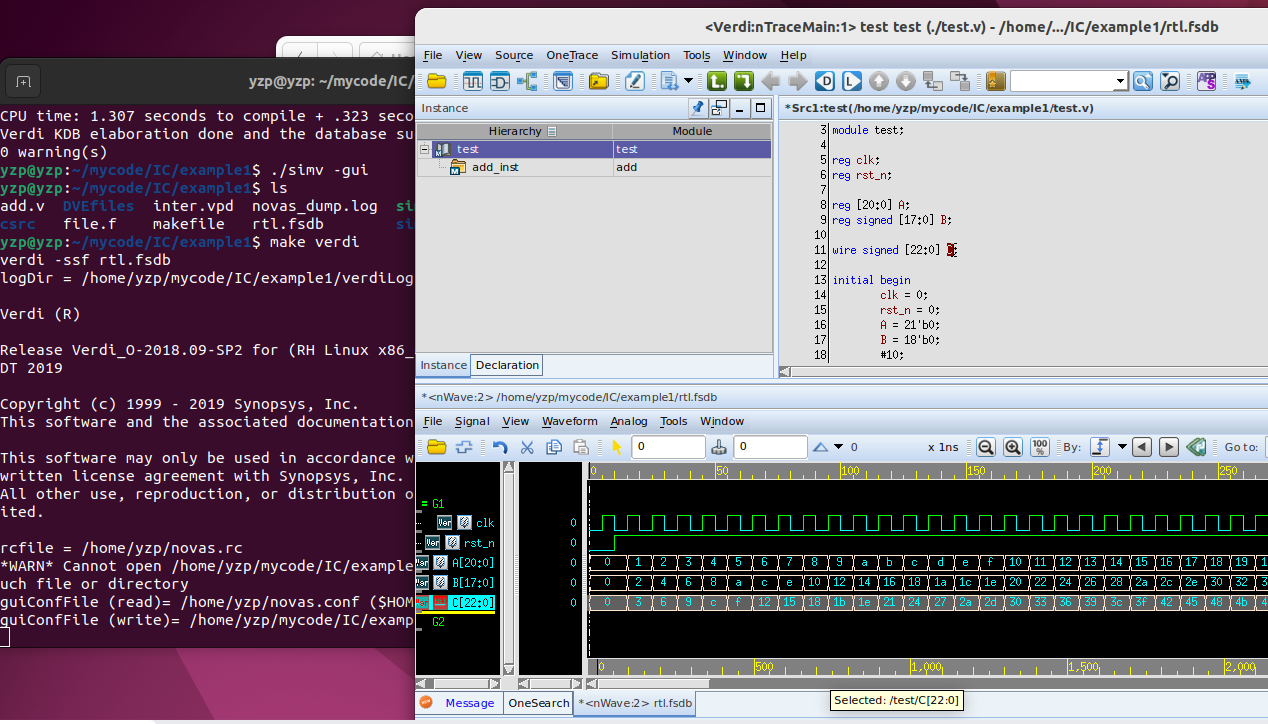

7)最后运行verdi软件,make verdi;verdi打开后,单击test.v文件中的信号,按ctrl+w,即可将信号加入波形图。

备注:

控制VCS和Verdi的命令都写在makefile文件里了,自行分析。另外在testbench文件里要加入生成.fsdb文件的代码,不然DVE软件无法正确生成.fsdb文件。

initial begin

$fsdbDumpfile("./rtl.fsdb");

$fsdbDumpvars("+all");

end

2514

2514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?