arXiv Paper CXL论文阅读笔记整理

问题

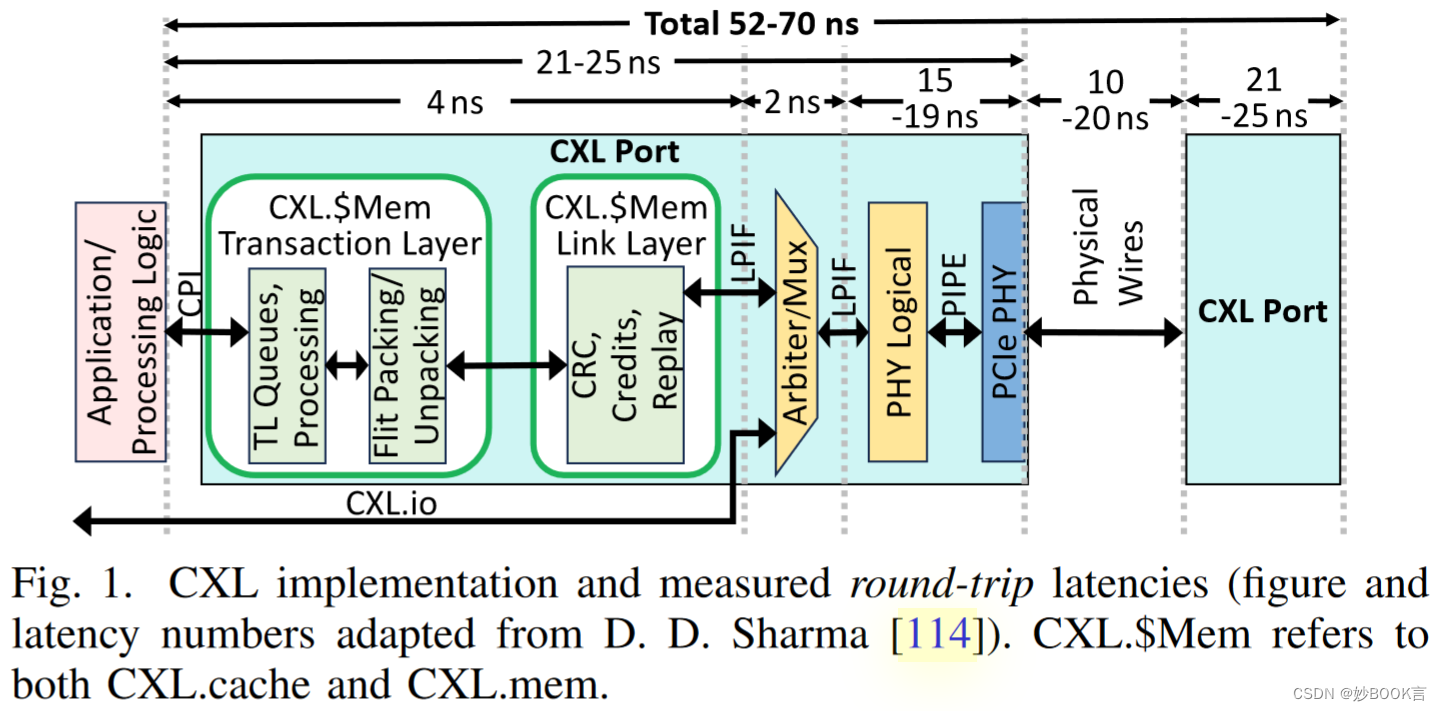

为了克服大规模AI和大数据应用程序的内存容量墙,Compute Express Link(CXL)实现了处理器本地DRAM之外的经济高效的内存扩展。

虽然CXL.mem协议通过优化的协议栈提供了最小的延迟开销,但频繁的CXL内存访问可能会导致内存绑定应用程序的速度显著减慢,无论这些应用程序是对延迟敏感的还是带宽密集型的。CXL控制器中的近数据处理(NDP)有望克服这些限制,但现有方法存在一些挑战:

-

先前关于CXL内存中NDP的工作提出了特定于应用程序的单元,这些单元不适合实际的基于CXL内存的系统,因为这些系统需要支持各种应用程序。

-

现有的CPU或GPU内核对NDP来说并不划算,因为它们没有针对内存绑定应用程序进行优化。

-

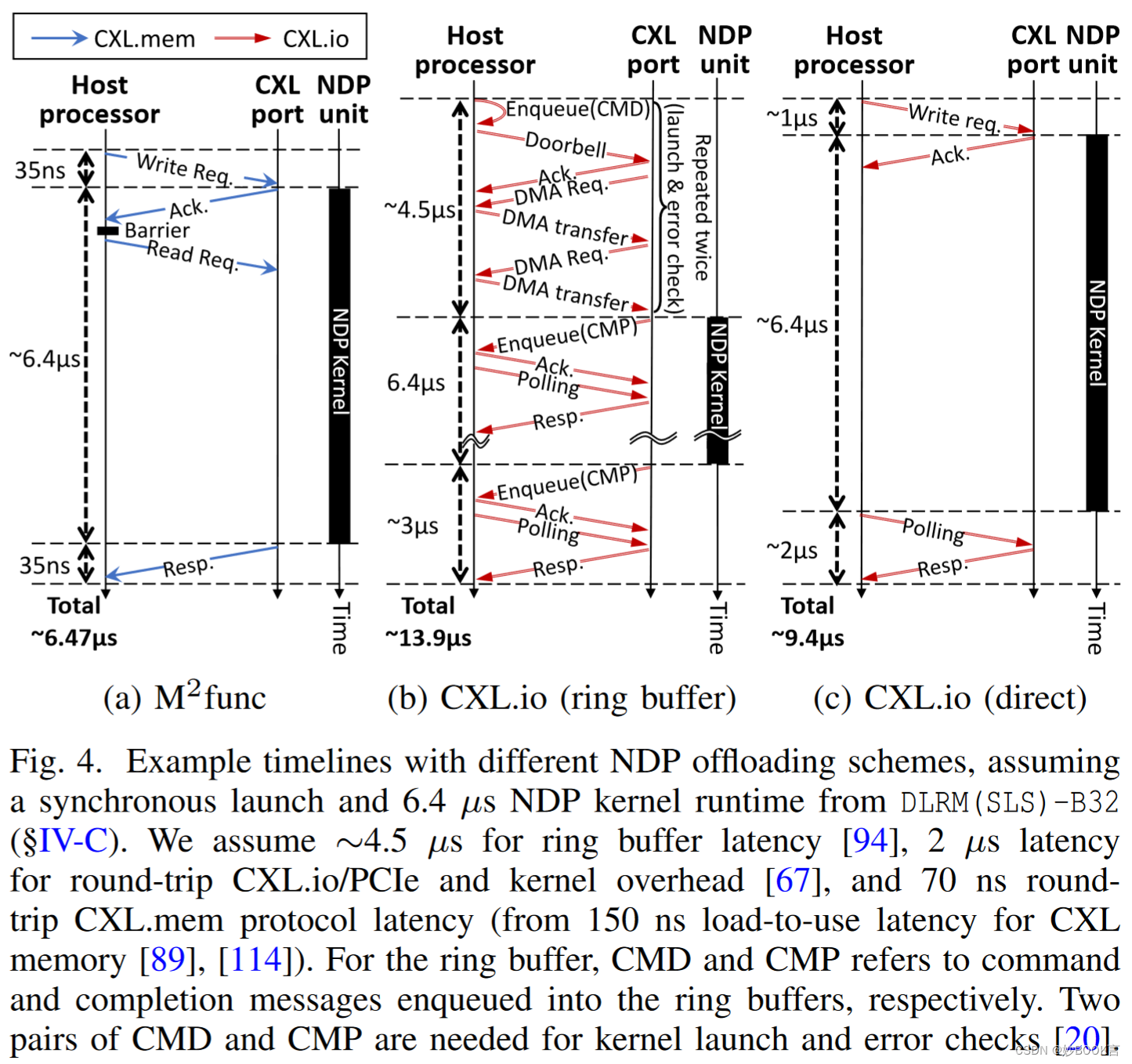

主机处理器和CXL控制器之间用于NDP卸载的通信应实现低延迟,但CXL.io(或PCIe)协议会产生μs级延迟,不适合细粒度NDP。

本文方法

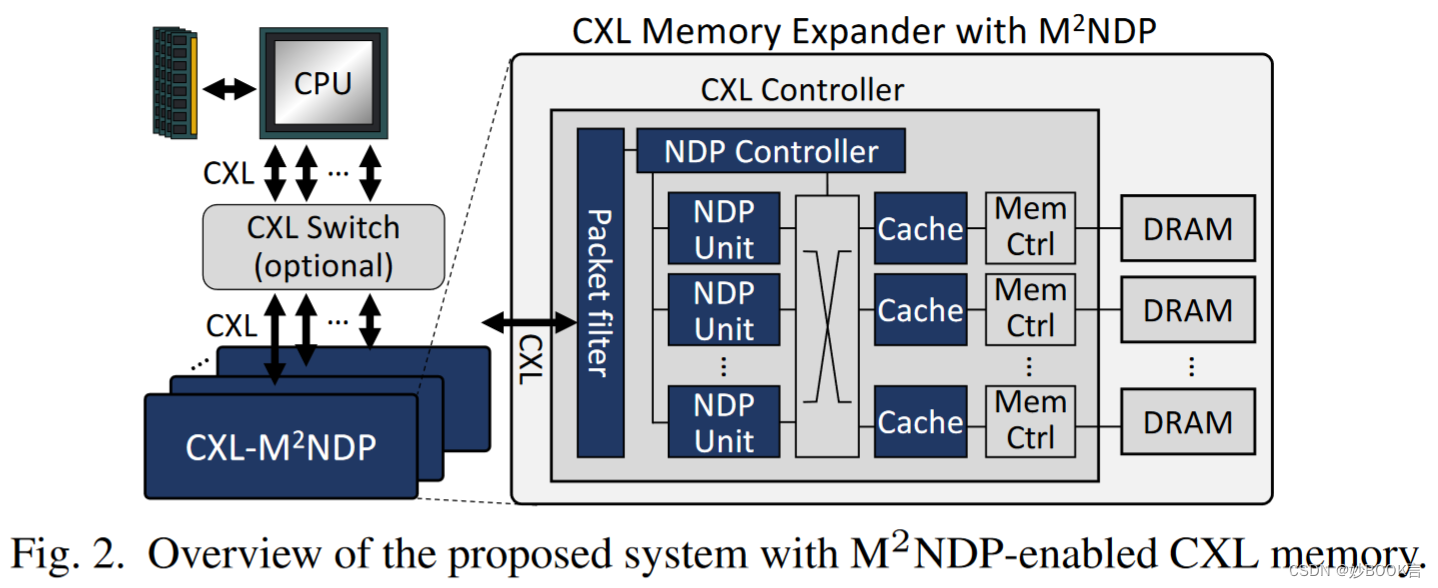

本文提出了一种低开销的CXL存储器通用NDP架构,称为内存映射NDP(M2NDP),包括内存映射函数(M2func)和内存映射μ线程(M2μthr)。为各种应用程序实现了显著的加速,包括内存OLAP、键值存储、大型语言模型、推荐模型和图形分析。

-

M2func是CXL内存中,主机处理器和NDP控制器之间的低开销通信机制。

-

选择性地调整CXL.mem中定义的读写数据包的用途,以便在内存事务之外进行高效的主机设备通信。在CXL.mem请求中将NDP管理命令(即函数调用)封装到预先确定的地址,避免使用CXL.io/PCIe进行传统卸载的高延迟开销。

-

位于CXL存储器输入端口的数据包过滤器,检查传入请求的内存地址是否与为每个主机进程预先分配的专用内存范围相匹配。对于匹配的请求,根据地址触发不同的NDP管理功能。因此,NDP管理函数调用(例如,内核注册、启动和状态轮询)可以简单地通过从主机发出内存访问来完成,从而最大限度地减少了NDP卸载的延迟,有利于细粒度NDP。

-

为了与主机CPU实现最佳兼容性,不需要对CXL.mem标准进行任何修改。M2func通过提供函数调用抽象,避免了在主机和CXL/PCIe连接的设备之间管理基于环形缓冲区的共享任务队列的复杂性。

-

-

M2μthr使用轻量级μ线程,以最小的资源浪费支持NDP内核的高度并发执行,实现了低成本、通用的NDP单元设计。

-

内存绑定工作负载往往比计算机绑定工作负载使用更少的寄存器。因此使用μ线程,是一个轻量级线程,使用体系结构的寄存器子集作为执行单元。通过减少寄存器使用,NDP单元可以同时执行许多μ线程以隐藏DRAM访问延迟,而不会产生过多的物理寄存器成本。

-

内存绑定数据并行工作负载,通常将每个线程与要处理的特定数据相关联。例如CUDA中,线程和存储器位置之间的关联是通过代码间接表示的(例如,使用CUDA中的线程块ID、块维度和线程ID来计算线程的数组元素的索引)。在M2μthr中,每个μ线程与特定内存位置直接关联,即μ线程是内存映射的,可以避免初始地址计算代码。

-

-

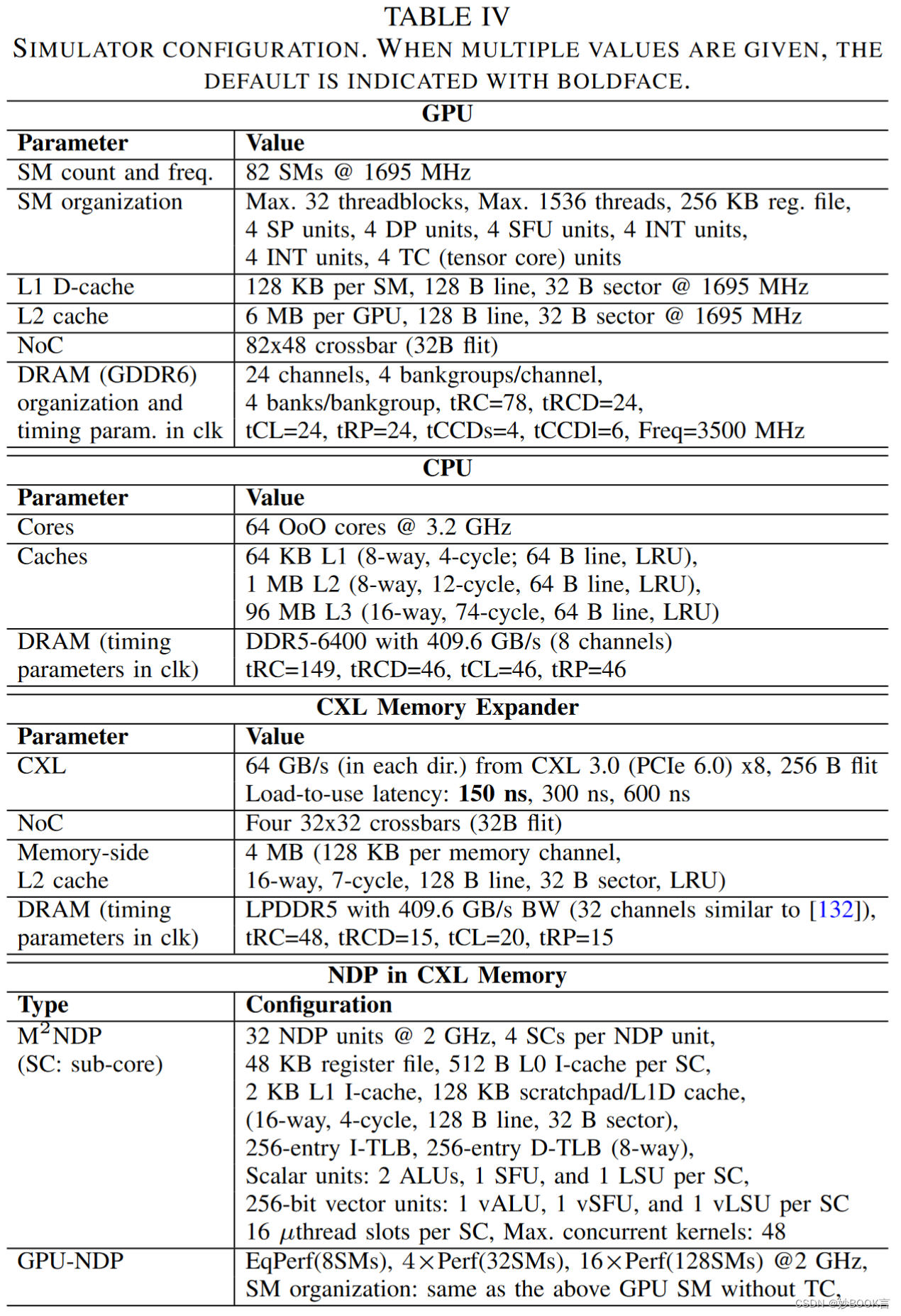

NDP单元的体系结构基于具有矢量扩展[6]的RISC-V ISA,以利用SIMD单元,并在CXL内存中充分利用DRAM BW,同时支持标量运算,避免在仅SIMT的GPU中进行冗余地址计算[56]。内存映射的μ线程使用细粒度多线程(FGMT)来执行,以隐藏内存访问延迟。μ线程是单独生成的,与GPU中的线程块生成形成对比,后者可能会由于包间分歧而浪费资源。

实验表明,与CXL内存的基线CPU或GPU主机相比,加速幅度高达128倍(整体11.5倍),能耗降低高达87.9%(整体80.1%)。

实验

实验环境:使用基于Ramulator[81]的内部循环级模拟器对CXL-M2NDP的功能和时序方面进行了建模。使用改进的ZSim[111]和AccelSim[77]对具有CXL存储器的基线CPU和GPU进行建模。表IV给出了模拟器配置。

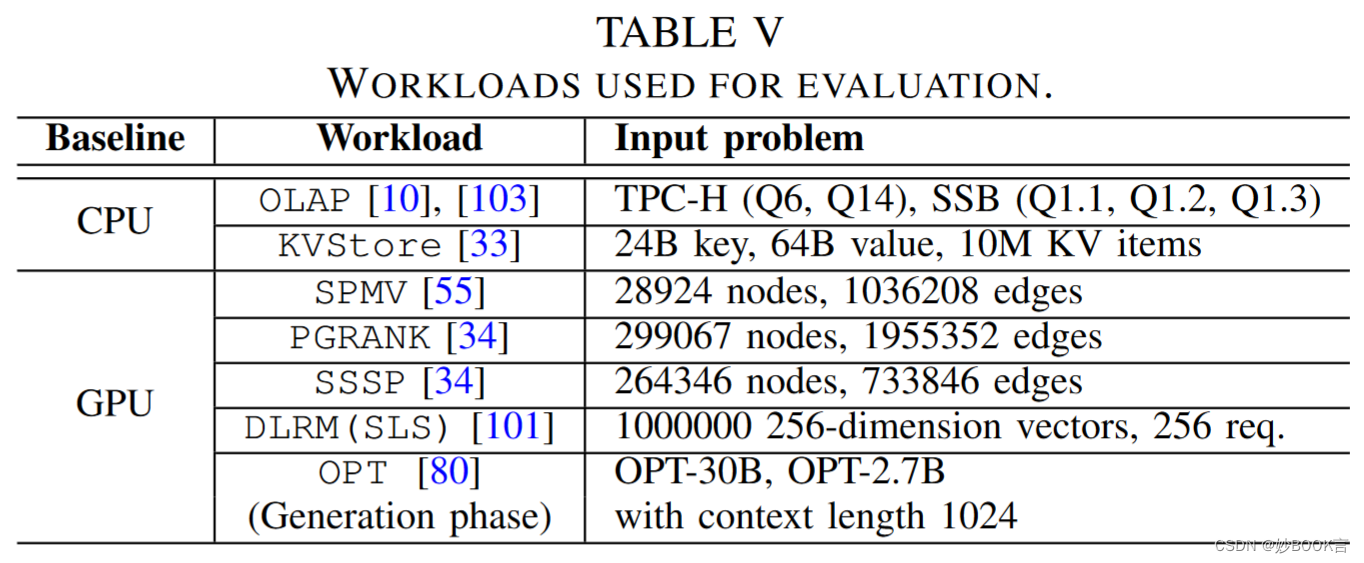

数据集:

实验对比:运行时间、尾延迟、加速比、能量消耗

实验参数:不同数据集

总结

针对CXL内存的近数据方法,如何实现不使用特殊单元,同时保持低延迟。本文提出了低开销的CXL存储器通用NDP架构,称为M2NDP,包括内存映射函数(M2func)和内存映射μ线程(M2μthr)。(1)M2func是主机处理器和NDP控制器之间的低开销通信机制。利用CXL.mem进行主机设备通信,将NDP管理命令封装到预先确定的地址,避免使用CXL.io/PCIe的高延迟开销。在CXL输入端口增加数据包过滤器,若请求的内存地址与预先分配的内存范围相匹配则触发NDP管理功能。(2)M2μthr使用轻量级μ线程,使用体系结构的寄存器子集作为执行单元,NDP单元使用细粒度多线程执行多个μ线程以隐藏DRAM访问延迟。每个μ线程与特定内存位置直接关联,即μ线程是内存映射的,可以避免初始地址计算代码。(3)NDP单元基于RISC-V ISA,以利用SIMD单元,并利用DRAM BW,同时支持标量运算。

2841

2841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?