FPGA中常见的复位方式为异步复位和同步复位。

异步复位与同步复位各有优缺点,同步复位需要多消耗资源,但异步复位亚稳态出现的概率更高。

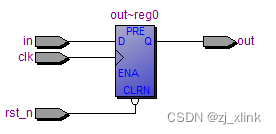

1) 异步复位

always @(posedge clk or negedge rst_n) begin

if(!rst_n) out <= 1'b0;

else out <= in;

end

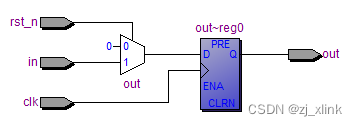

2) 同步复位

always @(posedge clk) begin

if(!rst_n) out <= 1'b0;

else out <= in;

end

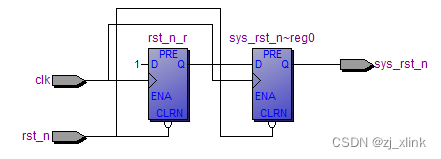

3) 异步复位、同步释放

在复位信号释放时,如果刚好在寄存器的建立时间与保持时间之间,此时由于释放信号不稳定,会引起亚稳态问题,可使用两级寄存器进行双缓冲。

always @(posedge clk or negedge rst_n) begin

if(!rst_n) rst_n_r <= 1'b0;

else rst_n_r <= 1'b1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) sys_rst_n <= 1'b0;

else sys_rst_n <= rst_n_r;

end

1306

1306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?