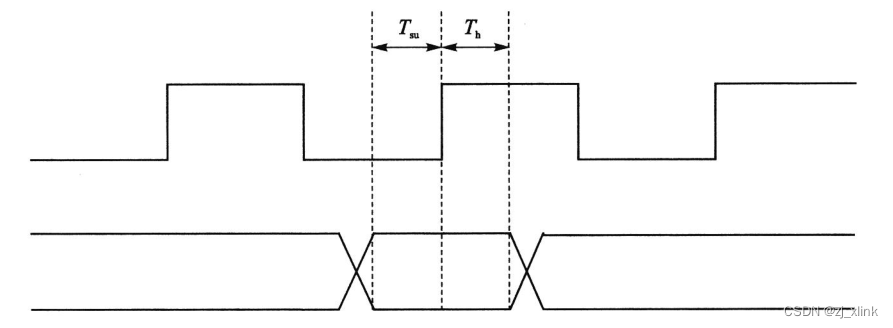

1、建立时间与保持时间

建立时间(Tsu):在时钟上升沿到来前数据必须提前保持稳定的时间。

保持时间(Th):在时钟上升沿到来之后数据必须保持稳定的时间。

在建立时间和保持时间范围内数据必须稳定,不然很可能出现亚稳态问题,影响系统稳定。

路径延时过长可能造成建立时间违规,过短可能造成保持时间违规。

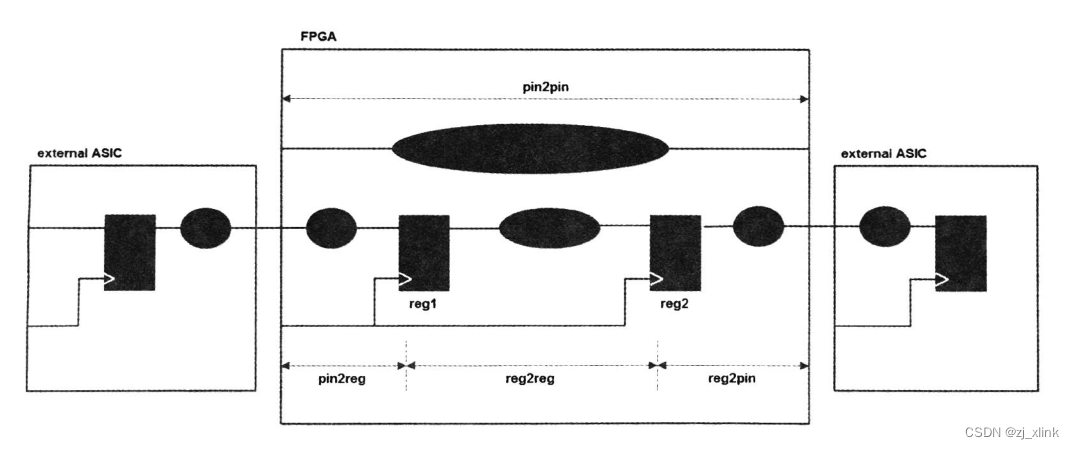

2、基本时序路径

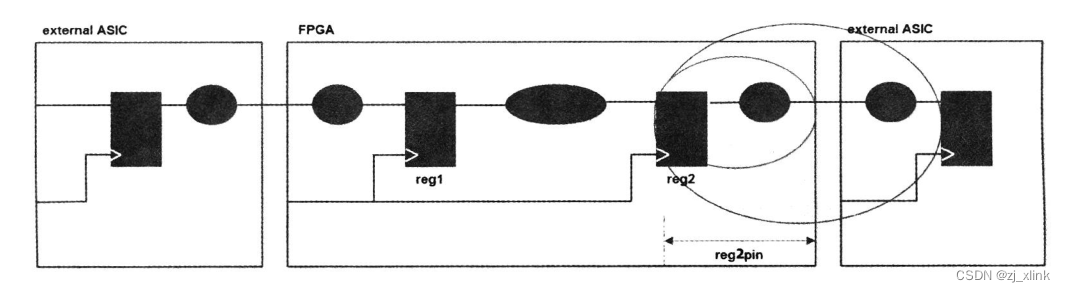

FPGA通常有4大类基本时序路径:内部寄存器之间的时序路径(reg2reg)、输入引脚到内部寄存器的时序路径(pin2reg)、内部寄存器到输出引脚的时序路径(reg2pin)、输入引脚到输出引脚(不通过寄存器)的时序路径(pin2pin)

1)内部寄存器之间的时序路径(reg2reg)

需要告诉EDA工具该路径的时钟频率。

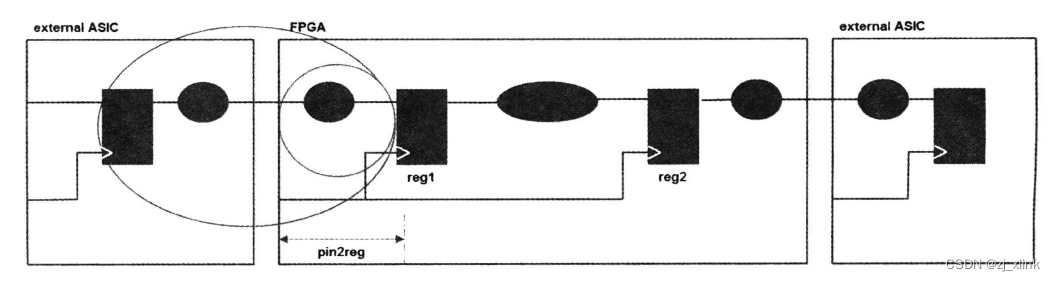

2) 输入引脚到内部寄存器的时序路径(pin2reg)

需要告诉EDA工具外部芯片的延时情况 ,从而调整内部电路(小圈部分)。

3) 内部寄存器到输出引脚的时序路径(reg2pin)

需要告诉EDA工具外部芯片的延时情况 ,从而调整内部电路(小圈部分)。

4) 输入引脚到输出引脚(不通过寄存器)的时序路径(pin2pin)

需要告诉EDA工具此部分电路的最大、最小延时要求。

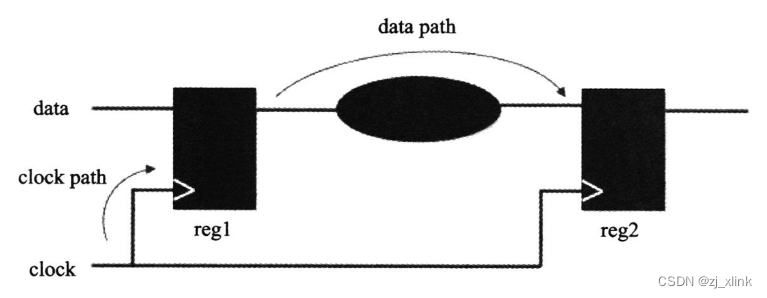

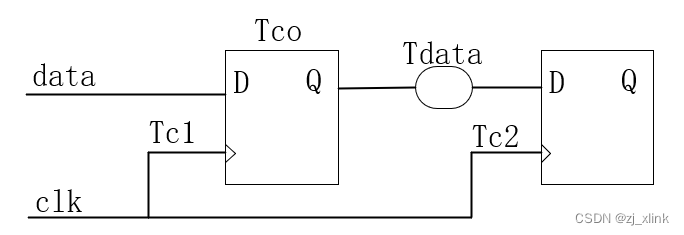

3、内部寄存器之间的时序分析

内部寄存器间的时序分析,上图中:

Tc1表示时钟源到源寄存器的时钟延时。

Tc2表示时钟源到目的寄存器的时钟延时。

Tco表示源寄存器内部的延时。

Tdata表示寄存器间的组合逻辑延时。

Tsu表示目的寄存器的建立时间。

Th表示目的寄存器的保持时间。

对于建立时间:

data arrival time = Launch edge + Tc1 + Tco + Tdata

data required time = Latch edge + Tc2 - Tsu

Setup time slack = data require time - data required time

对于建立时间,目的寄存器Latch edge 比 源寄存器Launch edge晚一个时钟周期。

对于保持时间:

data arrival time = Launch edge + Tc1 + Tco + Tdata

data required time = Latch edge + Tc2 + Th

Hold time slack = data arrival time - data required time

对于保持时间,目的寄存器Latch edge 与 源寄存器Launch edge为同一个时钟周期。

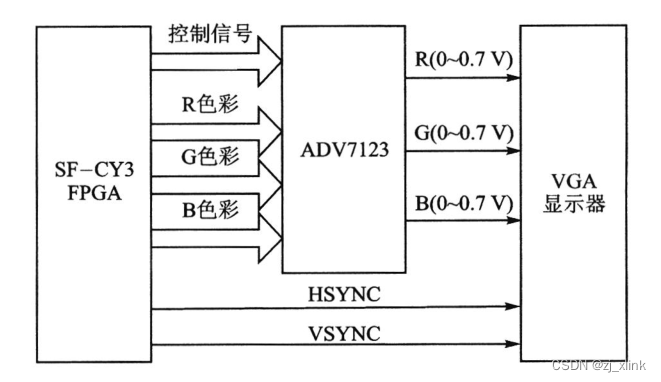

4、内部寄存器到输出引脚的时序分析

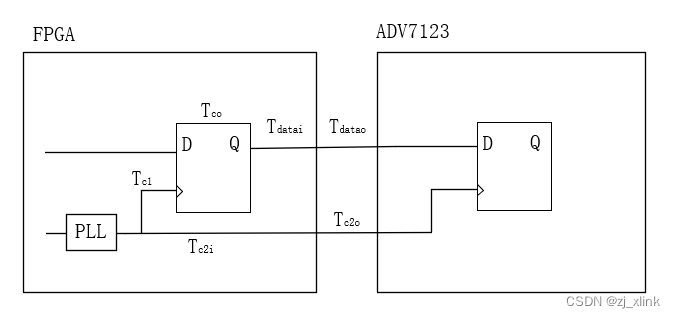

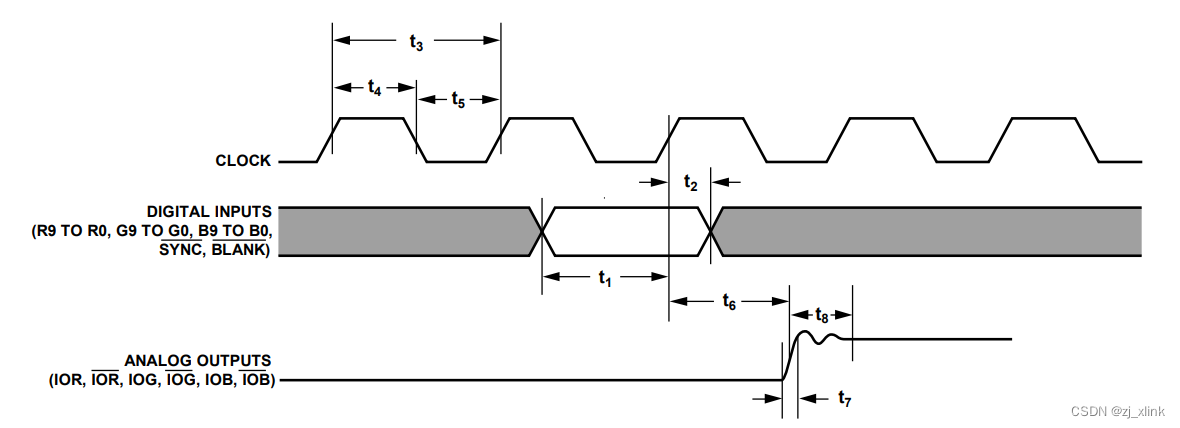

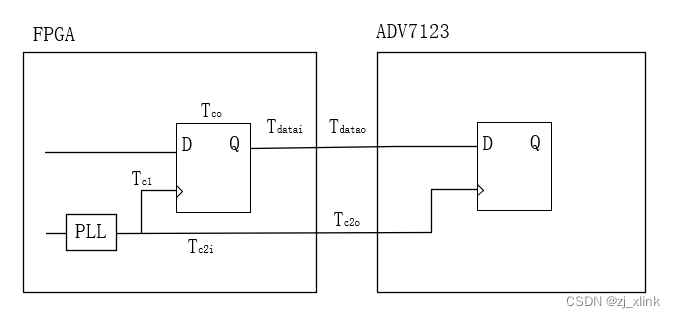

以上图VGA驱动为例,控制信号包括同步时钟信号lcd_clk和转换数据有效指示信号。上图可简化为如下模型

首先查看ADV7123的datasheet

![]()

可知建立时间为0.2ns,保持时间为1.5ns。

对于lcd_clk时钟,其需要通过FPGA输出引脚连接到ADV7123上,其延时主要包括PLL输出到FPGA引脚的延时,以及FPGA引脚到ADV7123引脚的延时(PCB走线延时),需要将其约束为虚拟(virtual)时钟,以作为latch时钟进行时序分析。

对于数据路径,其延时主要包括源寄存器内部延时Tco,源寄存器输出到FPGA引脚的延时,以及FPGA引脚到ADV7123引脚的延时(PCB走线延时)。

对于建立时间,时序关系必须满足:

Launch edge + Tc1 + Tco + Tdatai + Tdatao < Latch edge + Tc2i + Tc2o - Tsu

对于保持时间,时序关系必须满足:

Launch edge + Tc1 + Tco + Tdatai + Tdatao > Latch edge + Tc2i + Tc2o + Th

对于内部延时(Tco, Tc1, Tdatai, Tc2i),FPGA自身知道,但对于外部的延时(Tc Tdatao, Tc2o),FPGA无从得知,需要通过数据约束告诉FPGA,可通过Quartus TimeQuest中的set output delay功能设置该参数

output delay max = max(Tdatao) + Tsu - max(Tc2o)

output delay min = min(Tdatao) - Th - min(Tc2o)

1448

1448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?