PCIE DMA开发一共有4大类:Xilinx官方XAPP1052和XMDA IP、以色列Xillybus多通道DMA IP、国外RIFFA IP、北大EPEE IP)。

要开发一个带PCIe或者PXIe接口的FPGA板卡出来,除了硬件本身外,最重要的就是FPGA芯片里面的PCIe通信代码编写,俗称下位机FPGA编程;还有中间层的驱动文件编写以及上位机PC端的应用程序开发。

Xilinx官方提供的XDMA IP核方案有一个不足的地方,就是PCIe通信时的通道数量有限制,用户无法灵活配置,只能两上两下,无法实现8上8下这种,除非用户自己通过软件编写实现,这样工作量就会无比巨大。另外,Xilinx官方提供的驱动文件没有经过微软数字签名认证,无法正常安装,只能将windows系统设置到测试模式下才行,这点对于普通用户来说,比较麻烦。

以色列XILLYBUS公司推出的Xillybus FPGA PCIe DMA驱动IP核。这家公司技术实力非常全面,在很早的时候,就把复杂的FPGA PCIe DMA通信技术通过自己的封装变成傻瓜化,让用户能够轻轻松松集成到自己的项目和产品应用中。与此同时,该公司还把USB 3.0协议进一步封装成非常易用的FPGA IP核,以及将Xilinx ZYNQ平台里面的AXI4总线重新封装了。除此之外,Xillybus不仅仅支持Xilinx公司带PCIe的全系列FPGA芯片,还支持Altera公司带PCIe的全系列FPGA 芯片。

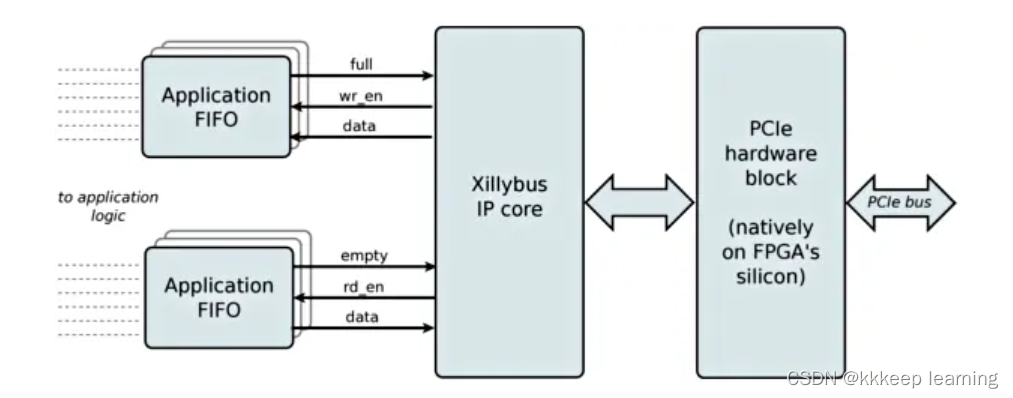

首先,Xillybus将Xilinx或Altera公司的底层PCIe接口IP core,接入到它自己的Xillybus IP core,然后再通过四线握手的Application FIFO接口将收发TX、RX通道映射出来给到FPGA。结构非常清晰,用户即使完全不懂PCIe通信协议,也可以很简单的在FPGA里面通过调用Xillybus提供的收发FIFO接口,将数据发送到上位机PC或者接收上位机PC下发的数据,因为Xillybus直接将底层的IP核全部屏蔽了,用户只需要按照标准的四线握手协议来操作对应的FIFO缓冲区就可以了。而上位机PC端更加简单,只需要通过打开被系统(Windows和Linux都支持)识别出来的名为xillybus的PCIe设备,然后调用标准的文件读写函数,进行文件读写即可控制底层FPGA芯片里面的FIFO数据的收发。

RIFFA(用于FPGA加速器的可重用集成框架),它是用于通过PCIe总线从主机CPU到FPGA相互之间进行数据交互的简单框架。该框架要求具有PCIe的上位机PC或者工控机和带有PCIe接口的FPGA硬件。RIFFA中间层驱动支持Windows和Linux,底层驱动FPGA PCIe IP核支持Xilinx和Altera芯片,上位机应用层支持LabVIEW、C / C ++、Python、Matlab和Java。

软件方面,RIFFA有两个主要功能:数据发送和数据接收。上层提供C / C ++、Python、MATLAB、Java下的DLL链接库。中间层驱动程序在每个系统(Linux和Windows操作系统)下支持识别多个FPGA(最多5个)。

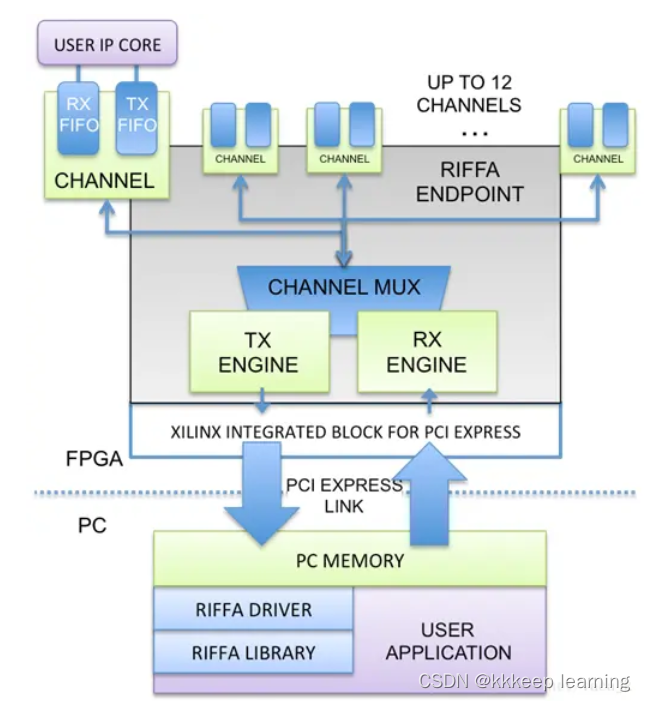

硬件方面,用户访问具有独立发送和接收信号的接口(全双工),无需了解总线地址,缓冲区大小或者PCIe数据包格式。只需在FIFO接口上发送数据并在FIFO接口上接收数据即可。RIFFA不依赖于PCIe桥接器,因此不受桥接器实现的限制。取而代之的是,RIFFA直接与PCIe端点一起使用,RIFFA使用直接内存访问(DMA)传输和中断信号传输数据。这样可以在PCIe链路上实现高带宽。软件和硬件接口都已大大简化。

FPGA底层集成了Xilinx的PCIe core,然后使用TX、RX引擎,经过通道仲裁映射到最多12个TX、RX通道上。结构与PIO、BMD的结构类似,增加了通道扩展的功能,这样用户就不需要自己去写仲裁代码了。

上位机PC端主要就是基本的驱动、应用结构,PCIe的访问空间映射到了PC的内存上;中间层的RIFFA驱动负责内存以及PCIe接口的管理,RIFFA动态链接库可以被用户应用程序调用,从而实现对底层RIFFA驱动的调用,并最终实现PCIe的数据通信。

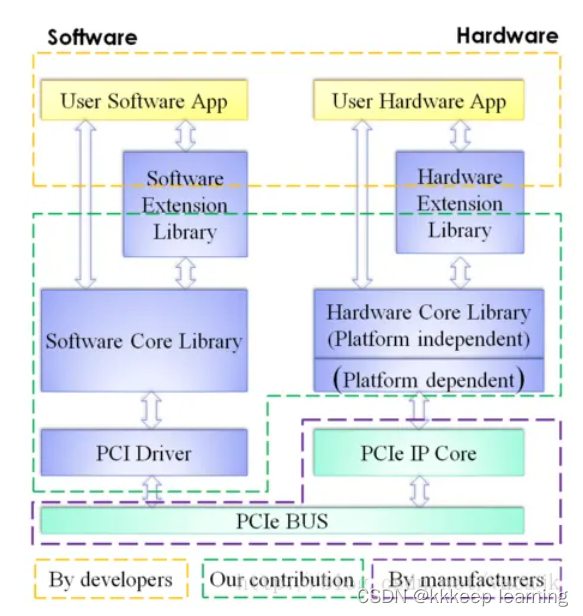

最后一个就是昙花一现的北大开源组织做的EPEE,图7-8是其系统框图,感兴趣的用户可以自行分析,因为目前可以找到这个EPEE的资料和应用非常少,这里就不在介绍了。

选择一个合适的FPGA PCIe驱动IP非常重要,不仅可以节约大量开发时间,关键是稳定性要比我们自己写的更好,毕竟很多商业的FPGA驱动IP核和驱动inf文件都是经过了大量企业实践检验过的,而很多所谓的开源代码,实际上用起来总是有这样那样的bug和坑,需要用户自己花费大量的时间去调试、修改和维护,有时候得不偿失。如果是做产品的话,个人愚见,还是用成熟的企业版软件工具包和FPGA驱动IP核,毕竟稳定胜于一切,社会分工不一样。以上来源于:神电测控 https://www.bilibili.com/read/cv10494381/

这里考虑到后续将接入多个FPGA进行资源池管理,我们选择使用基于开源的Riffa开发PCIE接口驱动。

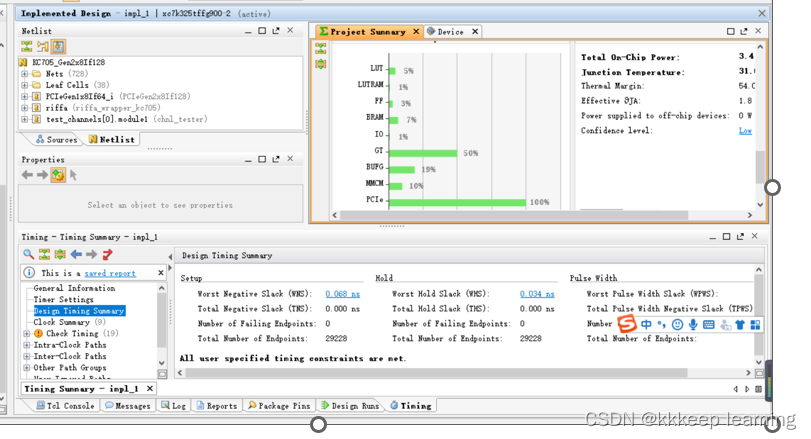

这里使用基于Linxu系统作为我们的host进行开发,板卡是Kintex-7.这里为了方便,直接使用Riffa给的FPGA demo里的板卡型号进行开发。在XXX文件夹下,使用vivado2015.4打开工程在setting中可以看到板卡的型号。为了方便我们进行开发,而较少的对底层IP进行修改和调试,直接使用demo case。

这里需要说明一下,在vivado2019.1中对demo进行综合,总是会遇到问题,编译不能通过。有些是对functions.vh文件中的clog2s方法进行修改,还有将functions.vh文件set global include均不能解决。于是将vivado版本进行降级编译。于是选择了vivado2015.4,编译通过。Riffa这个开源框架也是最近几年没有人在维护了,所以对新版本的vivado编译会有问题。所以有遇到相同问题的小伙伴可以尝试下。

先说一下我们的环境:

linux主机为host,使用c_c++代码进行上位机调试。使用xilinx kintex7芯片为FPGA工程。

接下来,Linux端驱动安装。

#download

$:git clone https://github.com/KastnerRG/riffa

$:cd driver/linux

#install kernel header

$:sudo make setup

#compile and install

$:make

$:sudo make install

$:sudo ldconfig

$:sudo modprobe riffa

#check

$:lsmod | grep riffaFPGA工程编译综合,bit流下载。

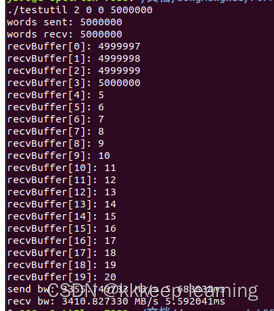

调试:

done.

2938

2938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?