在DDR3中几乎所有的状态都要求时钟必须处于稳定状态,只有在两个条件下,输入时钟可以进行切换,

- Self-Refresh mode

- Precharge Power-Down mode

Refresh&Self-Refresh

时延参数

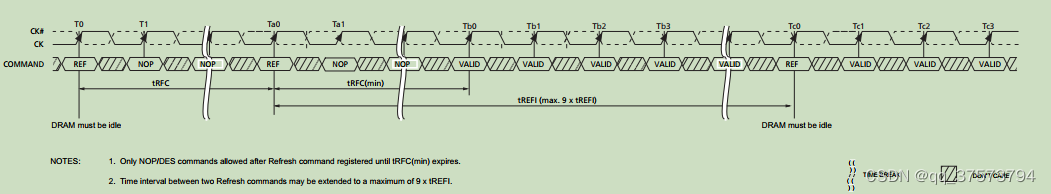

Refresh

- DDR为维持自身的数据,每隔固定时间必须要进行一次Refresh操作。

- 进行Refresh之前需要进行Precharge操作后处于Idle状态,并要满足tRP的最小时延要求。

- Refresh结束之后,所有bank也是处于Idle状态。

- 进行Refresh与下一次有效命令(除去NOP / DES)之间,需要满足最小时间tRFC。

- 考虑到命令的调度性能,Refresh命令的间隔可以灵活调整,最大不能超过 9 x tREFI。

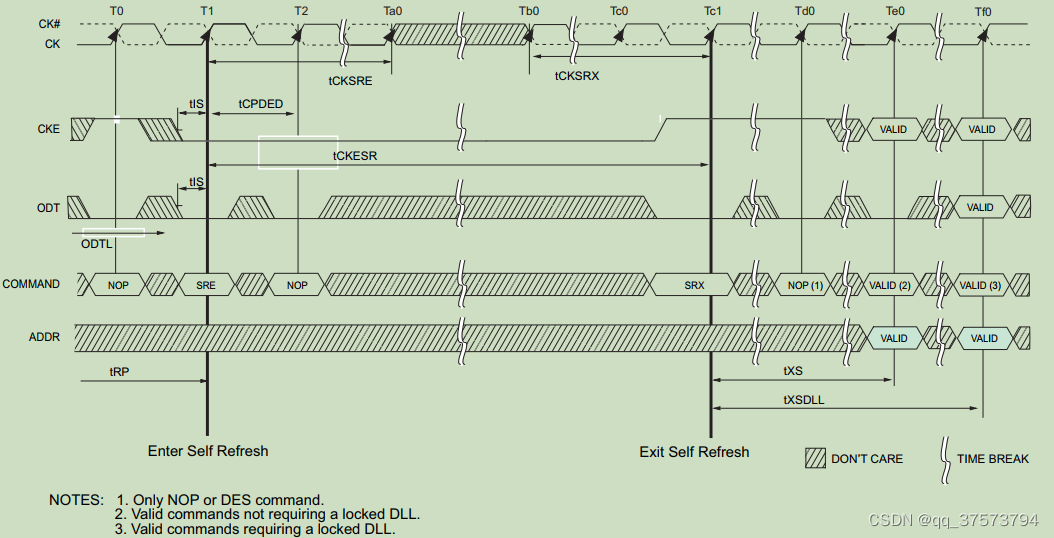

Self-Refresh

- 处于Self-Refresh状态,DDR在系统power-down的状态下,不需要时钟仍能保持数据;

- 进入Self-Refresh状态前需要进行Precharge操作后处于Idle状态,并满足tRP最小时延要求;

- 进入Self-Refresh状态前,ODT功能需要关闭,ODT需要提前(ODTL+0.5tCK)拉低;

- 对于DLL ON的配置下,进入Self-Refresh状态会自动降DLL disable,退出时自动进行enable;

Power Down

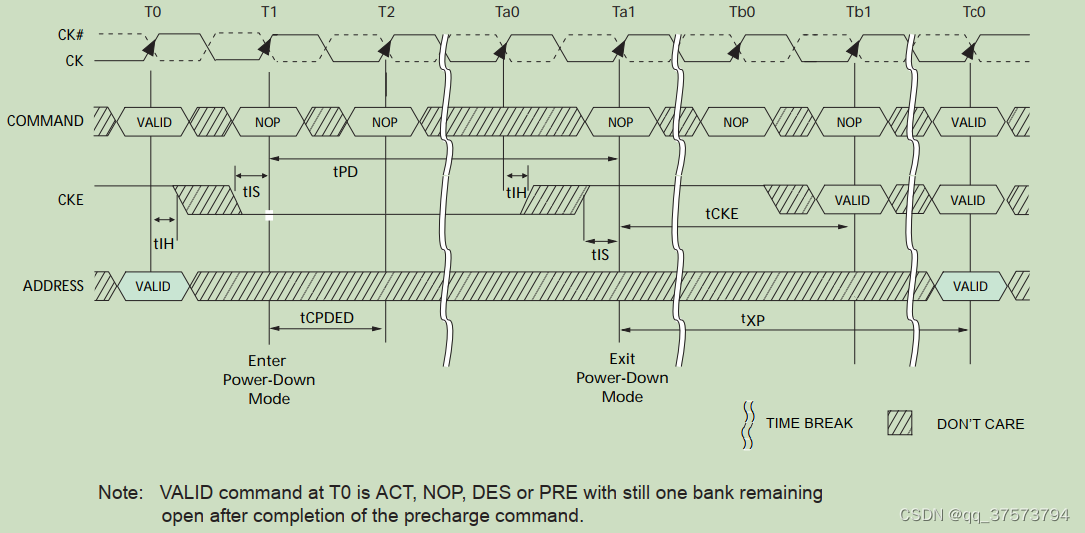

Power Down的进入和退出

- CKE拉低的同时,DDR进入Power-Down状态;

- 如果所有Bank都处于关闭状态,DDR将进入Precharge Power-Down状态;只要有Bank处于激活状态,则进入Active Power-Down状态;

- 在进入Power-Down且为faster Power-Down退出时,DLL必须维持Lock状态,否则在退出Power-Down状态后,DLL必须进行复位操作。

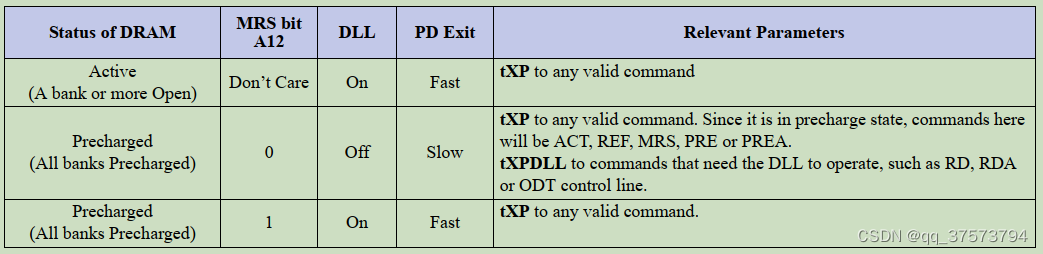

退出Power-Down的时序参数以及对应配置如下:

Power-Down时序及对应参数

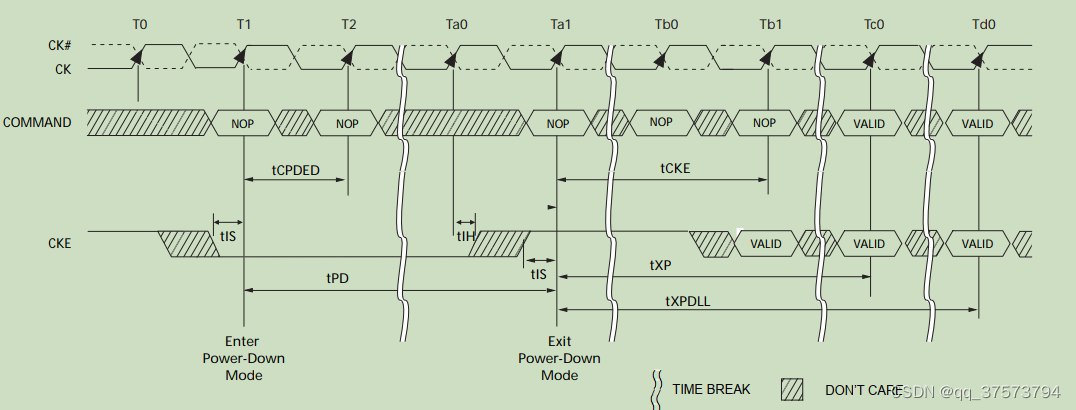

Power-Down进入和退出时序

图中tXP为Fast Exit Mode的退出时序,如配置为Slow Exit Mode需要等待tXPDLL,图示如下:

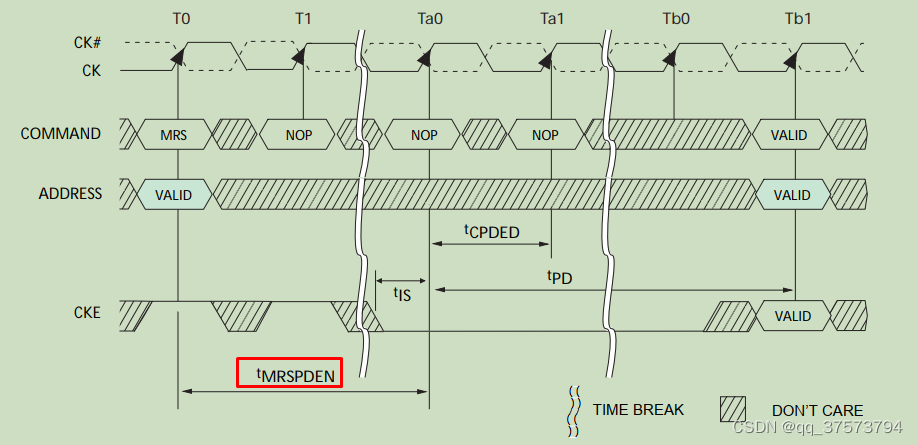

Refresh/Active/Precharge/MRS to Power-Down

几者的区别在于Command to Power-Down的时延要求不一致,下图仅以MRS为例

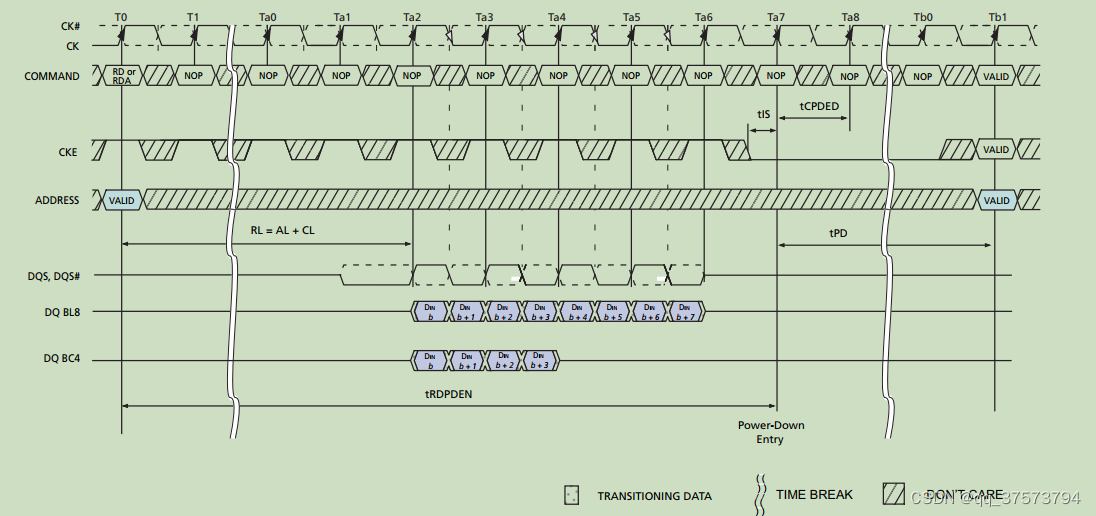

Power-Down after RD&RDA

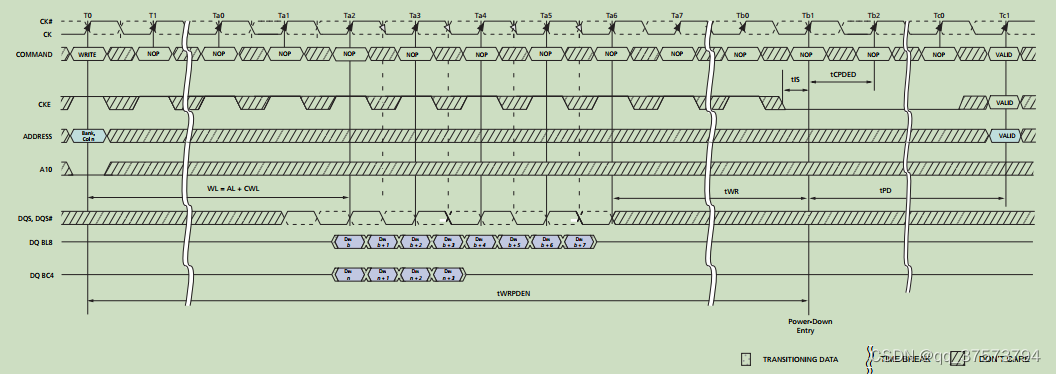

Power-Down after WR

Power-Down after WRA

与WR->Power-Down的时序区别在于tWRAPDEN 和 tWRPDEN(中间的固定值X是对于BL8或者BC4 OTF为4; 对于BC4应为2)

tWRAPDEN = WL+X+WR+1(通过上图也明显看出)

tWRPDEN = WL+X+(tWR/tCK)

对于WR和tWR/tCK这个应该怎么理解? -> tWR根据协议上不同的速率下有不同的最小值要求,WR是根据MR0进行配置得来,两者不相关?

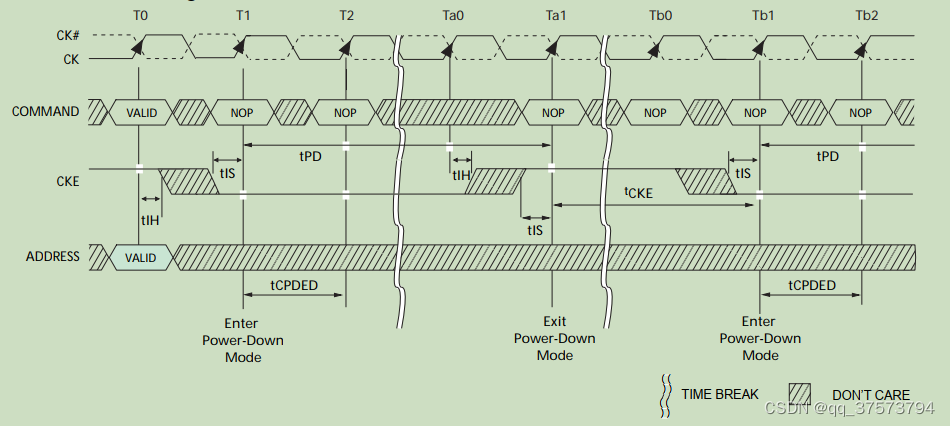

Power-Down Enter-Exit-Enter

相对于前面的power-down时序,需要额外满足tCKE即可

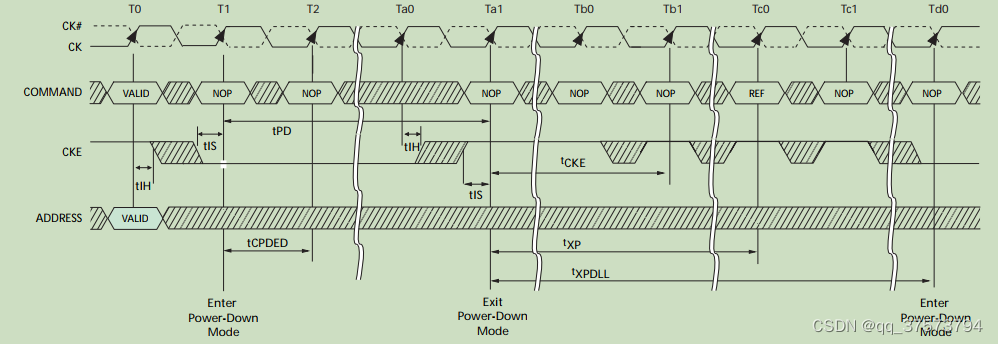

Power-Down Exit-Refresh-Enter

对于Exit Power-Down之后进行Refresh操作,需要保证下一次进入Power-Down时满足DLL lock时序

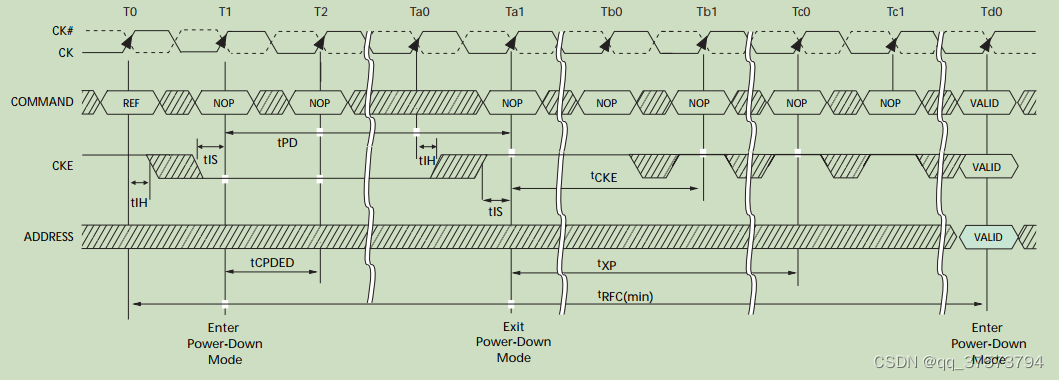

Power-Down Refresh-Enter-Exit-Enter

Power-Down在Refresh之后进入,在正常退出Power-Down满足其时序的同时,也需要满足Refresh到下一个Valid命令的最小延迟tRFC后,再进入Power-Down

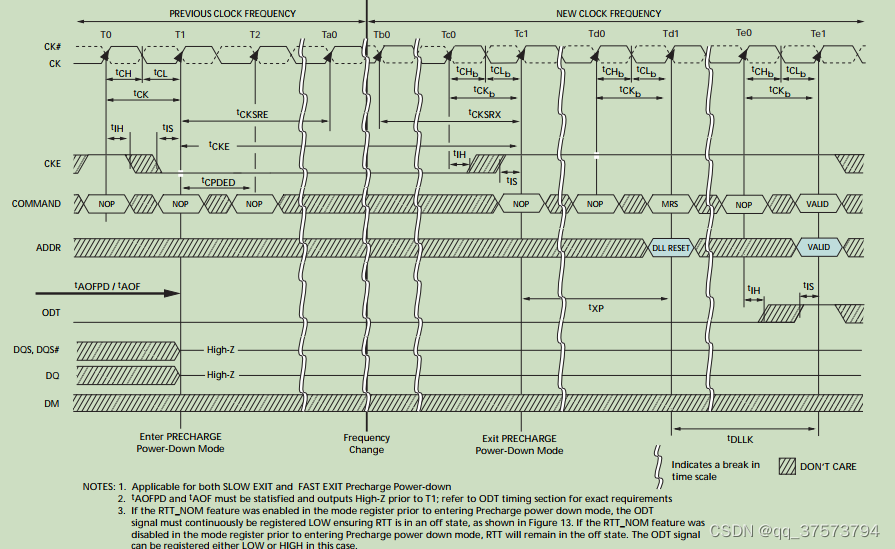

Power Down下切换时钟频率

- 如果RTT_NOM使能,在进入Power Down时,需要将ODT保持为0;如未使能,则可不关注;

- Power Down期间CKE保持为低,输入频率只能在最小与最大支持频率间切换;

- 在退出Power Down状态后,需要通过MRS命令对DLL进行RESET操作;

- 通过MRS命令对WR\CL\CWL进行重新配置,以适配新频率,且此期间CKE必须维持为1;

- 在DLL Re-lock期间,ODT保持为0,CKE保持为1;

DLL

- 上述切换频率中都有提到DLL这个功能,同时在切换时钟的频率只能在约束的最小、最大之间进行。

- 对于这个频率的限制的原因之一就是DLL的存在,因为DLL去做相位的调整和锁定,是有支持的时钟范围在,当DLL off的状态下,DDR时钟可以降到更低的频率来进行处理。

- DLL的切换也是基于Self-Refresh来完成。

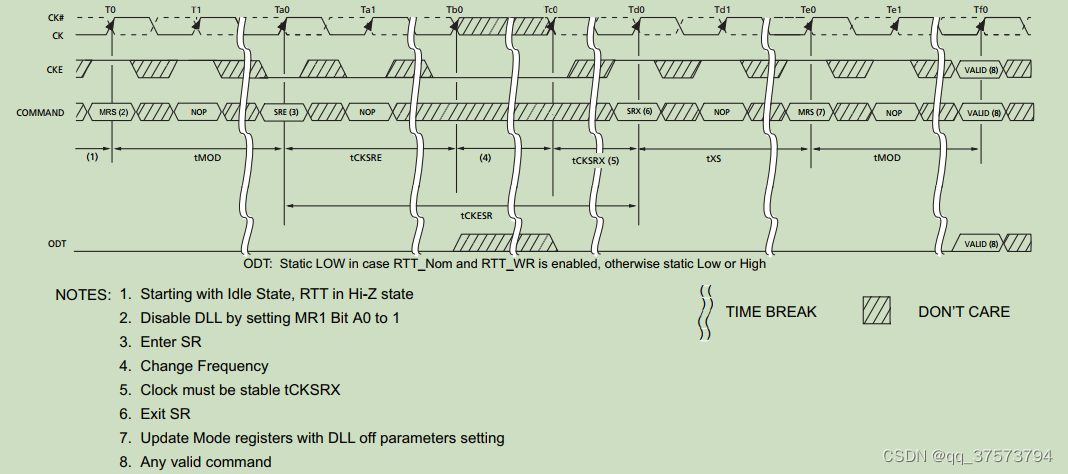

DLL on to off

- DDR进行Precharge且处于Idle状态,ODT维持高阻;

- 发起MRS配置MR1 bit0为1,将DLL disable;

- 等待tMOD时间,发起Self-Refresh(需要满足Self-Refresh对应时序);

- 修改频率,并等待时钟稳定;

- 退出Self-Refresh状态(ODT在使能的情况下,必须维持为0);

- 等待tXS后,发起MRS命令配置对应寄存器。

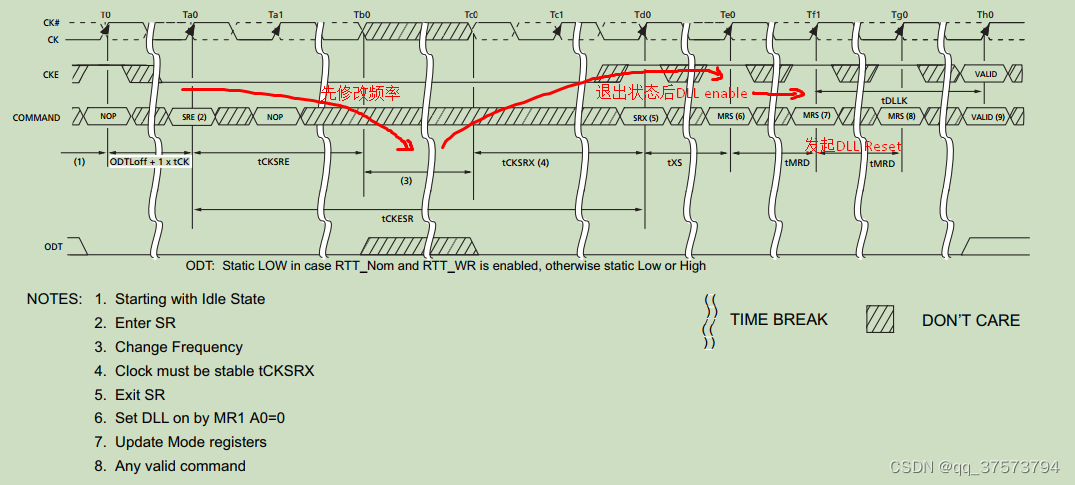

DLL off to on

基本与DLL on->off过程类似,主要区域在于:

- 先修改频率,退出Self-Refresh之后再使能DLL,并进行DLL Reset操作;

- 发起DLL Reset操作后等待至少tDLLK时间,才能进行读写之类需要DLL lock状态的命令。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?