一.实验环境

Vivado HLS 2018.3

Vivado 2018.3

Python

二.HLS实现

2.1缩放比例以及缩放算法

原始图片:1920*1080

处理图片:1080*720

缩放算法:双线性内插方法

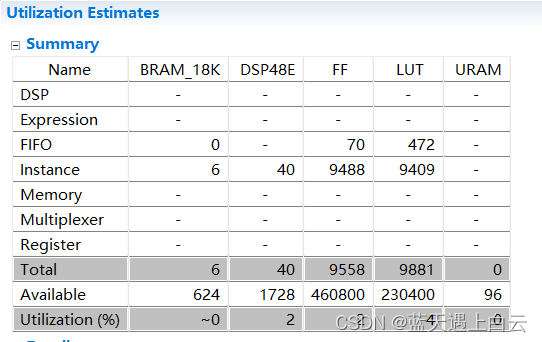

2.2资源评估

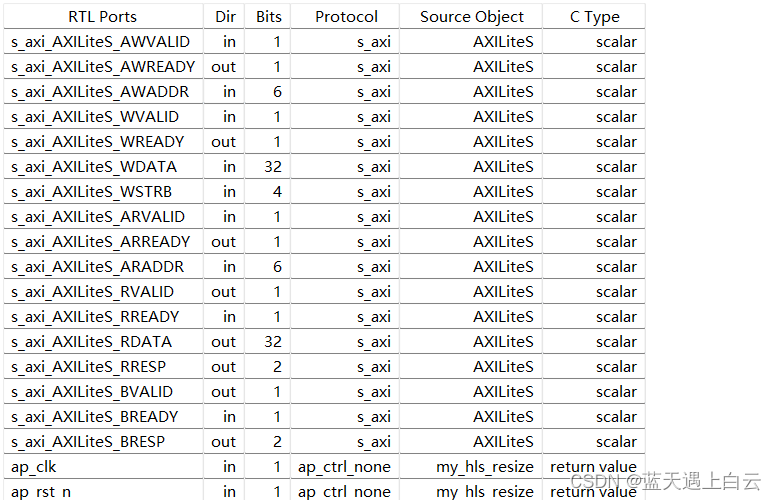

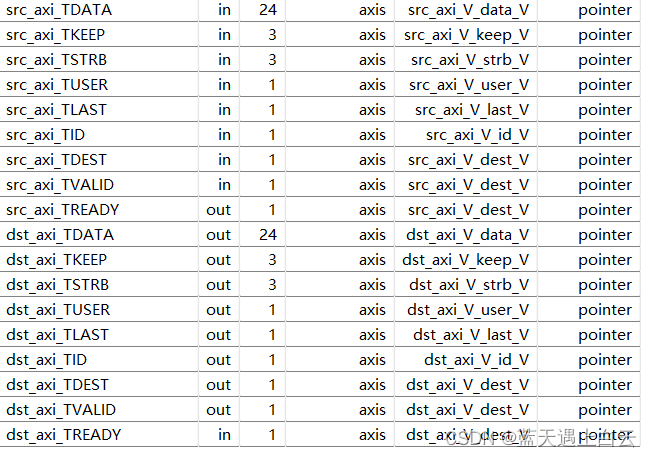

2.3接口类型

1.一路AXI4_LITE接口,用来配置该IP的寄存器

2.两路AXI4 Stream接口,该IP的视频流接口

2.4实现效果

2.5代码实现

2.5.1 top层代码

#include "top.h"

#define HLS_INTER_LINEAR 1

void my_hls_resize(AXI_STREAM& src_axi, AXI_STREAM& dst_axi, int src_rows, int src_cols,int dst_rows,int dst_cols)

{

#pragma HLS INTERFACE axis port=src_axi

#pragma HLS INTERFACE axis port=dst_axi

#pragma HLS INTERFACE ap_ctrl_none port=return

#pragma HLS INTERFACE s_axilite port=src_rows

#pragma HLS INTERFACE s_axilite port=src_cols

#pragma HLS INTERFACE s_axilite port=dst_rows

#pragma HLS INTERFACE s_axilite port=dst_cols

int interpolation;

SRC_IMAGE imag_0(src_rows,src_cols);

DST_IMAGE imag_1(dst_rows, dst_cols);

#pragma HLS dataflow

hls::AXIvideo2Mat(src_axi, imag_0);

hls::Resize(imag_0,imag_1,interpolation=HLS_INTER_LINEAR );

hls::Mat2AXIvideo(imag_1, dst_axi);

}

变换模式可以选择。

2.6问题总结

1.vivado HLS部分电脑可能综合失败,这个由于安装了加密软件导致的

2.vivado HLS2018.3支持HLS VIDEO视频库,vitis2020.1 不再支持hls video 库,转而支持opencv函数库。opencv函数库的环境配置比较麻烦。

3.vivado hls 2018.3生成的IP可以在vivado 2018.3及以上版本通用。也就是可以使用包含有HLS video 视频库的版本所生成的IP直接在高版本的vivado上面使用。

4.vivado 2018.3不能导出IP是因为软件有BUG,此时可以打一个补丁。

三.Python转换

3.1将图片转换为TXT文件

3.1.1代码实现

import cv2 # h, w, c

import numpy

import matplotlib.pyplot as plt

img = cv2.imread("D:/Blog/resize/resize_tb/pic.bmp" , 1)

print("图像的形状,返回一个图像的(行数,列数,通道数):", img.shape)

print("图像的像素数目:", img.size)

print("图像的数据类型:", img.dtype)

#img = cv2.resize(img,(280,280)) 可以改变图片的大小

fname = open("D:/Blog/resize/resize_tb/pic.txt",'w')

# fname.write("图像的形状,返回一个图像的(行数,列数,通道数):"+str(img.shape)+'\n')

# fname.write("图像的像素数目:"+str(img.size)+'\n')

# fname.write("图像的数据类型:"+str(img.dtype)+'\n')

Ylenth = img.shape[1] # 图片列数

Xlenth = img.shape[0] # 图片行数

for i in range(Xlenth):

for j in range(Ylenth):

# fname.write(str(img[i][j][0])+','+str(img[i][j][1])+','+str(img[i][j][2])+'\n')

fname.write(hex(img[i][j][0])[2:]+hex(img[i][j][1])[2:]+hex(img[i][j][2])[2:]+'\n')

# fname.write('\n')

fname.close()

cv2.imshow('image',img)

cv2.waitKey(0)

cv2.destroyAllWindows()

3.1.2实现效果

3.2将TXT文件转换为图片

3.2.1代码实现

# 这是一个文本转图片的python代码

import cv2

import numpy as np

def read_txt(path):

"""

读取txt文件,返回txt_data

"""

with open(path, 'rb') as f:

# 文件在with语句块结束时自动关闭

data = [(int(line.strip(), 16)) for line in f] # strip()用于去除每行末尾的换行符

return data

def list2mat(h,w,c,list_data):#高,宽,通道

img_array = np.zeros((h, w, c), dtype=np.uint8)

for i in range(h):

for j in range(w):

img_array[i, j, 2] = (list_data[i * w + j] & 0x00_00_ff) >> 0 # R

img_array[i, j, 1] = (list_data[i * w + j] & 0x00_ff_00) >> 8 # G

img_array[i, j, 0] = (list_data[i * w + j] & 0xff_00_00) >> 16 # B

return img_array

img_path = "output.jpg" # 400x400

txt_path = "pic.txt"

IMG_W = 1920

IMG_H = 1080

IMG_C = 3

# txt_path = "pic_out1.txt"

# IMG_W = 1080

# IMG_H = 608

# IMG_C = 3

# IMG_W = 512

# IMG_H = 512

# IMG_C = 3

data_list = read_txt(txt_path)

img_array = list2mat(IMG_H, IMG_W, IMG_C, data_list) # txt文件里面,低位为R

cv2.imshow('Image', img_array)

cv2.waitKey(0)

3.2.2实现效果

四.vivado逻辑仿真

4.1testbench平台的搭建

4.1.1例化该IP

4.1.2AXI4_LITE模块配置

4.1.3AXI4模块

4.2配置AXI4-LITE寄存器

HLS生成IP后,里面有一个driver文件夹,里面就是相应的AXI4_LITE寄存器的配置说明了

// ==============================================================

// File generated on Sat Apr 20 14:19:16 +0800 2024

// Vivado(TM) HLS - High-Level Synthesis from C, C++ and SystemC v2018.3 (64-bit)

// SW Build 2405991 on Thu Dec 6 23:38:27 MST 2018

// IP Build 2404404 on Fri Dec 7 01:43:56 MST 2018

// Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

// ==============================================================

// AXILiteS

// 0x00 : reserved

// 0x04 : reserved

// 0x08 : reserved

// 0x0c : reserved

// 0x10 : Data signal of src_rows

// bit 31~0 - src_rows[31:0] (Read/Write)

// 0x14 : reserved

// 0x18 : Data signal of src_cols

// bit 31~0 - src_cols[31:0] (Read/Write)

// 0x1c : reserved

// 0x20 : Data signal of dst_rows

// bit 31~0 - dst_rows[31:0] (Read/Write)

// 0x24 : reserved

// 0x28 : Data signal of dst_cols

// bit 31~0 - dst_cols[31:0] (Read/Write)

// 0x2c : reserved

// (SC = Self Clear, COR = Clear on Read, TOW = Toggle on Write, COH = Clear on Handshake)

#define XMY_HLS_RESIZE_AXILITES_ADDR_SRC_ROWS_DATA 0x10

#define XMY_HLS_RESIZE_AXILITES_BITS_SRC_ROWS_DATA 32

#define XMY_HLS_RESIZE_AXILITES_ADDR_SRC_COLS_DATA 0x18

#define XMY_HLS_RESIZE_AXILITES_BITS_SRC_COLS_DATA 32

#define XMY_HLS_RESIZE_AXILITES_ADDR_DST_ROWS_DATA 0x20

#define XMY_HLS_RESIZE_AXILITES_BITS_DST_ROWS_DATA 32

#define XMY_HLS_RESIZE_AXILITES_ADDR_DST_COLS_DATA 0x28

#define XMY_HLS_RESIZE_AXILITES_BITS_DST_COLS_DATA 32

4.3读取文本操作

reg [23:0] img [0:2073599];//根据自己图片大小

initial begin

$readmemh("D:/Blog/resize/resize_tb/pic.txt",img);

end4.4仿真数据写入TXT

integer file_out;

initial file_out = $fopen("D:/Blog/resize/resize_tb/pic_out.txt","w");

always@(posedge clk) begin

if(dst_axi_TVALID)

$fwrite(file_out,"%h\n",dst_axi_TDATA);

end

6911

6911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?